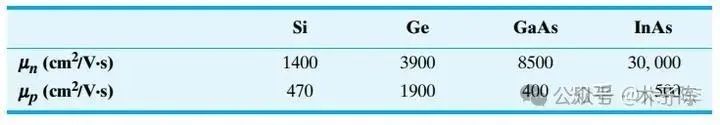

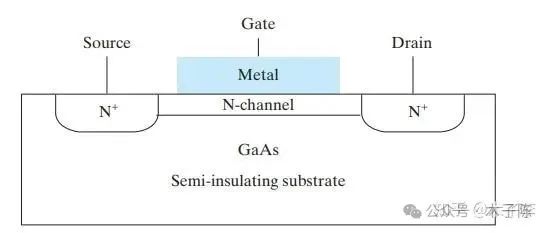

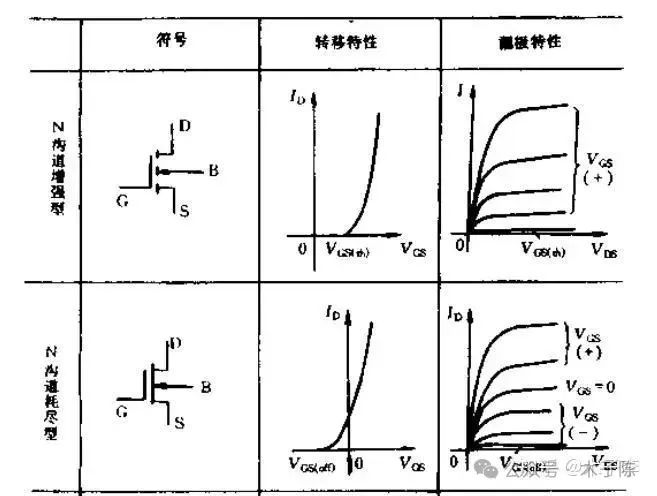

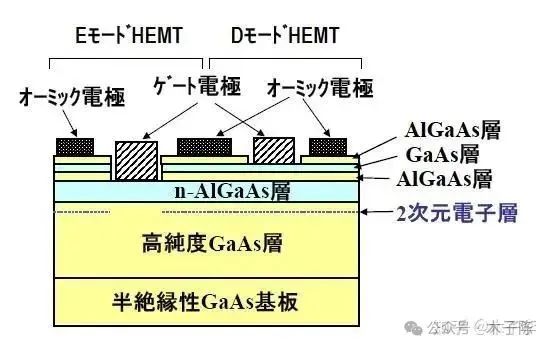

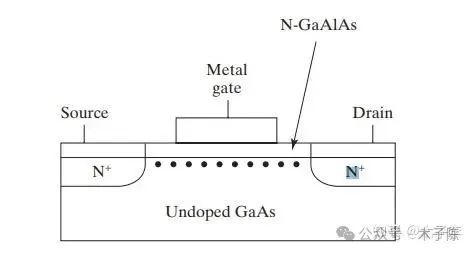

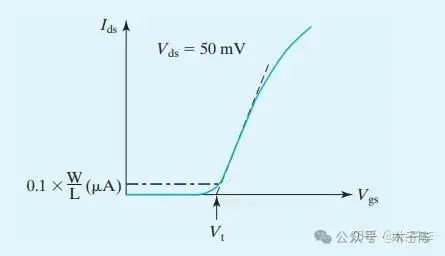

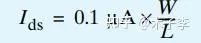

今天不讨论mosfet,讨论一下其他类型的半导体器件。1. GaAs MESFET 相比较一般mosfet, GaAs器件有着更高的载流子迁移率,这使得载流子移动更快,器件也拥有更快的速度,这为微波通信领域提供了新的选择。 The most obvious way to improve speed is to use a semiconductor having higher mobility than silicon such as germanium, Ge or strained Si . 最显著的提高器件速度的方法是使用比硅更高迁移率的半导体,如Ge, 应变Si, 通过外延工艺,在硅衬底上可以生长单晶Ge和SiGe合金 ,这对于提高器件速度大有裨益。 下表展示了不同半导体材料在室温下电子和空穴的迁移速率  从表中可知,GaAs和一些化合物半导体的电子迁移率( electron mobilities)比Si高。对于某些应用场景,只需要用到N-Channel 的FETs,故电子迁移率的重要性超过了空穴迁移率。但是,由于这些材料在semiconductor/dielectric interface中会形成大量的charge traps ,导致对于MOSFET的应用来说,如何在提高电子迁移率的基础上制备出高质量的mos transistors成为挑战。 Fortunately, a Schottky junction can serve as the control gate of a GaAs FET in place of an MOS gate 利用肖特基节代替MOS 栅极作为GaAs场效应管的控制栅极,The device, called MESFET for metal–semiconductor fieldeffect transistor  由于GaAs具有高的Eg和低的ni ,故未掺杂的GaAs具有很高的电阻率,可以被看做是绝缘体。而使用金属Gate,例如Au则会造成一个大的肖特基势垒高度,从而最小化输入栅极电流,即肖特基二极管电流 工作原理: 当Gate上加一个反向偏置电压或者正向小电压(维持gate diode 电流),栅极下的耗尽区会展宽或收紧,这便调节了导电的通路的厚度,即未耗尽的部分,同时影响了Ids, 由于Ids不存在在表面反型层中流动,因此电子的迁移率不会因为表面的散射而降低,这进一步增强了GaAs MESFET的速度优势。 depletion-mode transistor耗尽型晶体管:当N-channel的沟道厚度大于Vg=0时的耗尽层宽度,则MESFET在Vg=0时导通,且需要反向偏置电压将其关断。 enhancement-mode transistor增强型晶体管: 当N-channel的沟道厚度小于Vg=0时的耗尽层宽度,则MESFET在Vg=0是关断,且需要正向偏置电压将其导通。  Si基CMOS电路设计中常用增强型晶体管,GaAs FET中两种模式都会用到,但耗尽型更容易制造。 2. HEMT HEMT 又称 high electron-mobility transistor, MODFET for modulationdoped FET(调制掺杂FET的MODFET)用于微波通信,卫星电视接收器等。高电子迁移率晶体管(英语:High electron mobility transistor, HEMT),也称调制掺杂场效应管(modulation-doped FET, MODFET)是场效应晶体管的一种,它使用两种具有不同能隙的材料形成异质结,为载流子提供沟道,而不像金属氧化物半导体场效应管那样,直接使用掺杂的半导体而不是结来形成导电沟道。砷化镓、砷镓铝三元化合物半导体是构成这种器件的可选材料,当然根据具体的应用场合,可以有其他多种组合。例如,含铟的器件普遍表现出更好的高频性能,而近年来发展的氮化镓高电子迁移率晶体管则凭借其良好的高频特性吸引了大量关注。高电子迁移率晶体管可以在极高频下工作,因此在移动电话、卫星电视和雷达中应用广泛。  HEMT的提出:由于前面说到,掺杂会导致电子传导过程中散射 ,反射的增加而降低电子迁移率,因此如果Channel不掺杂,则电子迁移率会提高。故如图所示,在不掺杂的Channel上生长一层N-GaAlAs薄膜,可制成类MOS结构。  如图,gate下方的GaAlAs 薄膜处于耗尽状态,且GaAlAs比GaAs有着更高的带隙,其宽禁带导致其功能类似于MOSFET中的氧化层。在未掺杂GaAs和GaAlAs的界面出现energy well和薄层可导电电子。  图中,GaAlAs能带的向上弯曲是由于掺杂Al离子的存在,类似于PN结中的耗尽层。由于沟道中的带脑子来源于N+ Source, EF为N+source的费米能级,其与导带Ec共同决定了channel中的电子浓度。由于这两种半导体材料的外延界面比Si-SiO2光滑,故不会出现由于表面散射而导致迁移率下降的情况。 3.JFET 如果将Gate与衬底之间的肖特基结替换为P+N结,则成为JFET或者结场效应晶体管。P型掺杂的Gate连接到一个金属的电路,在MESFET中,反向偏压会使耗尽层展宽并收缩传导通道,这样可以通过栅极电压来控制JEFT电流。在MOSFET出现之前,集成电路多采用双极型晶体管bipolar transistors,在输入端有正偏二极管并产生显著的输入电流。但对于某些电路来说,高输入电流和大的电容是不可以接收到的,JEFT由于反向偏置的二极管的存在, 提供了一个低电容和低输入电流的器件,同时JFET可以用双极型晶体管制造,并在同一集成电路芯片中共存。 如何测量MSFET的Vt Vt 很少从CV的关系中读出,一般通过Ids-Vgs图中读出:  Vt可以通过外推Ids vs. Vgs曲线到Ids = 0来测量。 也可以定义为Vgs,其中id是一个很小的固定值。 在一个很小的Vds下,如50mv, 做Ids-Vgs图。如果Uns是常数,则在Vgs>Vt时,Ids随着(Vgs-Vt)的变化线性增加。但由于Uns随Vgs的增加而减小,所以曲线是亚线性的。其通常做法是在曲线最大斜率点外推,并取得与X轴的截距为Vt. 另一种测量方法是将Vt定义为Vgs,其中Ids是个小电压,公式如下图所示:  |