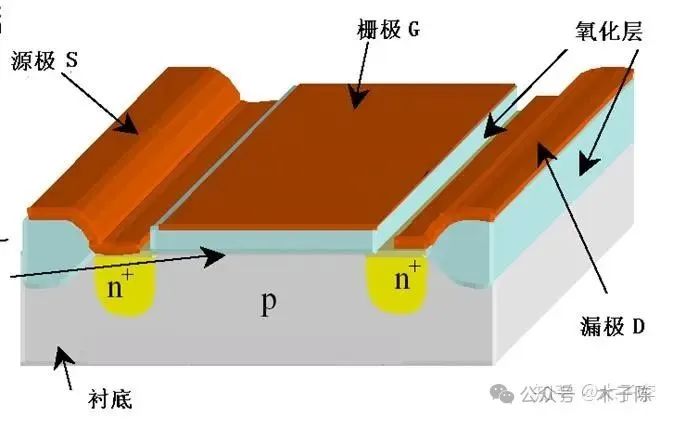

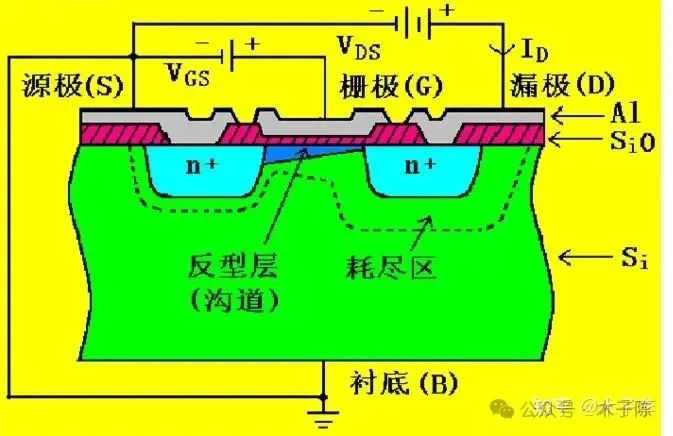

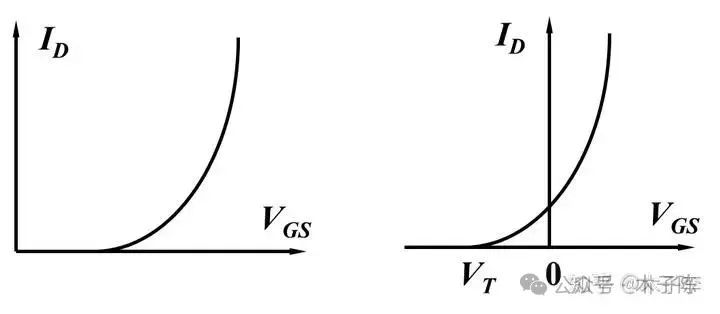

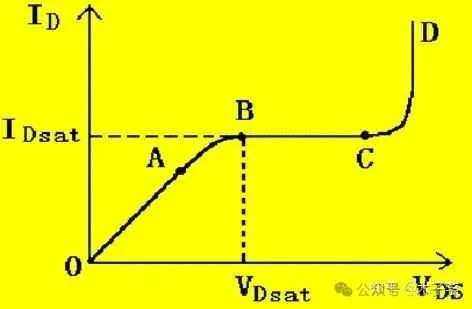

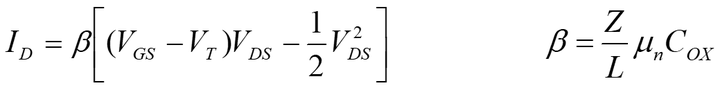

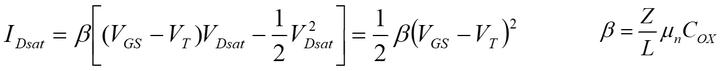

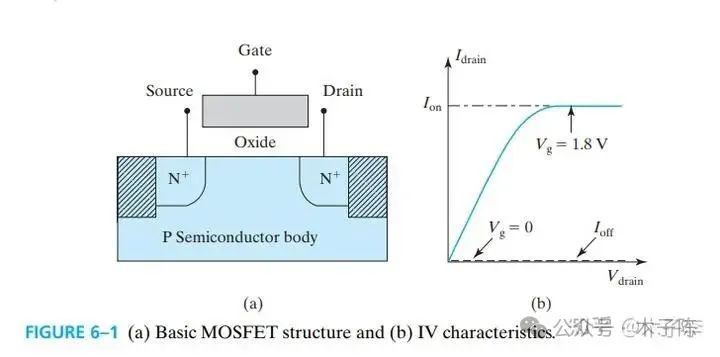

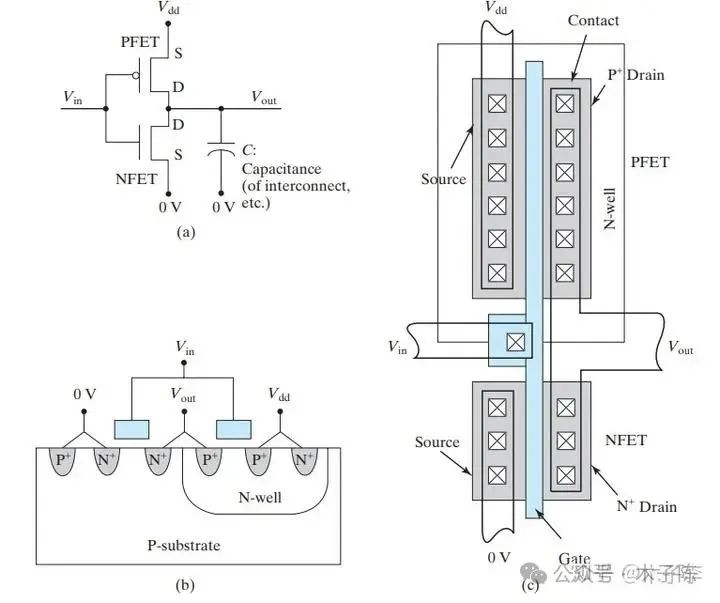

· MOSFET结构和工作原理1.MOSFET的结构   VGS来控制沟道的导电性,从而控制漏极电流 ID ,是一种电压控制型器件. · 2.MOSFET的工作原理 当 VGS<VT(称为阈值电压)时,源漏之间隔着P区,漏结反偏,故无漏极电流.当VGS >VT 时,栅下的P型硅表面发生强反型,形成连通源区和漏区的N型沟道,产生漏极电流ID. 对于恒定VDS ,VGS越大,则沟道中的可移动电子就越多,沟道电阻就越小,ID 就越大. · MOSFET的特性 N 沟 MOSFET当: VT >0时,称为增强型,为常关型.零栅压时无导电沟道. VT <0时,称为耗尽型,为常开型.零栅压时有导电沟道. 转移特性曲线:  输出特性曲线:  ① 线性区 当VDS 很小时,沟道就像一个其阻值与VDS 无关的固定电阻,这时ID 与VDS 成线性关系,如图中的OA段所示.  ② 过渡区 随着VDS 的增大,漏附近的沟道变薄,沟道电阻增大,曲线逐渐下弯.当VDS增大到VDsat饱和漏源电压时,漏处的可动电子消失,这称为沟道被夹断,如图中的AB 段所示. ③ 饱和区 当VDS >VD sat 后,沟道夹断点左移,漏附近只剩下耗尽区.这时ID 几乎与VDS 无关而保持常数ID sat,曲线为水平直线,如图中BC段所示.  ④ 击穿区 当VDS 继续增大到BVDS 时,漏结发生雪崩击穿,或者漏源间发生穿通,ID 急剧增大,如图中CD段所示. · 3. MOS的电容  晶体管的基本结构如图6-1所示,两个PN结为Source和Drain,用来提供电子或空穴。场效应晶体管(field-effect transistor )FET 是指Gate 通过栅氧电场来控制反型层((inversion layer),从而控制管子导通或者关断。6-1(b)显示了mosfet的IV特性,当Vg=0时,只有很小的关断的漏电流Ioff,随着Vg的增大,导通电流会增加到Ion.  (a)为NMOS, N-channel MOSFET, or N-MOSFET or simply NFET. 如图b所示是其导通的状态,Body和Source接0V,当Vg=Vdd,由于反型层的出现,NFET turn on . 同样对P管来说B和S接Vdd时,当Vg=0时,PMOS导通。 When Vg = Vdd, the NFET is on and the PFET is off. When Vg = 0, the PFET is on and the NFET is off 正是由于NMOS和PMOS的互补性,使得cmos成为低功耗电路的宠儿。  如上图(a)所示,这是一个inverter,其中PMOS为上拉管,NMOS为下拉管。在Vg电压的控制下,使负载电容C对输出节点充放电,以达到Vdd或者0的效果。具体工作流程如下 1.当Vg=Vdd,NMOS开启而PMOS关闭,输出低阻连接到GND,则输出低电平0, 2.当Vg=0,PMOS开启而NMOS关闭,输出低阻连接到VDD,则输出高电平1 3.在任何一种静态情况下,NMOS和PMOS均关闭,没有电流从Vdd通过两个晶体管流到GND,故功耗减小。 |