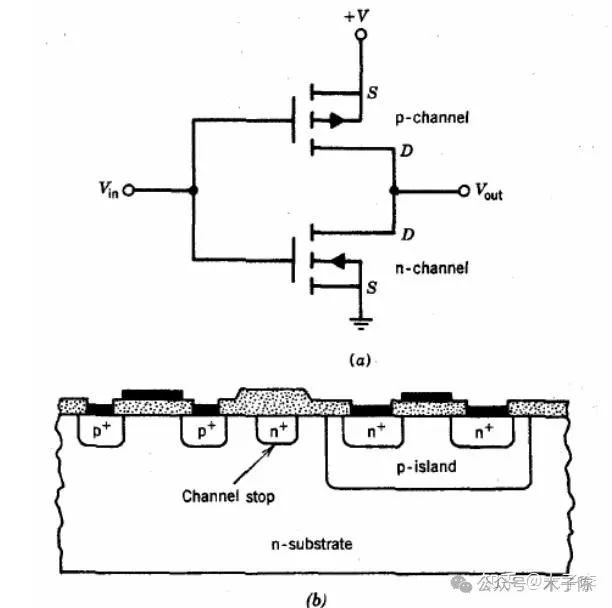

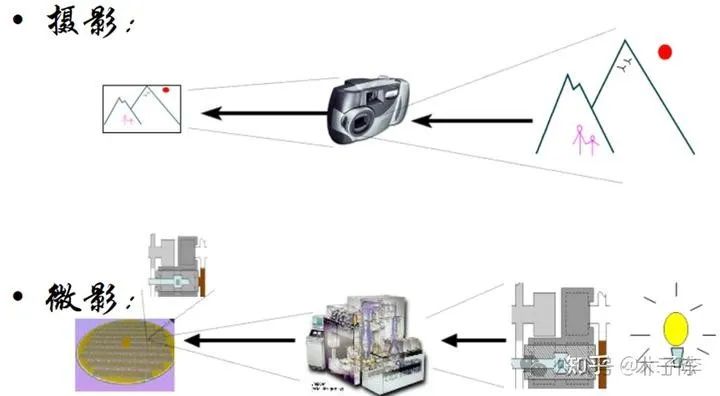

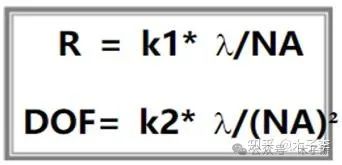

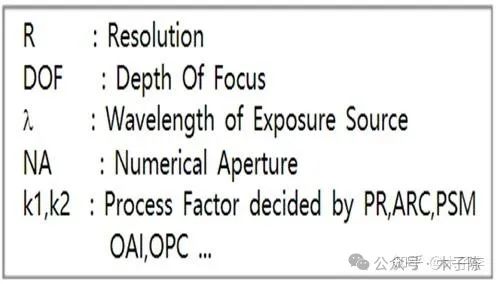

半导体工艺制程技术由双极型工艺,发展至PMOS工艺技术,NMOS工艺技术,但都存在功耗的问题,最后进化到低功耗的CMOS技术,而CMOS技术变成现在工艺主流,但随着应用环境的发展,又进化BICMOS, BCD , HV-CMOS工艺。CMOS 就是将NMOS和PMOS制造在同一个芯片上组成电路,利用互补对称电路来配置连接PMOS,NMOS,组成逻辑电路,其电路静态功耗为0。CMOS工艺组成的反相器,只有在低电平(VSS),高电平(VDD)相互转换的瞬间才会同时2导通NMOS和PMOS,在VDD和VSS之间产生电流,产生功耗,其静态功耗为0.  离子束光刻 离子束光刻CMOS集成电路制造工艺主要有以下几步: 1.图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到半导体单晶片上 2.掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等 3.制膜:制作各种材料的薄膜. 一 . 光刻其中,图形转化需要用到的技术,就是光刻技术:n光刻工艺是半导体制造中最为重要的工艺步骤之一。主要作用是将掩膜板上的图形复制到硅片上,为下一步进行刻蚀或者离子注入工序做好准备。  1)光刻理论· 瑞利(Rayleigh)公式   2) 光刻三要素光刻胶、掩膜版和光刻机光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。 光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。

|