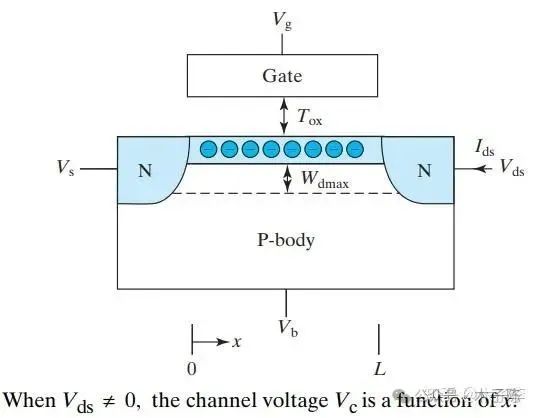

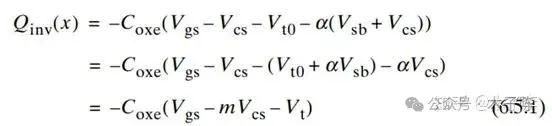

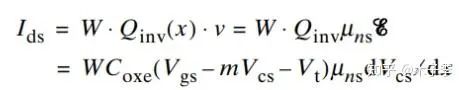

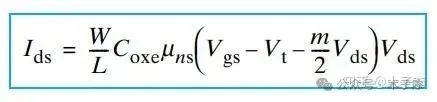

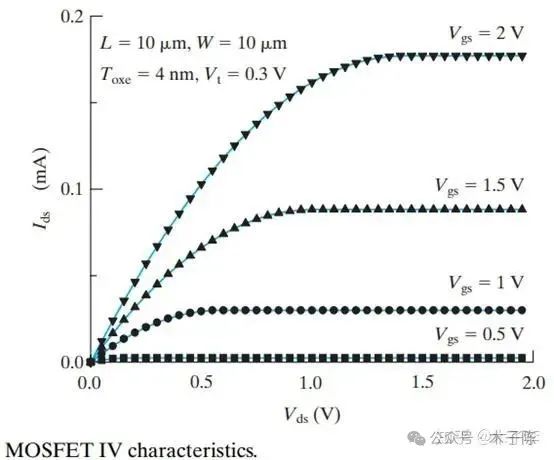

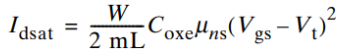

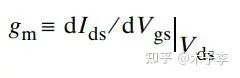

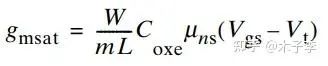

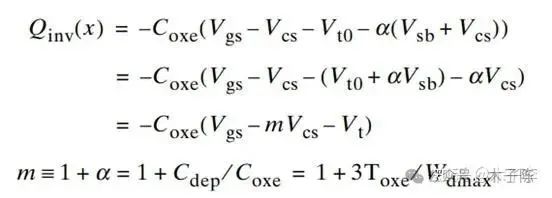

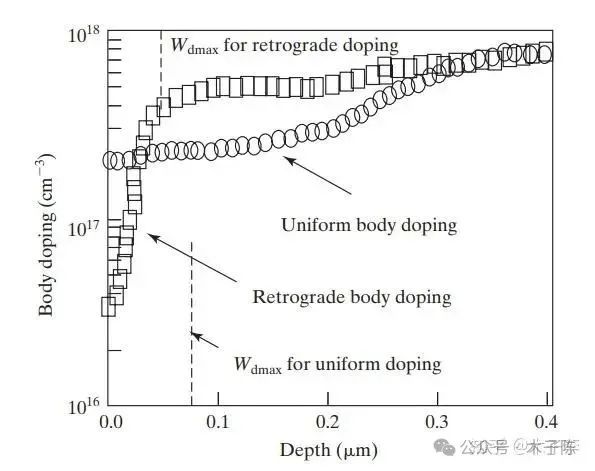

MOSFET(金属-氧化物-半导体场效应晶体管)是一种基本的半导体器件,它由源极(source)、栅极(gate)、漏极(drain)和体区(body或substrate)组成。MOSFET的电流-电压特性可以通过不同的模型来描述,这些模型考虑了器件的工作模式,包括截止区、线性区(也称可变电阻区)和饱和区(也称活跃区)。 MOSFET的基本IV特性 1. 截止区(Cut-off or Off-State): 当栅极电压相对于源极低于阈值电压时,沟道关闭,没有电流流过器件。 2. 线性区(Linear or Ohmic Region): 在此区域内,漏极电流与漏极电压成正比。这意味着器件表现出类似电阻的行为。 3. 饱和区(Saturation or Active Region): 随着 Vds增加到一定点后,漏极电流Id不再随Vds的变化而变化,而是主要受栅极电压Vgs控制。 MOS基础IV模型  利用反型电荷来理解Id可以得出其是由高电压流向低电压的,经过推导可以得出  从式中可以看出,Ids与W(channel宽度),uns(迁移率),Vds/L (S/D在channel内平均场强),和Cox(Vg−Vt−mVds/2)成正比,可以理解为channel内平均Qinv  当Vds很小时,mVds/2项可以忽略不计,Ids∝Vds,即晶体管表现为电阻。随着Vds的增加,平均Qinv减少,同时dIds/dVds减少,对上述式子求导可以看出在某一Vds处,dIds/dVds=0  Vdsat为漏极饱和电压,超过该电压漏极电流达到饱和,不同的Vg对应不同的Vdsat 当Vds << Vdsat,称为线性区,也叫欧姆区,Vds >Vdsat为饱和区,也叫有源区。 将Vds=Vdsat带入电流计算公式,可以得到饱和电流  当Vd=Vdsat后,Ids保持不变,其原因可以用反型电荷来解释,当Qinv在沟道的D端,当Vd=Vdsat后,反型电荷等于0 ,这种现象被称为channel pinch off.但这种夹断不会对电流流动造成影响,类似于耗尽层,电流可以流过PN结的耗尽区,同样当电子到达MOS的截断区时,会造成电位下降而不会影响电流流动 这就引出另一个概念,跨导gm,是衡量晶体管对输入电压的灵敏度   MOS管中有个很重要的概念就是Qinv, 即反型层电荷。 •当Vd >Vs ,沟道电压Vc是关于X的函数,在x = 0时Vc = Vs,在x = L时Vc = Vd,在channel中间,Vc>Vs, 但在源端,Vc=Vs,这是由于channel中部的Vc高于Vc(x), 这是由于氧化层和 耗尽层电容更少的分压导致的,因此反型层上的电荷数较少,具体来说,式中的Vgs项应替换为Vgc(x)或Vgs−Vcs(x), Vsb替换为Vsb + Vcs(x)。  M通常在1.2左右。一开始,简单地假设m = 1是可以接受的,也更容易。然而,在方程中加入m可以显著提高其准确性,以供以后参考。Body通常被称为背栅,由于它对channel 电荷有着微弱但类似门效应的影响,其在电荷上的表现被称为bulk charge effect . m 也被称为bulk charge factor. 体电荷效应(bulk-charge effect)是与半导体器件,特别是MOSFETs相关的现象。在MOSFET中,"bulk"指的是衬底材料,即形成晶体管的半导体基材。体电荷效应主要是指由于衬底内的电荷变化导致的MOSFET行为的变化。 体电荷效应的主要方面包括: 1.背栅效应 (Back-Gate Effect):当MOSFET的源极和漏极相对于衬底施加电压时,这个电压不仅影响到沟道区,还会影响到整个衬底区域。如果衬底没有正确地接参考电位(通常是接地),那么源极-衬底或漏极-衬底之间的电压差会在衬底内产生额外的电场。这可能会改变MOSFET的有效阈值电压,并且可能引起不必要的电流流动,从而影响电路性能。  2.衬底偏置效应 (Substrate Bias Effect):通过给衬底施加一个正向或反向偏压,可以改变MOSFET的工作特性。例如,在n型MOSFET中,如果衬底被负偏置,则会增加电子从源极到漏极的移动难度,从而提高阈值电压;反之,若衬底为正偏置,则会使阈值电压降低,更容易导通。这种效应可以通过适当设计来利用,以优化某些特定应用中的性能。 3.寄生双极效应 (Parasitic Bipolar Effect):在高电压或快速切换条件下,MOSFET内部可能存在由p-n结形成的寄生双极晶体管结构。当这些结构被激活时(如因过高的源极/漏极与衬底间的电压差),它们可能导致非预期的大电流流动,严重时甚至会引起设备损坏。这种情况通常发生在高压LDMOS等类型的功率MOSFET上。 4.体电荷调制 (Bulk Charge Modulation):对于一些高级工艺节点下的MOSFET来说,特别是在超薄氧化层和短沟道长度的情况下,衬底中的自由载流子浓度变化能够显著影响沟道电导率。这种情况下,即使是微小的衬底电压波动也可能对MOSFET的行为产生较大影响。 |