[测试工程] 什么是ATE测试? 日期:2025-11-20 08:03:35 点击:273 好评:2

[测试工程] 什么是ATE测试? 日期:2025-11-20 08:03:35 点击:273 好评:2

ATE测试工程师(Automatic Test Equipment Testing Engineer)在集成电路(IC)制造过程中扮演着至关重要的角色,主要负责利用自动化测试设备(ATE)对芯片进行测试,以确保产品的功能、性能和...

[测试工程] 芯片ATE测试综述 日期:2025-11-19 20:37:16 点击:394 好评:2

[测试工程] 芯片ATE测试综述 日期:2025-11-19 20:37:16 点击:394 好评:2

一、引言 ATE(Automatic Test Equipment),即自动测试设备,在电子元器件、尤其是半导体芯片的生产制造流程中扮演着不可或缺的关键角色。随着现代芯片集成度的不断提高以及功能的日益...

[测试工程] 半导体芯片测试知识 日期:2025-11-19 18:23:00 点击:231 好评:0

[测试工程] 半导体芯片测试知识 日期:2025-11-19 18:23:00 点击:231 好评:0

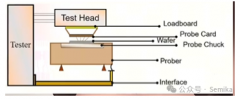

半导体芯片测试知识 半导体芯片测试是确保芯片质量和可靠性的关键环节,贯穿芯片制造的全过程。以下是关于半导体芯片测试的核心知识点: 1.测试类型与目的 晶圆测试(CP测试):...

[可靠性测试] 一篇讲透:芯片可靠性测试到底测什么? 日期:2025-11-18 21:38:00 点击:236 好评:0

[可靠性测试] 一篇讲透:芯片可靠性测试到底测什么? 日期:2025-11-18 21:38:00 点击:236 好评:0

芯片为啥能用好几年?揭秘背后的压力测试 在半导体产业链中,芯片从设计、制造到封装,每一步都至关重要。然而,即便芯片功能测试全部通过,也不能保证其在 真实应用场景中长...

[测试工程] 一文介绍半导体芯片各类测试 日期:2025-11-15 20:10:00 点击:240 好评:0

[测试工程] 一文介绍半导体芯片各类测试 日期:2025-11-15 20:10:00 点击:240 好评:0

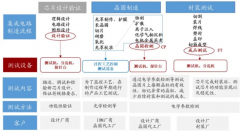

半导体芯片测试是指对芯片在制造和封装环节进行的,为检查其电气特性、功能和性能等进行的验证,目的是判断其是否符合设计要求。 集成电路测试分为三部分,包括 芯片设计验证...

[测试工程] 超全的芯片测试原理讲解 日期:2025-11-15 19:45:00 点击:292 好评:0

[测试工程] 超全的芯片测试原理讲解 日期:2025-11-15 19:45:00 点击:292 好评:0

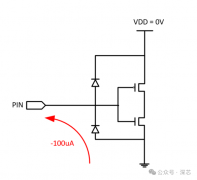

做芯片测试的同学经常会涉及到Continuity测试、Leakage测试、GPIO drive capability测试、GPIO pullup/pulldown resistor测试、standby idd、run idd、IDDQ、MBIST、SCAN等测试,小编在此带大家总结一下这些测...

[测试工程] IC封装测试流程(PPT) 日期:2025-11-15 09:31:00 点击:232 好评:0

[测试工程] IC封装测试流程(PPT) 日期:2025-11-15 09:31:00 点击:232 好评:0

虽然只是讲TSOP的,但对于了解封装来讲还是普遍适用的。...

[测试工程] 芯片封装测试流程详解,具体到每一个步骤 日期:2025-11-15 08:49:15 点击:84 好评:0

[测试工程] 芯片封装测试流程详解,具体到每一个步骤 日期:2025-11-15 08:49:15 点击:84 好评:0

封装测试是将生产出来的合格晶圆进行切割、焊线、塑封,使芯片电路与外部器件实现电气连接,为芯片提供机械物理保护,并利用测试工具,对封装完的芯片进行功能和性能测试。...

[测试工程] 技术前沿——半导体封测 日期:2025-11-12 22:40:52 点击:196 好评:0

[测试工程] 技术前沿——半导体封测 日期:2025-11-12 22:40:52 点击:196 好评:0

半导体生产流程由晶圆制造、晶圆测试、芯片封装和封装后测试组成。半导体封测是指将通过测试的晶圆按照产品型号及功能需求加工得到独立芯片的过程。 封装过程为: 来自晶圆前...

[测试工程] 一文详解芯片测试 日期:2025-11-12 21:24:00 点击:265 好评:0

[测试工程] 一文详解芯片测试 日期:2025-11-12 21:24:00 点击:265 好评:0

本文就芯片测试做一个详细介绍 。 芯片的测试大致可以分成两大部分。CP(chip probering)和FT(final test)。某些芯片还会进行SLT(system leve test)。还有一些特定要求的芯片,需要一些可靠性...