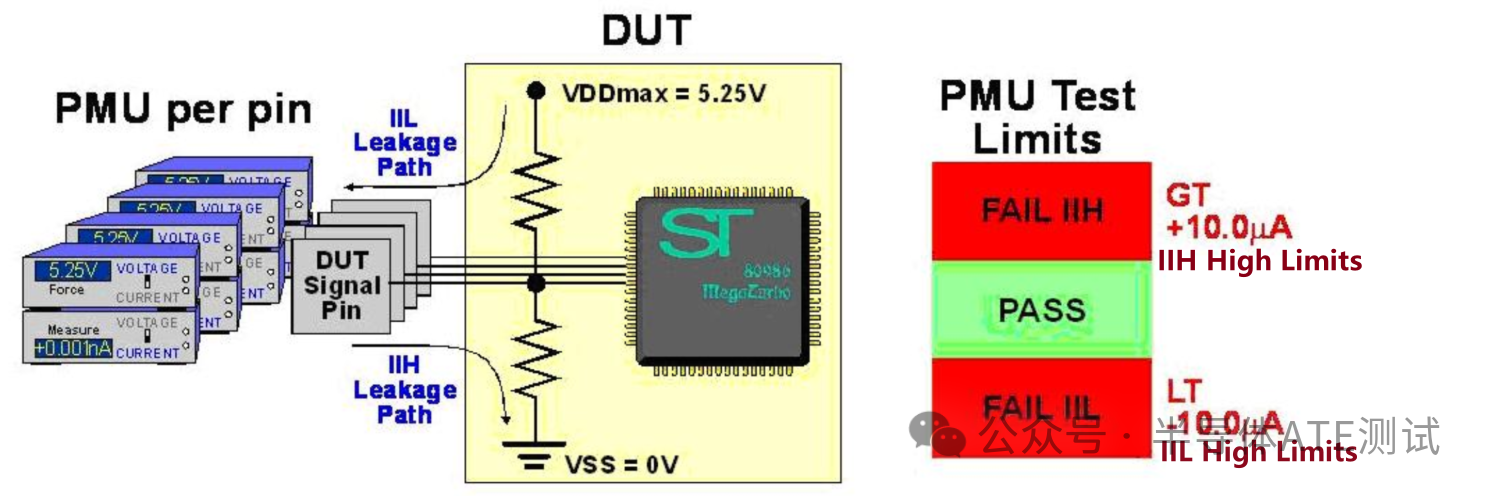

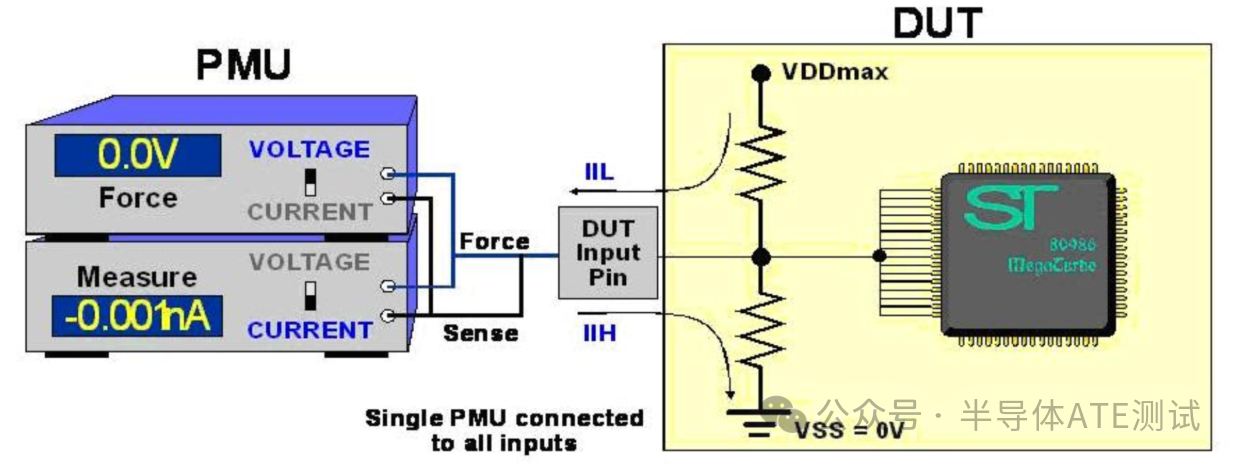

书接上文,IIH/IIL 除串行测试(需 ATE 具备 PerPin PMU 结构)外,IIH/IIL 测试还可采用更节省时间的并行测试方式。如需进一步压缩测试时间,可基于 DUT 的 I/O 结构考虑实施集群测试。1. IIH/IIL 并行测试 我们可以利用拥有PerPin PMU 结构的测试机,实现对DUT I/O 并行漏电流测试,即:对DUT 所有待测输入管脚同时且独立的施加电压并进行电流测量--提供 VDDmax 给所有Power Pin, 驱动逻辑0 给所有待测输入管脚,同时测量其输出电流(IIH); 驱动逻辑1 给所有待测输入管脚,同时测量其输出电流(IIL),测试结果与程序中设定的testLimit 比较并判断测试结果通过与否。  Step1. 按照I/O spec 提供VDDmax给Power Pin Step2. Run Pre-conditionpattern 将DUT所有I/O脚置于输入逻辑0状态 Step3. 利用ATE PerPin PMU 资源force VDDmax 给DUT所有待测I/O 脚 Step4. 等待5~10ms(PPMU-> BADC 电流测量delay) Step5. 测量当前待测I/O电流(方向:流入DUT,正电流) Step6. 若测量电流在Limit 范围内则Pass,反之Fail Step7. Run Pre-conditionpattern 将DUT所有I/O脚置于输入逻辑1状态 Step8. 利用ATE PerPin PMU 资源force 0V 给DUT所有待测I/O 脚 Step9. 等待5~10ms(PPMU-> BADC 电流测量delay) Step10. 测量当前待测I/O电流(方向:流出DUT,负电流) Step11. 若测量电流在Limit 范围内则Pass,反之Fail 2.IIH/IIL 集群测试 当测试外围硬件可实现单个ATE PMU资源可同时连接DUT 所有待测I/O时,我们可对DUT进行IIH/IIL的集群测试。  需注意的是: ①集群测试法的测试Limit 为所有待测引脚Spec Limit 之和,若需确定某个I/O channel 具体的漏电流值,需采用串行/并行测试方式。 ②集群测试需在测试负载板上增加额外的Relay,以确保同一硬件资源可同时对该Group channel进行Vforce Imeas 动作 ③集群测试可降低对测试系统PerPin PMU的需求,且可以节省测试时间。 ④因CMOS器件有较大的I/O 输入阻抗,集群测试仅可实现对CMOS 器件的测量,而无法完成对有特定低阻抗输入管脚,外接上拉,下拉电阻 I/O channel的同组测量。 ⑤由④可知,若选用集群测试实现IIH/IIL 测量,可根据DUT I/O channel 输入结构,将其分为不同的Group(CMOS I/O group, 低阻I/O group, 上拉I/O group, 下拉I/O group),对各Group 分别进行集群测量,并按其I/O Spec特性进行测试Limit 卡控。 ⑥实际测试时,可采用集群测试+并行测试/串行测试的方式进行IIH/IIL测量,以在确保测试质量的前提下,尽量减少测试硬件资源依赖,reduce 测试时间。 3.Trouble Shooting 1. IIH/IIL 电流方向正确,测量值在Limit 范围内,且测量数据符合具有集群效应,测试Pass --不用debug 2. IIH/IIL 实测值稍微超过所设Limit,测试不通过-- 测量结果在程序中所设Irange 范围内,未达到Iclamp 所设数值。 3. IIH/IIL 实测值远超测试Limit 所定义的上下限,测试不通过 --测量结果大于程序中设定的Irange 值,约等于程序所设Iclamp 值。 对于情况1,不用debug 情况2 & 3 出现时,debug 步骤如下: Step1. 确认当前硬件 Open Socket 测试结果,若未进行Open Socket 测试则将DUT 从Socket上拿走,运行测试程序空跑一次,此时实测电流应该为0,若实测电流不为0,则表明测试硬件上有额外的电流消耗电路。 Step2. 增大等待时间,确认实测结果是否有变化,若有,确认测试外围电路是否包含电容,电感等元器件。 Step3. 确认测试过程中Pre-condition pattern 是否完全起作用,与研发同事确认待测I/O 是否可被稳定置于逻辑0/1的状态。 Step4. 若出现情况2(IIH/IIL所测值稍超Limit 但小于IRange)则可能是器件本身缺陷,即在晶圆制造过程中的异变或静电对管脚产生损坏导致的。 Step5. 若出现情况3(IIH/IIL所测值远超Limit 大于IRange,约等于Iclamp), 在排除程序设置,硬件原因,及Pre-Condition正确,I/O 状态正常等后,情况3 的出现基本确认器件该I/O channel path 存在重大缺陷,需尽快反馈。 |