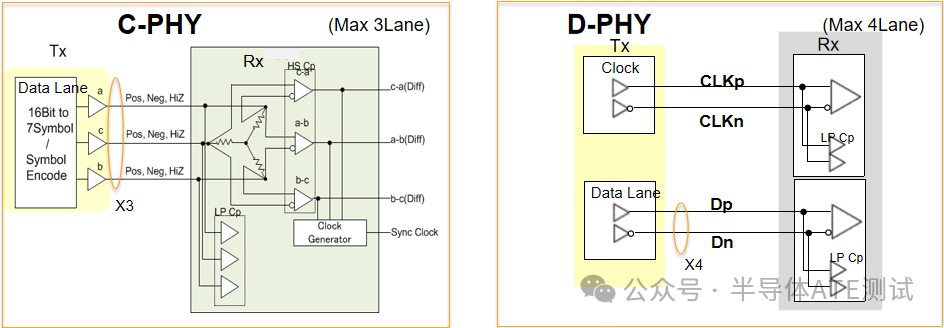

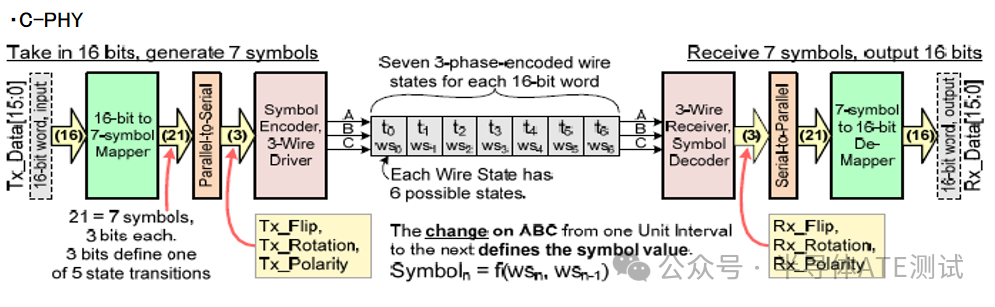

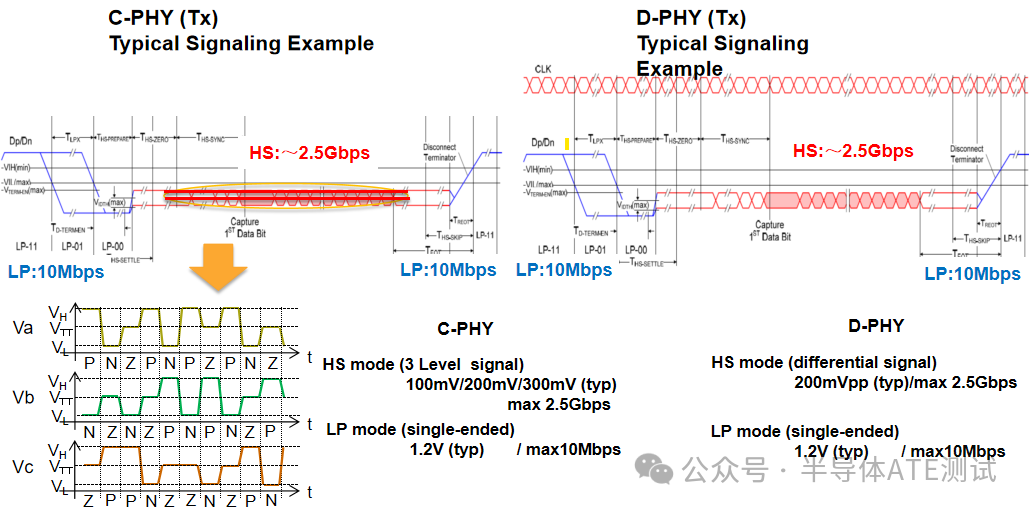

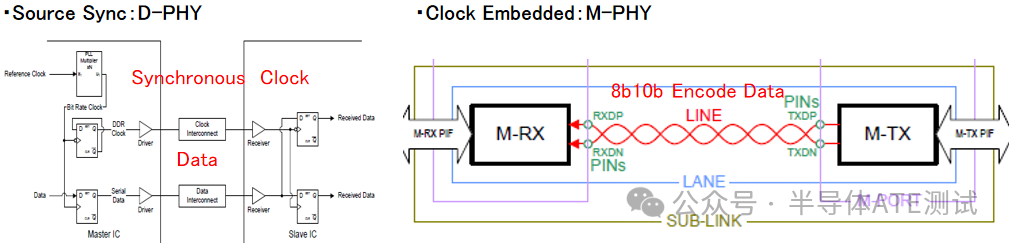

MIPI物理层协议对比1. D-PHY & C-PHY(3-phase) . 并行总线在低比特率下采用慢边沿信号以降低EMI(需在ATE测试中验证边沿速率与EMI合规性) . C-PHY的三相编码(3-phase)需测试符号间干扰(ISI)和眼图对称性. . 协议规范提供了一种灵活、低成本、高速的串行接口,其设计初衷是替代传统的CMOS并行总线。 . 测试关注点: 2. M-PHY . 支持多种Gear速率(需ATE进行多速率切换测试) . 低功耗状态(L1/L2)的电流消耗测试 . 高带宽下的抖动容限(Jitter Tolerance)验证 . 协议规范提供了一种高带宽、低引脚数的串行接口技术,同时具备优异的能效表现。 . 测试关注点: 1. 支持多种Gear速率(需ATE进行多速率切换测试) 2. 低功耗状态(L1/L2)的电流消耗测试 3. 高带宽下的抖动容限(Jitter Tolerance)验证 针对不同应用场景的两种物理层接口:D-PHY(广泛应用于CSI-2/DSI)和 C-PHY(更高带宽需求场景)进行对比如下: 1. 电气特性与信号传输

2. 带宽与效率

3. 协议与复杂度

4. 测试实现

· 3相符号编码技术(3-Phase Symbol Encoding),每符号传输2.28比特数据 |

| 特性 | C-PHY | D-PHY/M-PHY |

| 单通道信号线数 | 3线(A/B/C) | 2线(差分对P/N) |

| 电平状态 | 三电平(H/M/L) | 二电平(H/L) |

| 数据方式 | 状态跳变携带数据(需与前状态比较) | 稳态电平直接携带数据 |

| 编码方案 | 新型3相编码 | D-PHY:NRZ;M-PHY:8b10b编码 |

如何选择?

· 选D-PHY:低复杂度、成本敏感型应用(如车载中低分辨率摄像头)。· 选C-PHY:高带宽需求、引脚受限设计(如手机多摄系统或8K显示屏)。

· 选M-PHY:支持多Gear速率切换(最高达11.6Gbps/Lane),适合长距离传输(如高速存储/UFS接口、车载SerDes)。