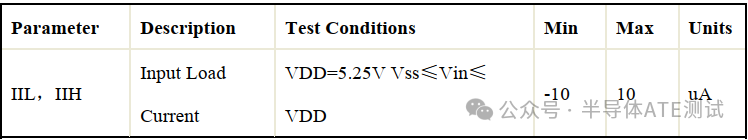

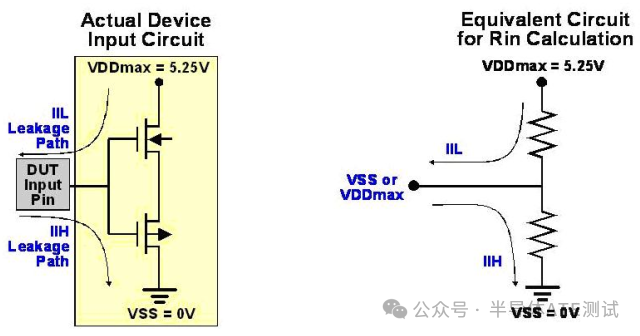

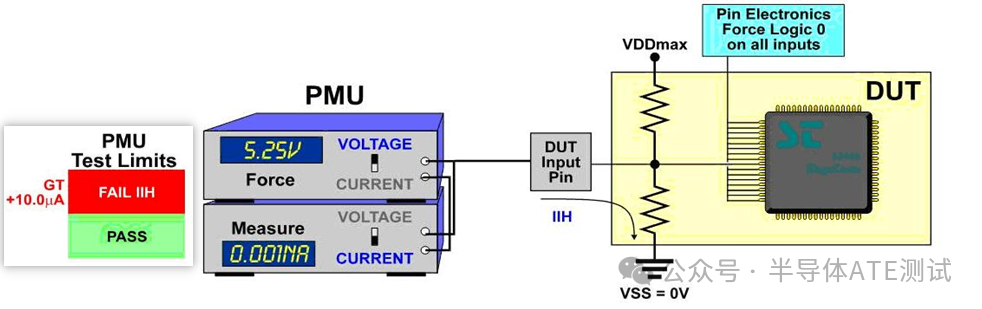

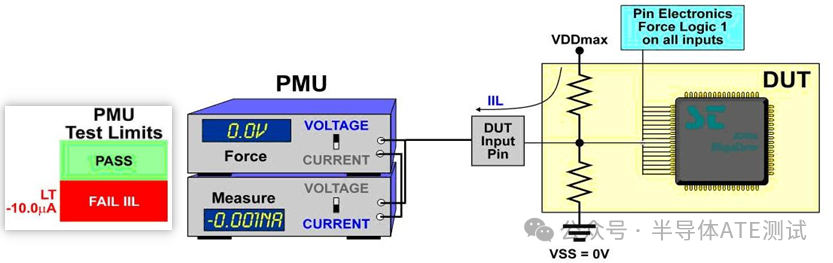

书接上文,咱们接着聊 ATE 的常规DC测试项目--IIH/IIL 静态测试。一.参数定义 IIH: 输入处于高电平(H)时 流入DUT(-) 的电流(I),I/O管脚处于输入状态时,输入管脚到地的阻抗。 IIL: 输入处于低电平(L)时 流出DUT(+) 的 电流(I),I/O管脚处于输入状态时,输入管脚到电源的阻抗。 举个栗子,如下是256x4 SRAM Spec 中关于IIH/IIL 的定义   由欧姆定律可知,该芯片最小输入阻抗R=(VDDmax - VSS)/ IIH(IIL) =5.25V/10uA = 525Kohm。 二. 测试方法IIH 串行测试:DUT 输入管脚到VSS间的阻抗.  Step1. 机台提供I/O IP vander Spec上定义的VDDmax 给DUT Power Pin Step2. Run Precondition Pattern 将DUT 所有 I/O管脚置于输入逻辑0 Step3. 利用PerPin PMU 资源 force VDDmax给当前 待测I/O Step4. 等待1~5ms Step5. 测量当前待测I/O 电流(流入DUT,电流为正) Step6. 若输出电流在Limit范围内则测试Pass,反之fail. Step7. Force VSS电压(0V) 给当前待测I/O. Step8. 对所有待测I/O 重复 Step3~7 IIL 串行测试:DUT 输入管脚到VDD间的阻抗.  Step1. 机台提供I/O IP vander Spec上定义的VDDmax 给DUT Power Pin Step2. Run Precondition Pattern 将DUT 所有I/O管脚置于输入逻辑1 Step3. 利用PerPin PMU 资源 force 0V给当前 待测I/O Step4. 等待1~5ms Step5. 测量当前待测I/O 电流(流出DUT,电流负) Step6. 若输出电流在Limit范围内则测试Pass,反之fail. Step7. Force VDDmax 给当前待测I/O. Step8. 对所有待测I/O 重复 Step3~7 三.HighLight & Trouble Shooting ① Current Measure Range选择需考虑所选机台资源的测量精度。 ② 部分机台PPMU 为电压源而非电流源,电流测试时需注意增加share资源电流测试等待时间。 ③ IIH 测试时需设置Voltage Clamp(Clamp 电压 ≈ 110%VDDmax)。 ④ 需注意在下一个管脚测试前将当前测试管脚恢复为最初的状态(参考Step7)。 ⑤ 串行测试可完整的显示管脚间漏电流路径,但测试时间增加。 ⑥对某些DUT,将所有I/O都置为低或高可能导致芯片进入异常状态,需提前与研发同事讨论确认Pre condition Pattern 及可测I/O list ⑦ 为防止其他双向I/O引脚在IIH/IIL 测试时意外打开,因DUT IDD电流导致IC内部实际供电电压小于测试设定的VDDmax ,进而导致未在最严苛的条件下进行IIH/IIL 测试,测试结果可信度降低,可以考虑在待测I/O channel 上增加输出负载,以将其固定成逻辑0/1电平,限制负载电流。 |