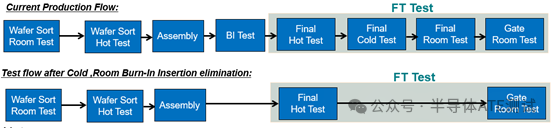

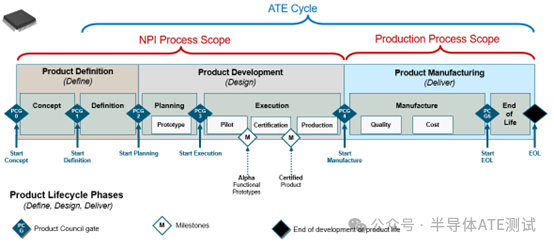

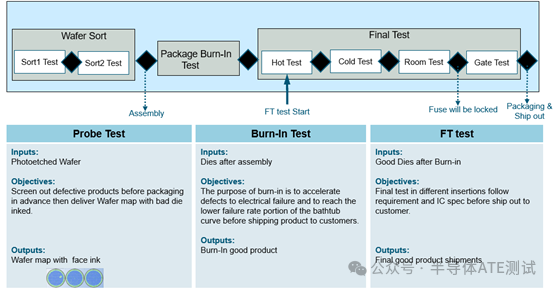

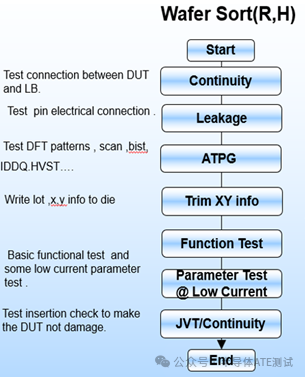

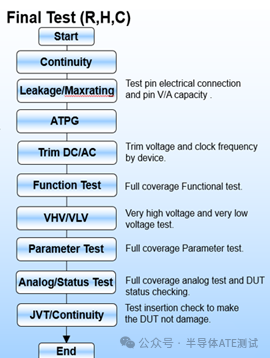

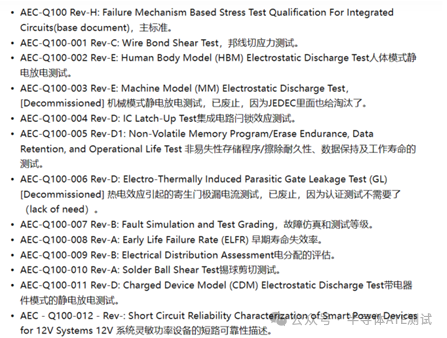

半导体测试的主要目的是确保交付给客户的芯片质量符合Datasheet(产品规格手册)的相关内容,ATE (Automated Test Equipment) 是实现批量化自动半导体测试仪器的简称。常见的消费类半导体ATE测试流程如下图所示:  依据车规APQP(Advanced Product Quality Planning)流程结合IPD (Integrated Product Development)项目管理理念,常见的车规/军规半导体ATE测试流程如下图所示:   CP Test - 晶圆测试包含如下测试站点: · Wafer Sort Room Test -常温CP 测试(除盲封外所有类型IC 产品均需经过此测试站点) · Wafer Sort Hot Test – 高温CP 测试(消费类产品,车规产品) · Wafer Sort Cold Test – 低温 CP 测试(车规,军规产品) FT Test - 封装后测试包含如下测试站点: · BI Test - BurnIn 老化测试 (所有类型IC 产品均会经过此测试站点) · Final Room Test - FT 常温测试 (所有类型IC 产品均会经过此测试站点) · Final Hot Test - FT 高温测试 (消费类产品:80℃,车规类产品:125℃/150℃) · Final Cold Test - FT 低温测试(车规类产品,军规类产品) CP测试主要目的及常见测试项: CP测试是指在划片(Dicing)前筛选不良裸片(Die),以节省芯片封装成本,CP 测试站点常见测试项如下:  FT 测试主要目的及常见测试项: FT 测试是指在封装后对芯片进行全面的功能测试,以验证封装后的芯片功能,FT 测试站点常见测试项如下:  老化测试 (Burn In Test): 通过高温高压加速芯片老化,根据芯片失效模型(浴盆曲线)暴露潜在缺陷,BI 测试可在FT 后单独进行也可与SLT合并,进行系统级Burn-In 除上述测试外,针对高可靠性需求芯片(车规,工规,航天,军规等)还有如下测试站点: SLT系统级测试(System Level Test): 针对复杂功能芯片(Soc,GPU),一般需要将IC置于真实系统板中进行测试验证,一般而言,SLT与ATE互补用来覆盖ATE ATPG难以模拟的测试场景(如多芯片交互,操作系统启动,应用程序压力测试等)。 可靠性测试(Reliability Test): 对工规,车规,军规等有可靠性测试需求的芯片,需根据实际使用场景要求进行相应的抽样测试。常见的AECQ-100 测试项如下图所示:  ATE 测试流程总结:

|