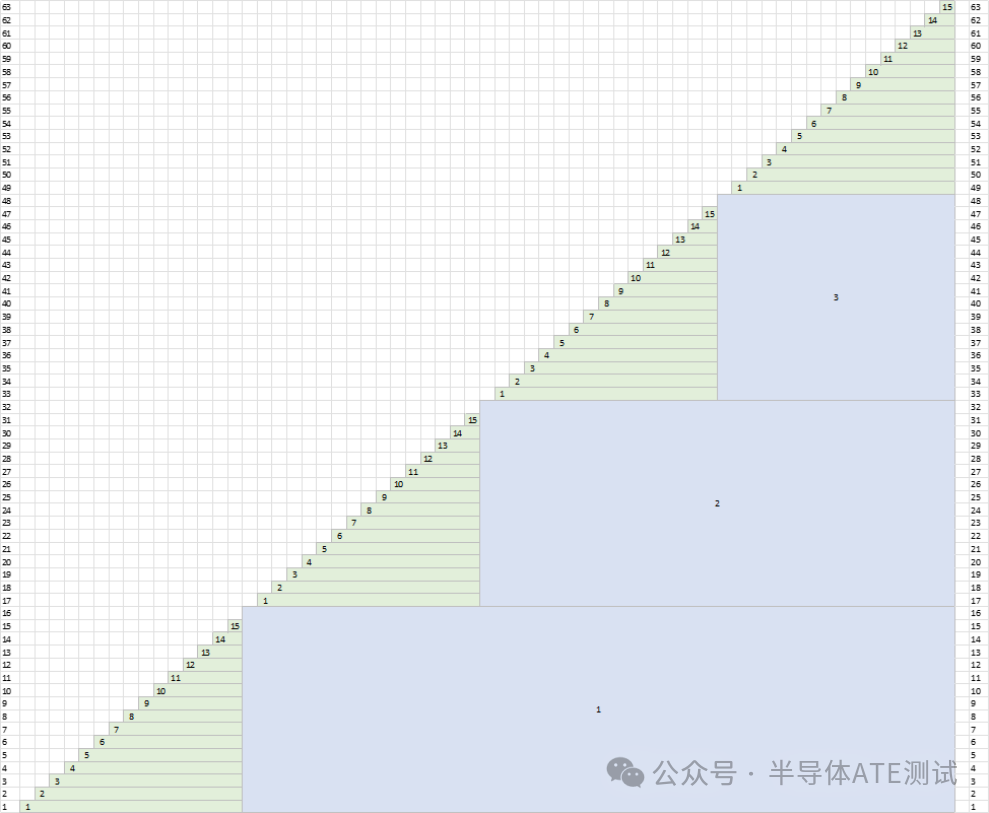

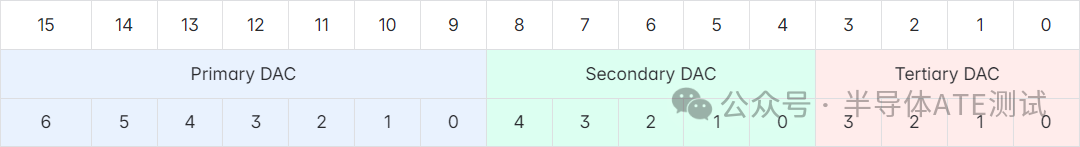

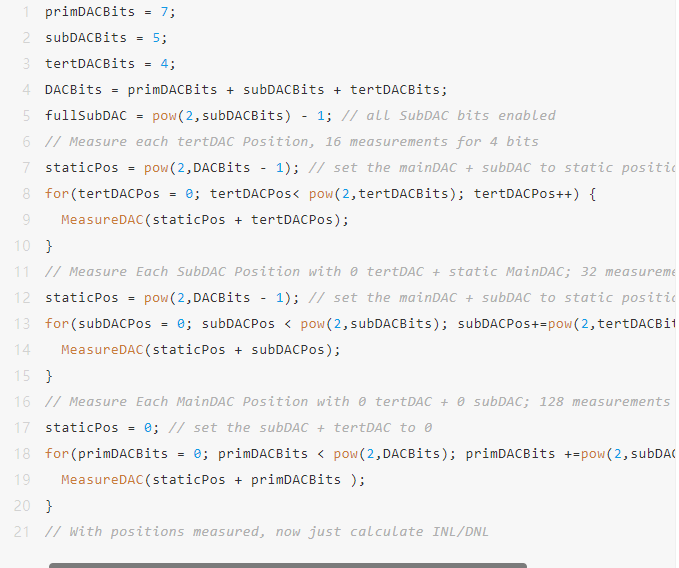

"在测试多级DAC的积分非线性(INL)和微分非线性(DNL)时,通常不需要对所有代码进行全量测试,而是可以通过精心选择部分关键代码子集来完成验证。"举个栗子:一颗16-bit 3-stage(三级)DAC,内部包含3个sub-DAC(7-bit,5-bit,4-bit)全代码扫描需要遍历65536个Code(2^16)。而通过对内部的子DAC扫描,仅需遍历176个Code(2^7 + 2^5 + 2^4),详见文末代码示例。 这种方法的有效性基于多级DAC的结构特点: 分段测试原理 o 多级DAC的测试本质上是对多个小型DAC(主DAC+副DAC)的独立分析与组合验证 o 主DAC(MSB段)的INL/DNL可通过测试其所有代码的跳变点来评估 o 副DAC(LSB段)只需验证其满量程和关键过渡点 o 级间耦合误差通过特定边界代码测试即可捕捉。如下图所示,以一个6位2级DAC为例:包含2位主DAC(蓝色部分)和4位副DAC(绿色部分)  副DAC(绿色部分)的斜坡信号上任意两点之间的差值(Delta)应当保持一致,无论主DAC(蓝色部分)的位数如何叠加到副DAC上。因此,仅需测量副DAC的任意单段斜坡信号,即可完整表征副DAC的特性。同理,禁用副DAC并测量主DAC的斜坡信号,即可解析主DAC的特性。DAC的最终输出结果,均可通过主DAC特性 + 副DAC特性的组合计算得出。 补充说明 1. Delta一致性: o 副DAC的线性度与其所处主DAC的码值无关,这是分段式DAC的核心设计假设。 o 例如:主DAC码值从00切换到01时,副DAC的4位斜坡的步进(LSB)应保持恒定。 2. 测试效率优化: o 通过分离测试主/副DAC,可将传统全码扫描(如6位DAC需测64点)简化为分段测试(主DAC测4点 + 副DAC测16点),大幅降低测试时间。 3. 误差叠加模型: o 若主DAC的INL误差为ΔM,副DAC的INL误差为ΔS,则整体DAC输出误差为ΔM + (ΔS / 2^k)(k为主DAC位数)。此关系需在校准时验证。 2级DAC测试示例 对于由主DAC和副DAC组成的2级DAC,测试步骤如下: o 分段测试策略✅ 固定主DAC码值,测试副DAC的所有位置· 保持主DAC在某一固定码值(如00),扫描副DAC的所有可能码值(如4位副DAC测16点),记录输出。· 验证副DAC的线性度(DNL/INL),确保其步进(Delta)均匀。 ✅ 固定副DAC为0,测试主DAC的所有位置 · 将副DAC置零(0000),扫描主DAC的所有码值(如2位主DAC测4点),记录输出。 · 验证主DAC的步进是否满足单调性要求。 o 单调性(Monotonicity)保证条件 若满足以下条件,可确保DAC整体单调(输出随码值增加而严格递增): MaxSecDAC(副DAC最大步进) < MinPrimDAC(主DAC最小步进) o 参数计算: MaxSecDAC = 副DAC全1输出 - 副DAC全0输出(副DAC的总跨度) MinPrimDAC = 主DAC相邻码值的最小步进(Min(ΔPrimary)) MaxPrimDAC = 主DAC相邻码值的最大步进(Max(ΔPrimary)) o 单调性判定: 若 MaxSecDAC < MinPrimDAC,则DAC必定单调。 否则,可能出现非单调(输出回退)情况。 o 最差DNL(差分非线性)计算 最差DNL由以下两种情况的最大值决定: ✅主DAC步进与副DAC跨度的偏差: DNL_case1 = MaxPrimDAC - MaxSecDAC(主DAC最大步进与副DAC总跨度的差值) ✅副DAC自身的步进不均匀性: DNL_case2 = 副DAC任意相邻码值的步进偏差 最终最差DNL:Worst_DNL = Max(DNL_case1, DNL_case2) 3级DAC测试示例对于由主DAC、副DAC和三级DAC组成的3级DAC,测试流程是2级DAC的扩展,需分层验证各级特性并确保整体单调性。测试步骤如下:o 分层测试策略 ✅ 固定主DAC和副DAC,测试三级DAC的所有位置 · 设置主DAC和副DAC为固定码值(如00和0000),扫描三级DAC的所有码值(如4位三级DAC测16点)。 · 验证三级DAC的线性度(DNL/INL),确保其步进(Delta)均匀。 ✅ 固定主DAC,三级DAC置零,测试副DAC的所有位置 · 主DAC固定(如00),三级DAC置零(0000),扫描副DAC的所有码值(如4位副DAC测16点)。 · 验证副DAC的步进是否满足单调性要求。 ✅ 副DAC和三级DAC置零,测试主DAC的所有位置 · 副DAC和三级DAC均置零(0000和0000),扫描主DAC的所有码值(如2位主DAC测4点)。 · 验证主DAC的步进特性。 o 单调性(Monotonicity)保证条件 ✅副DAC单调性条件FullTertDAC(三级DAC全跨度) < MinSecDAC(副DAC最小步进)计算参数: · FullTertDAC = 三级DAC全1输出 - 三级DAC全0输出 · MinSecDAC = 副DAC相邻码值的最小步进(Min(ΔSecondary)) · MaxSecDAC = 副DAC相邻码值的最大步进(Max(ΔSecondary)) 判定: · 若 FullTertDAC < MinSecDAC,则副DAC段保证单调。 · 副DAC最差DNL = MaxSecDAC - FullTertDAC ✅主DAC单调性条件FullSecDAC(副DAC全跨度) < MinPrimDAC(主DAC最小步进)o 参数计算: · FullSecDAC = 副DAC全1输出 - 副DAC全0输出 · MinPrimDAC = 主DAC相邻码值的最小步进(Min(ΔPrimary)) · MaxPrimDAC = 主DAC相邻码值的最大步进(Max(ΔPrimary)) 判定: · 若 FullSecDAC < MinPrimDAC,则主DAC段保证单调。 · 主DAC最差DNL = MaxPrimDAC - FullSecDAC · 对于7位主DAC + 5位副DAC + 4位三级DAC 的16位分段DAC:

|