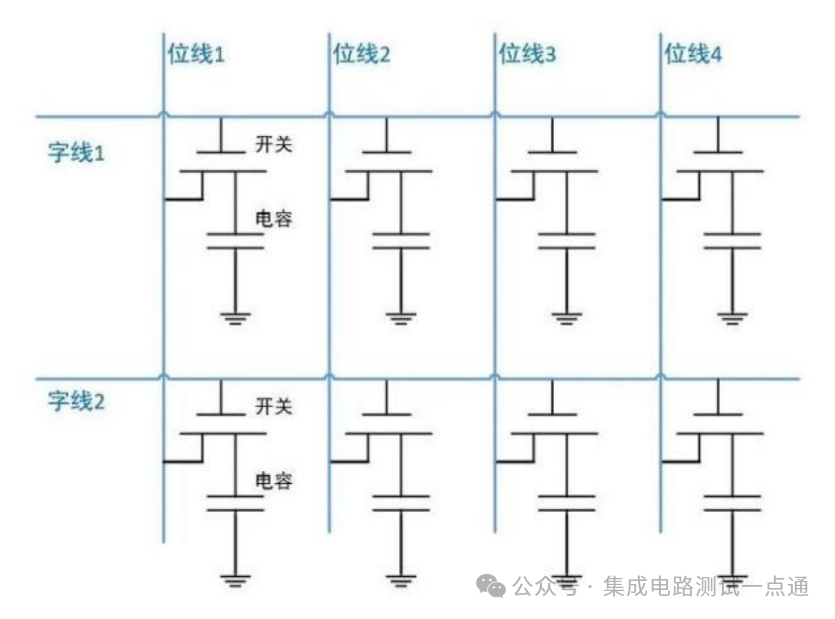

I.字线电压的概念及产生方式II.字线电压对DRAM性能与可靠性的影响 III.在DRAM测试中关于字线电压的关注点 I. 字线电压的概念及产生方式A. 字线电压的概念动态随机存取存储器(DRAM)的基本存储单元由一个晶体管和一个电容器(1T1C)构成。在这个结构中,晶体管扮演着一个“开关”的角色,而电容器则通过存储电荷来表示一个比特的数据(逻辑“1”或“0”)。大量的基本存储单元被组织成一个二维阵列,横向连接一整行所有访问晶体管栅极的导线被称为字线(Word Line, WL)。纵向连接一整列晶体管源极或漏极的导线被称为位线(Bit Line, BL)。施加在字线上的电压信号即为字线电压,其核心功能是通过控制电压的高低状态,实现对特定行存储单元的“选中”或“未选中”。当内存控制器需要访问(读取或写入)某个特定的存储单元时,它会“激活”对应的字线,即在该字线上施加一个正电压。这个电压会打开该行所有的访问晶体管,从而将它们各自的存储电容器连接到位线上。这个核心操作被称为行激活(Row Activation)。  B. 字线电压的几个特点(1) "激活"态字线电压——升压为什么不直接将DRAM的电源电压(VDD)施加到字线上呢?以下几个关键的物理原因决定了字线电压必须使用一个高于VDD的“升压”电压。 · 克服阈值电压(Vt)损失:DRAM 基本存储单元中的访问晶体管通常是N沟道金属氧化物半导体(NMOS)器件,该晶体管栅极(G)连接字线,漏极(D)连接位线,源极(S)连接存储电容。为保持晶体管导通状态,栅极字线电压必须满足VWL≥V_source+Vt的状态(Vt是晶体管的阈值电压)。如果VWL仅为VDD,那么当源极电压达到VDD−Vt时,晶体管就会关闭,导致最终写入电容器的电压被限制在VDD−Vt,这种现象被称为“Vt损失”(Vt drop)。一个不完整的“1”电平会严重削弱信号裕度,降低读操作的可靠性。因此,字线电压必须被提升到一个更高的水平,确保字线电压>VDD+Vt 。这样可以保证即使在电容器完全充电至VDD的过程中,访问晶体管能一直保持强导通状态,从而将完整的逻辑“1”电平写入存储单元。 · 最大化读操作的信号裕度:在读操作期间,存储单元微小的电容器(电容值Ccell)中存储的电荷会与电容值大得多的位线(电容值CBitline)进行电荷共享 。这会在位线上产生一个非常微弱的电压扰动(ΔV),这个扰动随后被一个称为感应放大器(Sense Amplifier)的差分放大器检测并放大。一个由于字线电压而得以完全充电的“1”状态,能够最大化这个初始电压扰动,从而提高信噪比,确保感测放大器能够快速而准确地区 分逻辑“1”和“0” 。 (2) “关闭”态字线电压——接地或负压当字线处于“关闭”状态时,即驱动到低电平(通常是地电压)时,该行的所有访问晶体管必须完全关闭,以防止存储在电容器中的电荷泄漏。为了进一步抑制亚阈值泄漏电流并延长数据保持时间(retention time),一些先进的DRAM设计甚至会采用负字线电压,将非选择状态的字线驱动到一个低于地的电位 。(3) 分层字线架构:分而治之 为了应对现代DRAM巨大的阵列尺寸,设计者采用了分层字线架构(Hierarchical Word Line Architecture)。在这种架构中,行地址解码器驱动的不是一条贯穿整个存储阵列的长字线,而是一条主字线(Master Word Line, MWL)。这条主字线连接到多个子阵列块。在每个子阵列内部,一个子字线驱动器(Sub-word Line Driver)接收来自MWL的信号,并用它来驱动连接到实际存储单元的、短得多的局部字线(Local Word Line, LWL或Sub-Word Line, SWL)。这种“分而治之”的策略极大地降低了单次行激活操作所需驱动的电容负载,从而显著缩短了行激活延迟(tRCD)并降低了功耗 。字线电压通过这个分层路径,最终被施加到被选中的局部字线上的字线驱动器(Word Line Driver)电路上 。字线驱动器是连接逻辑控制和物理执行的关键环节。一个典型的字线驱动器包含一个上拉网络(通常是PMOS晶体管),负责将字线连接到字线电压电源轨;以及一个下拉网络(通常是NMOS晶体管),负责将其连接到地(或负电压轨)。当行地址解码器选中某一行时,会发出逻辑信号激活该行对应的字线驱动器。驱动器响应后,其上拉网络导通,将高压字线电压施加到字线上,激活该行。对于所有未被选中的行,其驱动器的下拉网络则被激活,将字线拉至低电平,确保其保持在“关闭”状态 。这些驱动器的设计对DRAM的性能至关重要,因为它们必须能够快速地对具有高电容的字线进行充放电。 C. 字线电压的产生(1) 电荷泵原理(开关电容转换器)电荷泵是一种无电感的DC-DC转换器,它能够产生高于输入电源电压的输出电压 (Vout>Vin)。其基本工作原理依赖于一个“飞跨电容”(flying capacitor)和一系列开关,并通过两个阶段的循环操作实现电压提升 : · 充电阶段: 开关配置将飞跨电容与输入电源(例如VDD)并联,使其充电至VDD。 · 泵送阶段: 电路重新配置,将已充电的飞跨电容与输入电源串联。这样,输出端看到的电压便是输入电源电压与电容电压之和,理想情况下为2×VDD。 通过将多个这样的阶段级联,可以实现更高的电压倍增。整个过程由一组非重叠的时钟信号以高频(通常在几十kHz到几MHz之间)驱动。 (2) PMIC:电源领域的“片上系统”DDR5模组通过集成一个专用的PMIC,将电源管理提升到了系统层面。这个PMIC本身就是一个复杂的电源系统,通常包含:· 多个同步降压转换器(SMPS): 这些高效的开关模式电源负责将来自主板的较高电压(如5V或12V)降压至DRAM所需的1.1V(VDD/VDDQ)和1.8V(字线电压)。 · 低压差线性稳压器(LDO): 用于为其他低功耗或对噪声敏感的电路提供洁净的电源。 · 通信与监控接口: PMIC通过I2C或I3C总线与系统主控进行通信,允许实时监控电压、电流、温度等遥测数据,并支持动态电压调节。 从片上电荷泵到模组PMIC的转变,是系统级优化的体现。设计者们逐渐意识到与其在DRAM芯片上花费宝贵的面积和功耗来构建日益复杂的电荷泵,不如使用一个专门的、高效的外部组件来解决电源问题。PMIC通过将高效的电压转换和精确的调节功能置于离负载最近的位置,为现代DRAM提供了前所未有的电源完整性。

|

| DRAM标准 |

核心电压 (VDD) |

I/O电压(VDDQ) | 字线电压 | 字线电压生成方式 |

| DDR3 | 1.5V / 1.35V | 1.5V / 1.35V | 约2.5V-3.0V | 基于VDD的内部片上电荷泵 |

| DDR4 | 1.2V | 1.2V | 2.5V (标称值) | 专用的外部电源引脚 |

| DDR5 | 1.1V | 1.1V | 1.8V (标称值) | DIMM模组上的电源管理IC (PMIC) |

II. 字线电压对DRAM性能与可靠性的影响

字线电压并非一个可以随意设定的参数,它处于性能、功耗与可靠性之间复杂权衡的中心。本章将探讨字线电压对DRAM关键指标的双重影响,揭示其在速度与稳定性平衡中的核心地位。A. 核心时序参数

字线电压水平直接影响DRAM的几个关键时序参数,这些参数定义了内存的访问速度。

· tRCD (行地址到列地址延迟):从发出“行激活”命令到可以开始读取数据所需的时间。降低字线电压会增加(恶化)tRCD。这是因为较低的栅极电压(字线电压)导致访问晶体管的导通能力减弱,减慢了存储单元电荷与位线之间的共享过程。反之,较高的字线电压能提供更强的驱动能力,理论上可能允许更激进(更低)的tRCD设置,但这是一种复杂的相互作用,并伴随着风险。

· tRAS (行激活时间): 一行必须保持激活状态以确保在读取后数据能被完全写回(恢复)到存储电容器的最短时间。降低字线电压会削弱电荷恢复过程,从而使tRAS恶化,因为访问晶体管可能在电容器完全恢复到VDD之前就因栅源电压差不足而关闭。这可能需要一个更长(更差)的tRAS来保证数据完整性。

· tRP (行预充电时间):这是关闭当前行并为激活下一行做准备所需的时间。增加字线电压可能会损害(增加)tRP,因为将电容极高的字线从一个更高的电压(字线电压)完全放电至地电平需要更长的时间。

Note: 在超频社区中,有时会通过增加字线电压来尝试稳定激进的时序设置。这应被理解为一种在高风险边缘操作中寻求边际稳定性的方法,而不是对基础物理原理的否定。研究明确指出,较低的字线电压本质上需要更长的访问延迟。

B. 数据保持时间

数据保持时间(Data Retention Time)衡量的是一个存储单元在没有刷新的情况下能够可靠地保持其存储数据的时间长度。这个特性与字线电压通过电荷恢复过程紧密相连。降低字线电压可能导致电荷恢复不完全。一个未被完全充电的单元,其电荷会更快地泄漏到无法被感测放大器识别的水平。因此,降低字线电压会对数据保持时间产生负面影响。实验数据显示,随着字线电压的降低,在给定的刷新间隔内,出现数据保持错误的单元数量会增加。尽管对于许多芯片来说,这种影响仍在标准64ms刷新间隔(tREFI)的安全裕度之内,但它揭示了字线电压调节的另一个可靠性风险。

C. “行锤”(Row Hammer)

Row Hammer是一种硬件可靠性问题,现已演变为一个严重的安全漏洞。它指的是对DRAM中的某一行(攻击行)进行高频率的重复激活和预充电操作,会导致其物理上相邻的行(受害行)发生位翻转(bit flips),即数据损坏。

(1) Row Hammer的物理机制

攻击行字线电压的剧烈、反复切换(从0V到字线电压再返回)会通过电磁干扰和寄生电容耦合,对其相邻的受害行产生扰动。这种扰动会加速受害行存储单元的电荷泄漏。如果在下一次刷新周期到来之前,某个受害单元泄漏了过多的电荷,其存储的数据就会被破坏。字线电压正是这个“锤子”的力度。扰动的强度与字线电压的摆幅直接相关。更高的字线电压会产生更强的电场和更剧烈的电压波动,从而极大地加剧Row Hammer效应。

(2) 字线电压调制作为一种Row Hammer缓解策略

鉴于字线电压在Row Hammer机制中的核心作用,研究人员发现降低字线电压是一种有效的Row Hammer缓解手段。降低字线电压可以显著增加Row Hammer诱发位翻转所需的激活次数(即“锤击阈值”),并降低总体的位错误率。一项研究表明,降低字线电压最多可使锤击阈值增加85.8%,并将位错误率降低66.9%。

D. 根本性的权衡——访问完整性与扰动完整性的冲突

字线电压是现代DRAM设计中一个根本性冲突的焦点:访问完整性(Access Integrity)与扰动完整性(Disturbance Integrity)之间的冲突。

· 为了确保一个比特被正确读写(访问完整性),需要一个较高的字线电压来完全打开访问晶体管,最大化信号裕度。这推动字线电压向更高值发展。

· 为了确保访问一行不会损坏其邻居(扰动完整性,即防止Row Hammer),需要最小化字线上的电压摆幅。这推动字线电压向更低值发展。

III. 在DRAM测试中关于字线电压的关注点

A. 功能测试

ATE会运行专门设计的内存测试算法(如March测试),在不同的字线电压、VDD和时序组合下对存储阵列进行读写,以检测是否存在失效的存储单元。

B. 压力测试

为了确保产品的长期可靠性,DRAM需要经过压力测试来筛选出潜在的(latent)缺陷。晶圆级老化(Wafer-Level Burn-In, WLBI): 这是一种在晶圆阶段对芯片施加加速老化条件(如高温、高压)的测试过程,旨在激发那些在标准测试中不易暴露的“早期失效”缺陷。在基于缺陷的晶圆老化(Defect-Based WLBI)方法中,字线电压是一个关键的压力因子。通过施加高于正常工作范围的字线电压电压,对潜在的缺陷节点施加电应力。这种压力测试针对特定的失效模型,例如相邻字线之间的微弱电阻性桥接(WL-WL bridge)、字线与位线间的桥接(WL-BL bridge),或单元晶体管内部的短路等。施加高电压差可以使这些微弱的连接彻底击穿,从而转变为一个可以被ATE轻易检测到的硬故障。

C. 字线电压电源完整性

电源完整性(Power Integrity, PI)是衡量电源供应质量的关键指标。对于字线电压稳定性两个核心的PI测量指标是纹波(Ripple)和瞬态电压降(Voltage Droop)。

· 纹波:这是指在直流电压上叠加的周期性交流成分,通常由PMIC或电荷泵的开关频率引起。

· 电压降: 这是指当负载电流突然急剧增加时(即负载瞬变),电源电压发生的暂时性下降。对于字线电压而言,最大的负载瞬变发生在“行激活”命令期间,此时字线驱动器需要瞬间提供大电流来为高电容的字线充电。

这些微小的电压变化必须使用高带宽示波器进行测量。正确的探测技术至关重要,必须采用“针尖与接地环”(tip and barrel)或尽可能短的接地线方法,以最大限度地减少探头引入的电感,否则测量结果中会包含虚假的振铃,无法反映真实的信号质量。测量时,示波器通常设置为交流耦合(AC coupling),以便滤除高压直流分量,专注于观察微小的交流变化。

IV. 结语

随着DRAM工艺节点向更小尺寸继续微缩,围绕字线电压的挑战只会愈发严峻。访问完整性与扰动完整性之间的矛盾将变得更加尖锐。未来的DRAM可能会集成更复杂的片上电路,可能会出现更细粒度的字线电压控制,或者在内存控制器或PMIC中集成基于人工智能/机器学习的预测性电源和可靠性管理算法,都是合乎逻辑的未来方向。