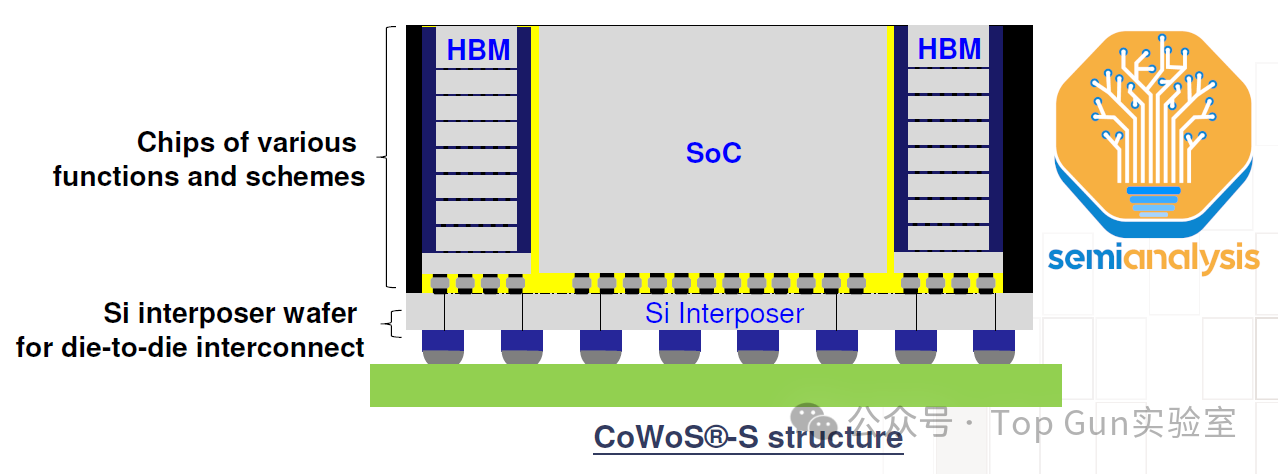

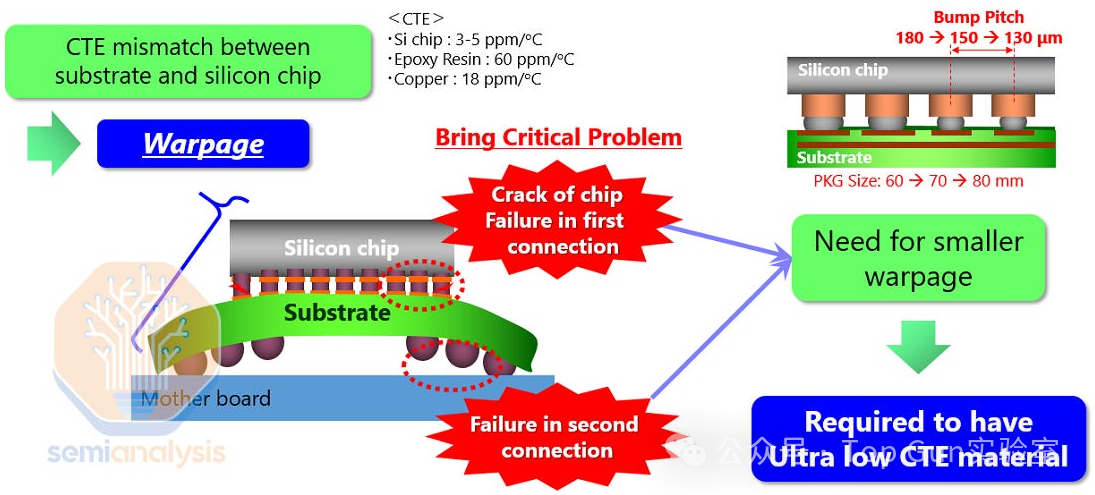

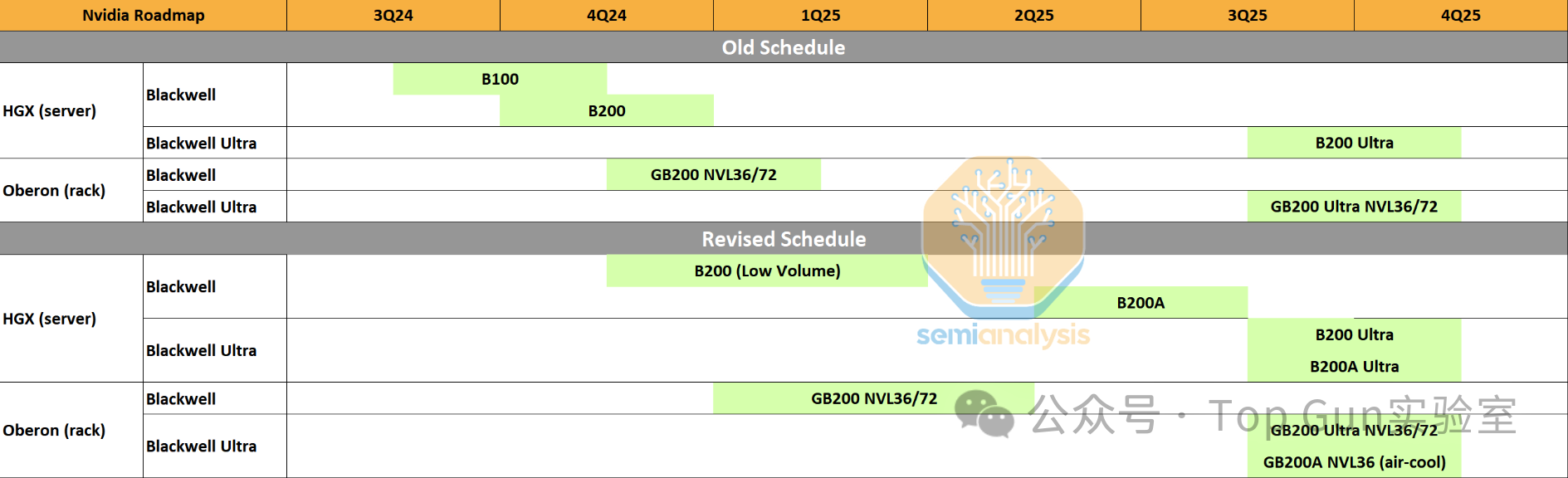

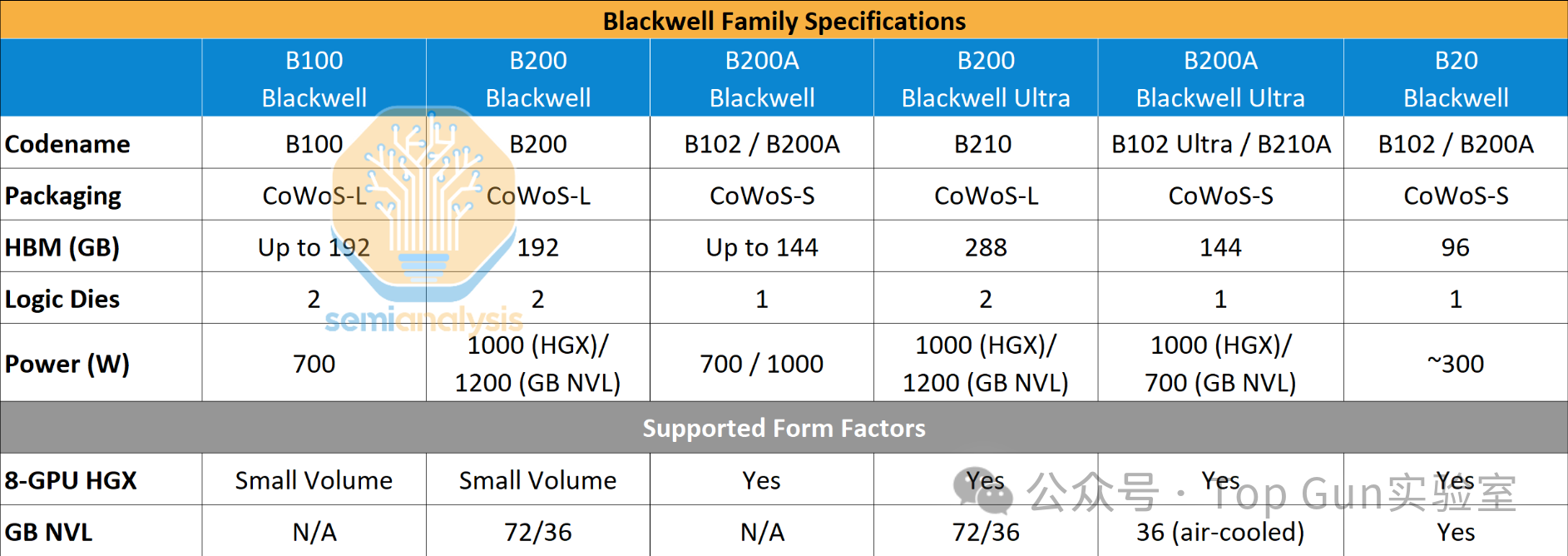

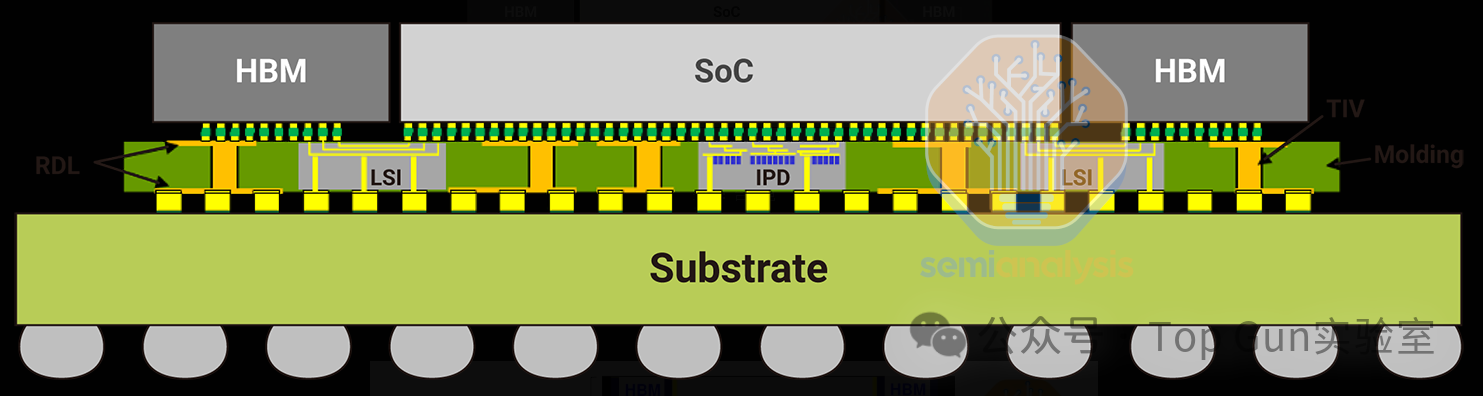

一、问题概述英伟达(Nvidia)Blackwell架构芯片在24年下半年的生产延迟,主要源于其首次大规模采用的台积电(TSMC)CoWoS-L封装技术在初期量产阶段的良率极低。根据SemiAnalysis的深度分析,该问题的根源在于Blackwell复杂的双芯片(Dual-die)设计与CoWoS-L封装工艺在热机械稳定性上的不匹配,导致了严重的物理失效。 二、技术背景:CoWoS-L 的架构演进为了实现 Blackwell 巨大的算力需求,英伟达从传统的CoWoS-S转向了更具扩展性的CoWoS-L封装。 2.1 CoWoS-L结构解析CoWoS-L使用RDL(再分布层)中介层,并在其中嵌入LSI(局部硅互连)桥接芯片。这种设计允许在有机基板上拼接多个大型芯片,突破了传统硅中介层的尺寸限制。

|