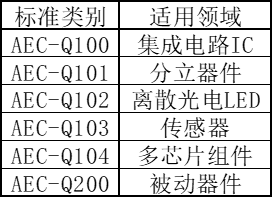

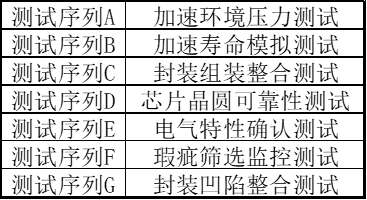

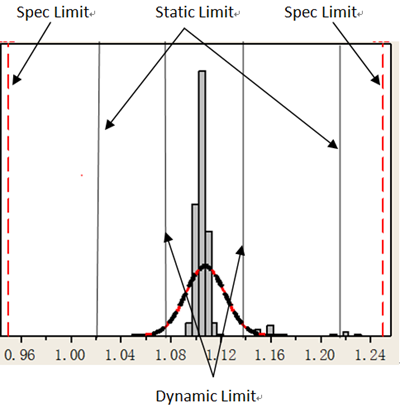

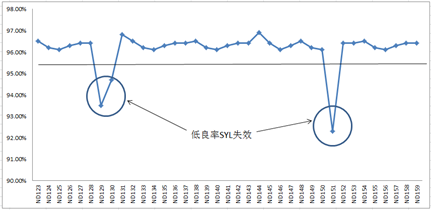

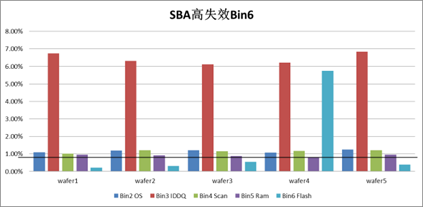

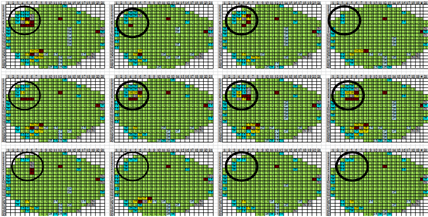

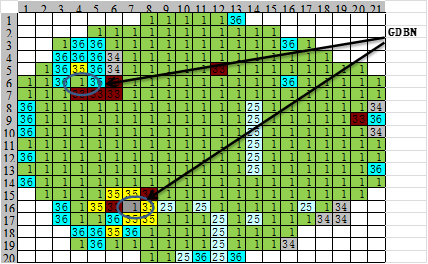

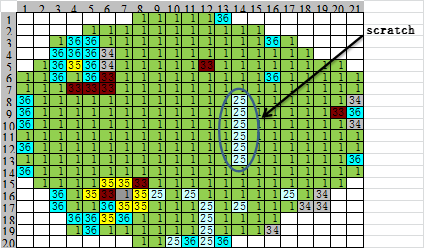

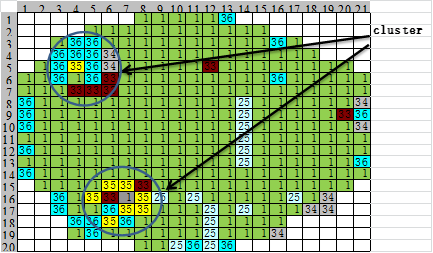

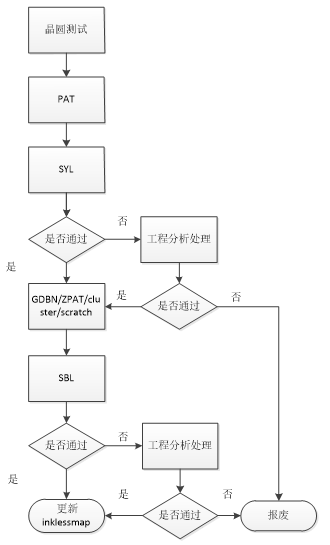

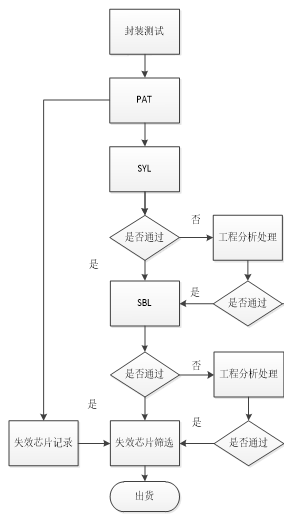

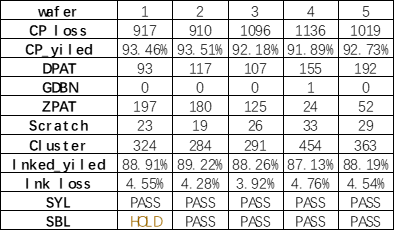

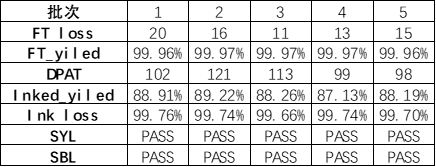

摘要随着新能源以及无人驾驶汽车的迅速发展,车规级芯片的作用愈加重要。本文介绍了符合AEC-Q100标准的车规级芯片筛选方法,首先对AEC-Q100汽车芯片质量标准体系进行概述。之后详细介绍了符合AEC-Q001和AEC-Q002标准的基于统计学的筛选方法,以及基于空间位置的异常点检测方法,分别介绍了在晶圆测试和封装测试阶段的筛选流程。该方法已成功应用于车规级芯片筛选测试当中。 引言 近年来,随着新能源以及无人驾驶汽车的迅速发展,车规级芯片的作用愈加重要,这是芯片产业应用的一个重要方向。车规级(Automotive Grade)芯片是指满足车载等级要求的芯片元器件。车规级芯片对比消费级和工业级芯片,对可靠性的要求要高出许多,例如工作温度范围、工作稳定性、不良率等。通过集成电路测试手段,能够将合格芯片与不合格的芯片区分开,保证产品的质量和可靠性。但是,传统的筛选测试手段已经无法满足车规级芯片的严苛要求。AEC-Q系列标准作为行业公认的车规级元器件认证标准,已成为电子元器件是否适用于汽车应用的一个标志,该标准为车规级芯片的筛选测试提供了整套的指导性建议。因此,如何通过合理的筛选测试手段,筛选出符合AEC-Q100标准要求的集成电路芯片,是本文研究的主要内容。 01 AEC-Q100标准简介 AEC是汽车电子委员会(Automotive Electronics Council)的简称,总部设在美国,AEC-Q标准最初由三大汽车制造商(克莱斯勒、福特和通用汽车)建立,其目的是建立共同的零部件资格和质量体系标准。该标准所包含的领域见表1,对于不同领域的电子器件,适用的标准也不相同。 表1 AEC-Q领域分类  本文主要介绍其中的AEC-Q100标准,该标准主要针对集成电路芯片及其封装的应力测试,其最新版本Rev-H发布于2014年。AEC-Q100标准定义了最低应力测试认证的要求和集成电路认证的测试参考条件,这些测试项目能够发现和识别集成电路芯片和其封装的故障及问题。该标准的目标是制定一系列芯片产品能够通过的标准测试,从而预测该产品在实际应用中可以达到的的质量水平以及产品可靠性。 AEC-Q100标准总共包括7组测试序列,如表2所示。 表2 AEC-Q100测试序列  在以上测试序列中,对应筛选测试领域,测试序列F是我们关注的重点,该测试组通过部件平均测试(Part Average Testing, PAT)和良率统计分析(Statistical Bin/Yield Analysis, SBA/SYA)两种测试方法,对已完成自动化筛选测试的测试结果进行加严筛选,从而进一步提高芯片的可靠性。 在AEC-Q标准体系中,PAT方法和SBA/SYA方法作为AEC-Q的参考文件单独存在,其中AEC-Q001定义了零件平均测试指导原则,AEC-Q002定义了良品率统计分析的指导原则,二者不仅仅应用于AEC-Q100标准中,也对整个AEC-Q标准适用。 02 符合AEC-Q的筛选方法介绍 PAT和SBA/SYA方法并不是使用自动化测试机台进行的筛选流程,而是基于统计学原理对已完成的测试结果进行的筛选,下面对二者的原理和应用分别进行介绍。 2.1 PAT筛选测试 PAT筛选测试是一种基于统计学的方法,主要用于从已完成自动化测试的器件中去除存在异常特性的器件,PAT筛选中的测试极限值是根据指定器件的指定电气测试的结果样本建立的。根据极限限值设定的方法不同,PAT筛选可以分为静态PAT和动态PAT,二者分别可称为SPAT(Static PAT)和DPAT(Dynamic PAT)。PAT的本质是在实际生产过程根据生产数据对芯片规格书中定义的上下限进行不断地修正,用于确保AEC-Q100所提供芯片的可靠性和一致性。一般地,将产品规格书中定义的上下限称为LSL、USL,筛选测试程序中定义的上下限称为LTL、UTL,PAT筛选的上下限称为PAT limit。原则上,LSL/USL的范围>LTL/UTL范围>PAT limit范围。PAT limit的限值范围主要用于体现生产工艺稳定性,而LSL/USL主要体现芯片本身的特征特性。 静态PAT是最简单的PAT方法,在生产初期需要收集至少6个批次的测试数据,并且确认这些批次已经通过了筛选测试。之后,通过从每个批次中选择至少30个随机数据,用于建立后期测试的稳健平均值(robust mean)和稳健西格玛值(robust sigma)。对于晶圆测试,可以使用5筒测试分别选择晶圆上、下、左、右、中5个区域的各5颗DIE(晶圆裸片)建立数据。若生成早期无法获得6个批次的数据,可以使用表征批次数据,测试限值设置如下: 该规格能够筛选出明显偏离正常的数据。在稳定生产6个月后,需要每半年对静态PAT限值进行评审,并根据需要更新。 动态PAT比静态PAT限值设定更加频繁,筛选也更加严格。该方法需要持续的动态调整PAT的限值,根据实际生产情况,在晶圆测试阶段,可以选择一个晶圆批次更新一次PAT限值,在封装测试阶段,可以选择一个封装批次进行一次更新。对于具备可追溯性的芯片,可以在测试完成后统一使用动态PAT进行筛选,而对于不具备可追溯性的芯片,需要在设定动态PAT限值后再全部进行一次筛选测试。 静态PAT限值Static Limit、动态PAT限值Dynamic Limit、测试限值Spec Limit三者关系如图1所示:  图1 静态PAT、动态PAT、SPEC三者限值关系 3.2 SBA/SYA测试 SBA/SYA测试用于去除存在异常器件的批次。该测试基于统计学方法,能够识别出存在异常低良率或者存在异常高失效bin值的晶圆片、晶圆批次或封装批次。生产经验表明,特征参数存在异常的晶圆或封装批次可能质量较差,存在出现可靠性和质量相关问题的风险。在AEC-Q标准中,建议在做SBA/SYA筛选时使用以PAT limit作为限值的测试数据。 在使用SBA/SYA筛选测试的过程中,生产初期需要收集至少6个批次的产品数据,统计各批次良率信息和所有失效Bin值的分布特性,由此计算良率和失效Bin值通过率的百分比平均值(mean)和百分比西格玛值(sigma),并计算出良率限值通过百分比(SYL)和失效Bin值通过百分比(SBL)。基于以上数据设定的SYL和SBL如下: SYL1=Mean -3 Sigma SBL1=Mean+3 Sigma SYL2=Mean -4 Sigma SBL2=Mean+4 Sigma 其中,任何良率低于SYL1或Bin失效率高于SBL1的晶圆批次或封装批次都需要标记为“控制”以供工程评审,任何低于SYL2和SBL2的晶圆批次或封装批次都要求标记“隔离”并做出改善。对于隔离批次的处置需要进行风险评估,并采取遏制措施,以降低对用户或客户的风险。对于重大偏差,需要确定根本原因、制定纠正措施和未来预防措施。图2中对超出SBL限值的Bin6高失效wafer进行了隔离处理。图3中对超出SYL限值的高失效wafer进行了隔离处理。  图2 SYA筛选示例  图3 SBA筛选示例 当无法获得6个批次的数据时,可以根据表征数据或corner lot结果设定初始值,并在生产6个月后根据生产结果定期进行评审和更新。在稳定量产后,每年至少更新两次限值,或按照供应商和用户/客户之间的约定进行更新。 其他筛选方法介绍 除了以上AEC-Q标准提供的加严筛选方法外,还可以使用其他方法进行加严筛选。加严筛选的基本思想都是在晶圆上找到测试潜在失效DIE与其他DIE不同的特征,PAT和SBA/SYA方法主要体现在异常芯片在测试数值上的差异外,而以下筛选方法都是基于空间位置的异常值检测技术。实践表明,在失效芯片相关联的空间位置上,芯片存在异常的可能性增加。 (1)ZPAT测试 在晶圆测试阶段,X、Y坐标定义了一颗DIE在晶圆上的具体位置。而对于一个晶圆批次25片wafer,将所有wafer重叠,其wafer号就相当于每一颗DIE的Z坐标。在同一晶圆批次中,如果出现多片wafer在同一X、Y坐标下的DIE均出现失效,可以认为属于Z方向失效。当同一批次25片wafer中同一X、Y坐标下的失效数量大于ZPAT阈值,需要将整个lot所有wafer的该坐标DIE全部判做fail,如图4所示,1、2、3、5、6、7号晶圆出现聚集型失效,对于同一坐标下的其他好DIE也要全部判作fail。此失效模式主要筛选出与掩膜工艺相关的失效。  图4 ZPAT失效示例 (2)GDBN测试 GDBN测试(Good DIE Bad Neighbor)基于这样一个理念,缺陷总是趋向于集中出现在晶圆的某些特定位置上。实践经验认为,在晶圆测试中,若存在一颗测试好品DIE周围DIE几乎都测试fail,那么这颗好品DIE存在可靠性和质量风险会上升。因此,需要通过图像识别每颗测试好品DIE周围DIE的失效情况,若周围DIE失效数量大于GDBN阈值,则该颗好品DIE也需要算作坏DIE。图5是典型的GDBN失效形状示例。  图5 GDBN失效形状示例 (3)Scratch测试 在晶圆测试中,由于生产工艺相关问题,可能导致出现线形的划伤失效,该失效也需要通过测试图形进行识别。如果一颗好品DIE存在于划伤路径上,也认为其具有潜在质量风险,需要作为失效DIE处理。图6标示典型的scratch失效图形。  图6 scratch失效形状示例 (4)Cluster测试 在晶圆测试中,由于生产工艺相关问题,可能出现环形或区域形的集中失效,因此,如果一颗好品DIE存在于区域性失效边缘,也认为其具有潜在质量风险,需要作为失效DIE处理。图7标示典型的cluster失效图形。  图7 cluster失效形状示例 以上图形化的加严筛选方法并不在AEC-Q标准范围内,且目前并没有统一标准,具体的筛选方法根据实际需求制定,并使用软件进行自动化分析。 选流程介绍 针对晶圆测试和封装测试,以上筛选方法均适用,但由于两个测试阶段特性的不同,筛选流程有很大的差别。 在晶圆测试阶段,每颗DIE具有唯一的X、Y坐标,需要将测试数据和测试map导入到自动化处理软件中,通过上述算法生成最终的inklessmap用于拾片和封装工艺。在封装测试阶段,由于芯片没有对应的坐标文件,因此需要在封装测试期间在测试文件中打印工厂码等用于记录坐标的信息,用于与实际的芯片进行一一对应。将封装测试的测试数据导入到数据库中,通过算法筛选出不符合AEC-Q标准的芯片,将筛出的芯片工厂码打印成失效芯片记录文件,在最终的筛选测试流程中使用自动化测试设备筛出,完成封装阶段的筛选。 晶圆测试阶段流程如图8所示:  图8 晶圆测试筛选流程 由于封装测试的时效性问题,不再进行与图形相关的ZPAT、GDBN、scratch、cluster测试。 封装测试阶段流程如图9所示:  图9 封装测试筛选流程 经过以上测试,筛选出的合格芯片符合AEC-Q100标准统计处理要求。保证了出货芯片在一致性和稳定性上得到质量提升。 测试结果及研究方向 在晶圆测试阶段,通过全流程测试后各测试项目的测试结果如图10所示。  图10 晶圆测试筛选结果 在封装测试阶段,通过全流程测试后各测试项目的测试结果如图11所示。  图11 封装测试筛选结果 以上筛选结果,符合AEC-Q100标准要求,实现了符合AEC-Q100标准的筛选测试方法。 该方法在实现AEC-Q100筛选功能的基础上,存在着进一步优化的空间,以下是后期研究的方向: (1)PAT筛选需要对所有的测试数据进行统计分析,在自动化处理过程中,占用巨大的存储空间,如何有效优化数据,减少存储量,是后期研究的一个方向。( (2)不同自动化测试机台数据格式差异大,对不同机台的数据格式进行处理和统一,能够有效提高数据导入的效率。 (3)基于空间位置的异常点检测算法中,cluster和scratch的算法目前较为原始,引入图像识别技术对划痕、点状、环状失效进行识别是后期研究的一个方向。 结语 本文介绍了符合AEC-Q100标准的车规芯片筛选方法,首先对AEC-Q100汽车芯片质量标准体系进行了概述。之后介绍了符合AEC-Q001和AEC-Q002标准的基于统计学的筛选方法PAT和SBA\SYA,补充介绍了基于空间位置的异常点检测方法。针对晶圆测试和封装测试的不同情况,分别介绍了实际的筛选流程。该方法已成功应用于车规芯片筛选测试当中。 |