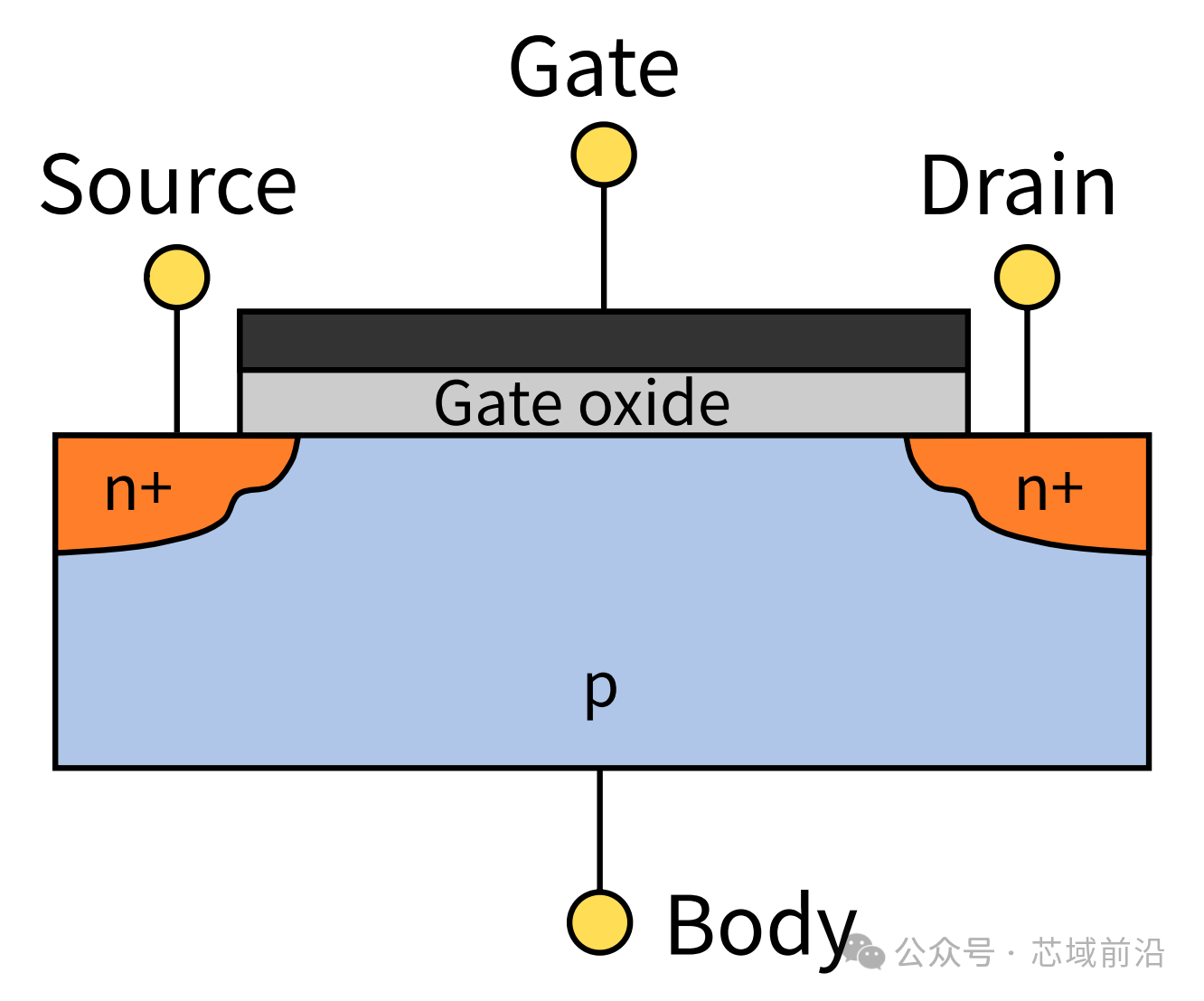

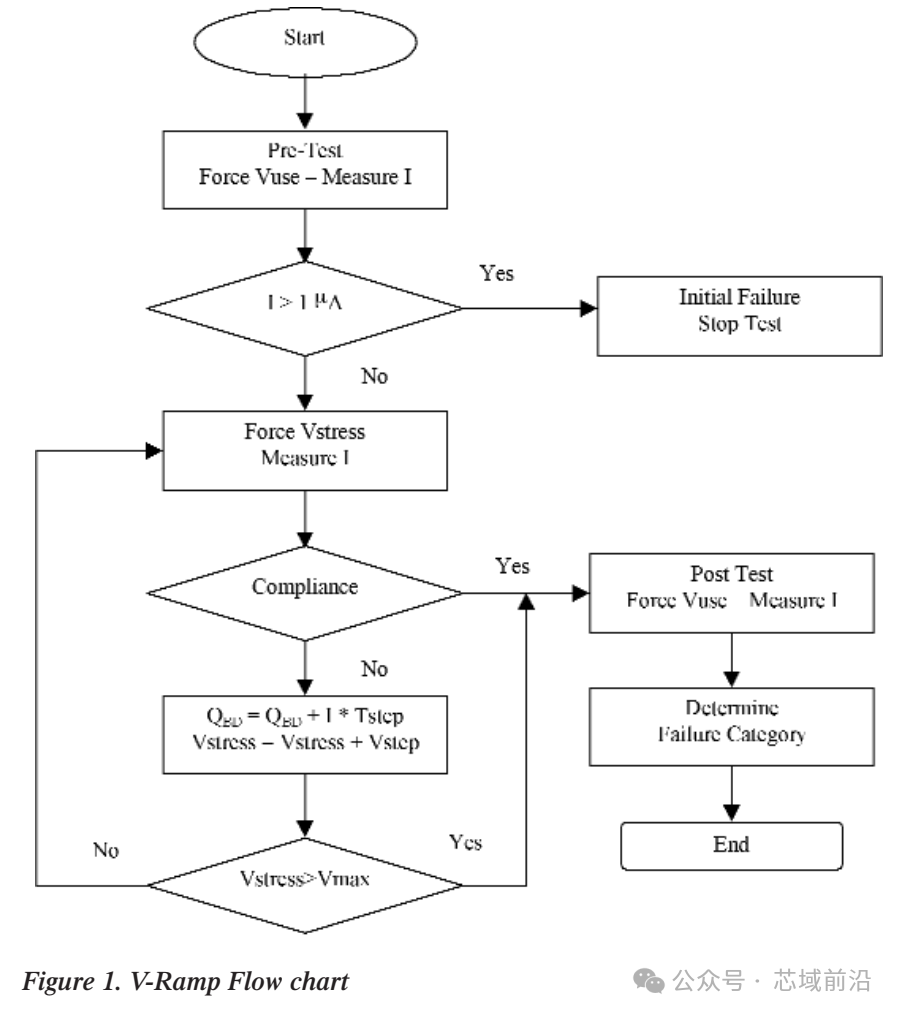

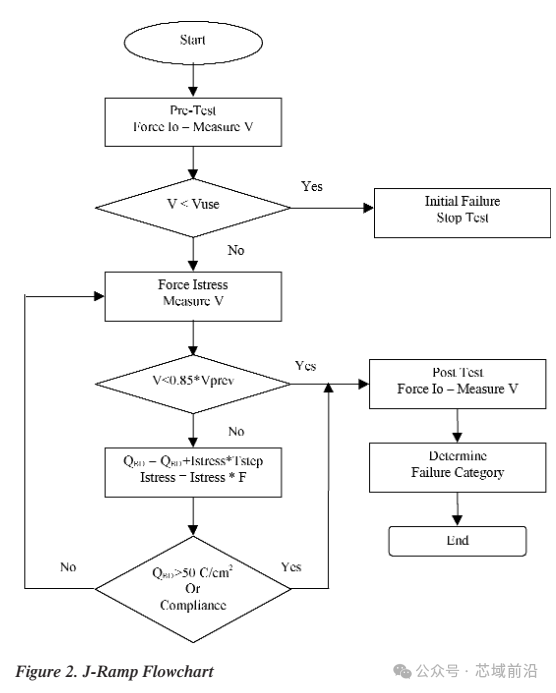

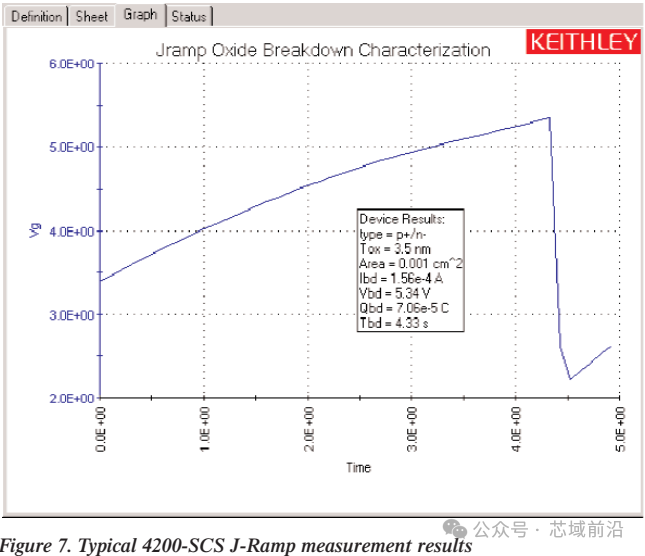

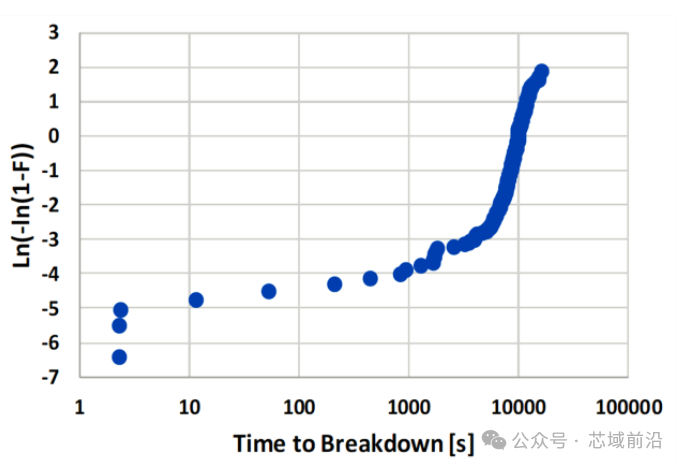

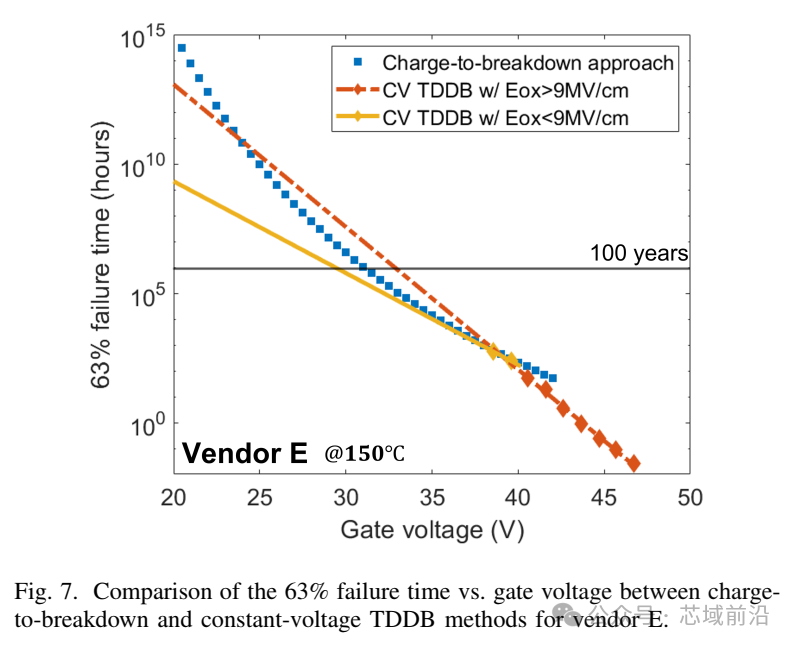

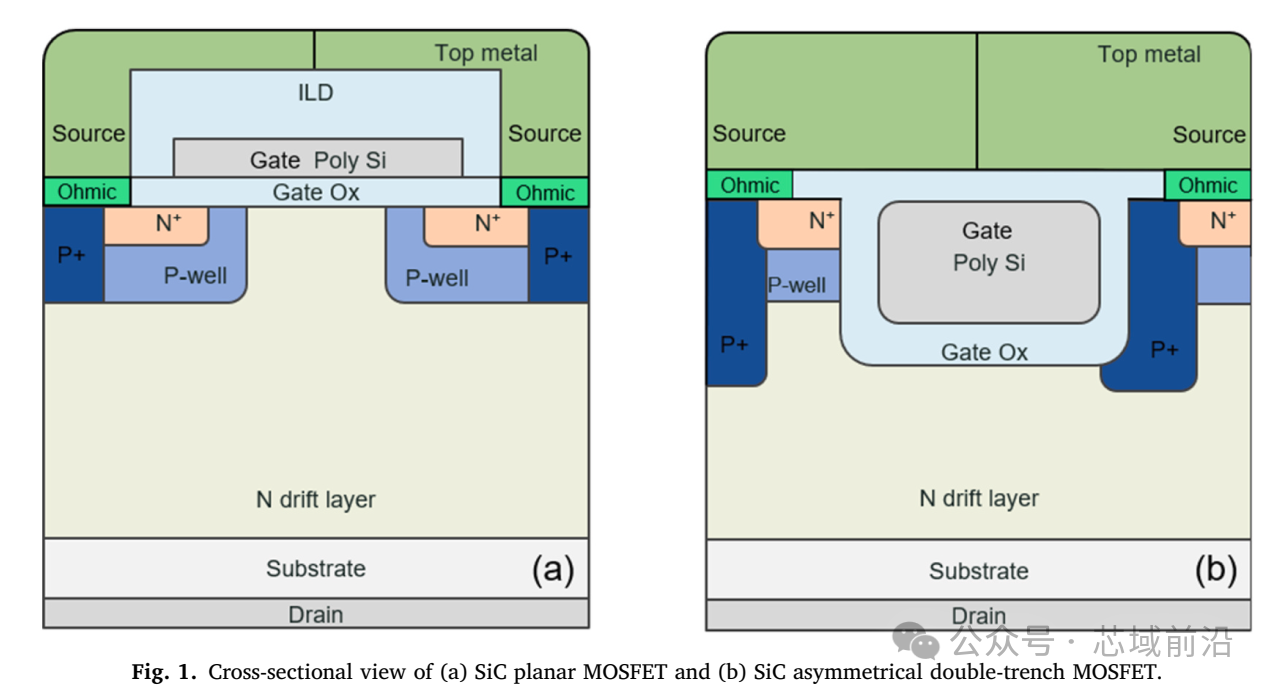

一颗芯片能不能活过十年,工程师往往先看这两条斜坡:V-ramp与J-ramp全解JEDEC(Joint Electron Device Engineering Council,电子器件工程联合委员会)JESD35 把 V-ramp(Voltage Ramp,电压斜坡)和 J-ramp(Current Ramp,电流斜坡)定义为薄介质晶圆级快速评估方法,它们的核心作用不是“把芯片测坏”,而是用尽可能短的时间,看清这层氧化物到底稳不稳、散布大不大、有没有早夭风险。 作者分享了几篇相关资料,感兴趣的小伙伴可以在公众号【芯域前沿】对话框输入:326,获取资料研读。  01为什么半导体工程师会对“栅氧”如此紧张? MOS(Metal-Oxide-Semiconductor,金属-氧化物-半导体)器件的妙处,在于栅极和沟道之间隔着一层绝缘氧化层。 理想状态下,这层膜既要足够薄,保证栅控能力强、器件开关快;又要足够稳,保证在电场、温度和长期应力下不漏、不漂、不击穿。 问题就在这里:氧化膜一旦出现局部缺陷、陷阱累积、隧穿电流异常,失效往往不是“慢慢坏”,而是会走向突发性的介质击穿。 最新综述也指出,介质击穿依然是电子器件里最核心、也最复杂的可靠性问题之一,实验数据很多,但微观机理并没有被“彻底讲完”。 如果说 TDDB(Time-Dependent Dielectric Breakdown,时依介质击穿)更像“长期寿命考试”,那 V-ramp 和 J-ramp 更像“高效率入厂体检”。 前者擅长回答“在工作应力下它能活多久”,后者更擅长回答“这批氧化层是不是有弱点、散布是否异常、工艺窗口是否飘了”。 也正因为 TDDB 尤其在低电场下测试时间很长,制造端才会高度依赖 ramp 类测试做快速反馈。  02V-ramp到底在测什么?本质上是在“匀速升压,看它什么时候撑不住” V-ramp 的逻辑很直观:先对样品做一次预检,在使用电压 Vuse 下测一遍泄漏;如果器件初始状态正常,就按线性电压斜坡不断升高栅压,直到氧化层失效。 按照 Tektronix 的应用说明,V-ramp 常见的击穿判据包括:氧化层电流突然升到预期值的约 10 倍,或者电流超过预设 compliance(限流)门限。 测试结束后,再回到 Vuse 做一次后测,判断最终失效状态,并提取 VBD(Breakdown Voltage,击穿电压)与 QBD(Charge to Breakdown,击穿电荷)。 它为什么叫“电压斜坡”,却又经常被理解成“电场筛子”? 因为在薄氧化层里,电压最终会折算为 Eox(Oxide Electric Field,氧化层电场)。 JEDEC 规范对步进高度和斜坡速率都有要求,Tektronix 的示例甚至明确给出了 0.1 MV/cm 的最大电压步高要求以及 1 MV/cm·s 的最大 ramp rate(斜坡速率)要求。 换句话说,V-ramp 不是随便往上扫,而是要在“步进均匀、时间精确、位移电流可控”的前提下,让数据真正能用于工艺判断。 工程上,V-ramp 之所以常被用来观察 infant mortality(早夭失效)和低电场缺陷,是因为它从较低氧化层电压起步,对低场弱点更敏感; 而且它常用于面积较大的测试结构,更容易把外在缺陷引发的尾部问题“放大出来”。 这也是很多逻辑工艺、较大面积薄栅氧结构偏爱 V-ramp 的原因。  03J-ramp: 它是在“按电流抬坡,看电压何时塌陷” J-ramp 的起手式和 V-ramp 很像,也要先做完整性预检;但它真正施加的不是线性升高的电压,而是不断增长的对数电流阶梯。 Tektronix 的说明给得很具体:预检阶段常用约 1 μA 恒流,看氧化层能否建立起正常电压;通过后,再按 Istress = Iprev × F 的方式逐级提高电流,其中 F 小于 3.2。 当测得的氧化层电压相比前一步下降 15% 以上,或累计电荷超过限制,就判定击穿。 它同样能提取 VBD、QBD 和 TBD(Time to Breakdown,击穿时间)。 J-ramp 的关键优势在于,它从相对更高的氧化层电压状态进入测试区,因此对高电场区域的分辨率更好。 JEDEC 35 对 J-ramp 还给出了一条常被工程师引用的节奏要求:current ramp rate(电流斜坡速率)为 one decade/500 ms,即每 500 ms 增加一个 decade(十倍电流量级)。 这也是为什么 J-ramp 经常被用在更小的 scribe-line(划片道)测试结构,或者被认为更适合观察本征失效路径。 如果用一个更容易传播的类比来讲:V-ramp 像是不断抬高堤坝外的水位,看大坝何时决口;J-ramp 则更像是强行把越来越大的流量压进管道,看系统内部什么时候电压支撑不住。两者都在找“弱点”,但寻找弱点的受力路径不一样。  04工程师拿到斜坡测试结果,真正盯的是哪几个数? 最常见的三个量是 VBD、QBD 和 TBD。 · VBD 很好理解,就是击穿那一刻对应的电压; · QBD 不是“某一个瞬时电流值”,而是从应力开始到击穿为止,穿过氧化层的累计电荷; · TBD 则是击穿时间。 对制造工程来说,这三者不是谁更“高级”,而是谁更适合回答当下问题:要做快速筛选、工艺对比、面积效应分析,还是要做寿命外推、风险保守评估。 而真正让数据有工程意义的,往往不是单点数值,而是 Weibull Distribution(Weibull 分布,威布尔分布)上的整条分布曲线。 曲线的斜率、尾部、批间偏移,能反映这批氧化层是“整体偏弱”,还是“少量坏点拖尾”,是工艺均匀性出了问题,还是清洗与界面控制出了隐患。 NIST 论文展示了典型的 TDDB Weibull 分布中外在失效长尾问题; 而 0.18 μm CMOS 工艺研究则指出,测试方法对 VBD 的影响很小,但对 QBD 的影响很大,且 J-ramp 得到的 QBD 往往明显大于 V-ramp,QBD 的 Weibull 斜率也明显小于 VBD,这意味着在那类工艺条件下,VBD 往往是更稳健的比较指标。这也是很多初学者最容易误判的地方:看到 QBD 大,就以为“这个氧化层更耐打”;其实不一定。因为 QBD 对测试路径、时间控制、应力条件非常敏感,跨方法、跨条件直接横比,很容易把“测法差异”看成“工艺差异”。  05V-ramp和J-ramp,谁更适合谁?没有绝对赢家,只有问题导向 从 JEDEC、Tektronix 和 HP 的应用经验看,V-ramp 更擅长暴露低电场、较大面积结构上的异常尾部,因此常被拿来观察早夭和外在缺陷; J-ramp 则更适合高电场分辨率更高的场景,常用于更小测试结构、偏本征失效模式的观察。 简单记忆就是: V-ramp 更像“把低场弱点筛出来”,J-ramp 更像“把高场承受能力看清楚” 。 但真正成熟的制造体系,几乎从来不会把两者当成“二选一”。 它们更像两支角度不同的探针:一支先看尾巴,一支再看核心;一支适合快筛,一支适合补分辨率。 真正决定寿命承诺的,依然要回到 TDDB 这类长时应力测试。也就是说,ramp 测试擅长做“前线侦察”,TDDB 才是“寿命判卷”。  06工程师是怎么把“斜坡图”读成“工艺语言”的? 对制造端来说,最有价值的不是一句“通过/不通过”,而是分布为什么会长成那样。 HP 的应用文档就明确提到,QBD 和 VBD 往往来自大量测试结构,并最终被画成累积失效分布图;理想制造过程追求的,是让分布逐步逼近更理想、更收敛的形态。 换句话说,工程师看的是“这条分布曲线在说什么工艺故事”:是氧化均匀性变差了,还是清洗引入了尾部缺陷,还是量测时序本身不够稳定。 NIST 的研究则提醒了另一个更深的点:不同缺陷模型下,ramp 测试读出来的“坏”并不一定对应工作电压下同样的坏。 尤其在所谓 lucky defect(“幸运缺陷”)模型下,某些缺陷会在特定能级和空间位置上显著增强 Trap-Assisted Tunneling(TAT,陷阱辅助隧穿),它改变的是局部电流路径,而不只是“单纯局部变薄”那么简单。 也就是说, 看图归因不能只靠一条曲线拍板 ,往往还要结合失效分析、版图面积、氧化工艺、TDDB 与器件应用场景综合判断。  07为什么今天再谈V-ramp和J-ramp,越来越绕不开SiC和TDDB? 当器件从传统硅逻辑不断扩展到 SiC(Silicon Carbide,碳化硅)功率器件时,栅氧可靠性的重要性被进一步放大。 OSU 的公开研究显示,在 150 °C 条件下,商用 SiC 平面栅 MOSFET 与沟槽栅 MOSFET 的平均栅氧击穿电压大约分别为 51 V 和 75 V; 如果按 11 MV/cm 的临界击穿场估算,对应氧化层厚度大约是 46.4 nm 和 68.2 nm。 更厚的氧化层意味着更高的可接受 screening(筛选)电压,但并不意味着可以无限度“猛筛”。 更关键的是,OSU 对 SiC 功率 MOSFET 的寿命比较还表明:constant-voltage TDDB(恒压 TDDB)在较低氧化层电场下给出的寿命预测更保守; 如果在过高电场下做外推,hole trapping(空穴俘获)等效应会加速失效,反而可能把正常工作电压下的寿命看得过于乐观。 换句话说, ramp 测试可以很快,寿命结论必须很稳。 这正是为什么今天的先进功率器件评估,越来越强调 ramp、screening 和 TDDB 的组合使用,而不是单靠某一条斜坡曲线下结论。  08最容易被误解的三件事:快测不是寿命本身,斜坡也不是万能答案 1. V-ramp/J-ramp 不是寿命的直接同义词 。 它们是非常高效的可靠性指示器,但不是对真实工作寿命的一步到位回答。NIST 的结论已经非常明确:在特定缺陷机理下,V-ramp 对工作电压下的氧化品质未必给出有用信息,高场 screening 也未必能把弱器件真的筛干净。 2. 筛选电压越高,不一定越好 。 OSU 研究指出,过长时间的高栅压应力会抬高隧穿电流并伤害栅氧本征寿命,因此 screening 需要在效率和损伤之间找平衡,而不是一味把门槛往上拧。 3. 不要把不同方法下的 QBD 直接横向排名 。 0.18 μm CMOS 研究已经说明,QBD 对测法和条件敏感得多,VBD 反而更适合作为稳定比较基准。对读者来说,最简单的理解就是:一张曲线背后,既有器件物理,也有量测方法学;只看“数值大小”,很容易把工程判断带偏。 1. 说到底,V-ramp 问的是“升压到哪儿会坏”,J-ramp 问的是“增流到哪儿撑不住”,TDDB 问的是“在真实使用应力下它能活多久”。把这三个层次放在一起看,你看到的就不再只是两条测试曲线,而是一整套半导体制造对“良率、筛选、寿命、失效机理”的系统性理解。 |