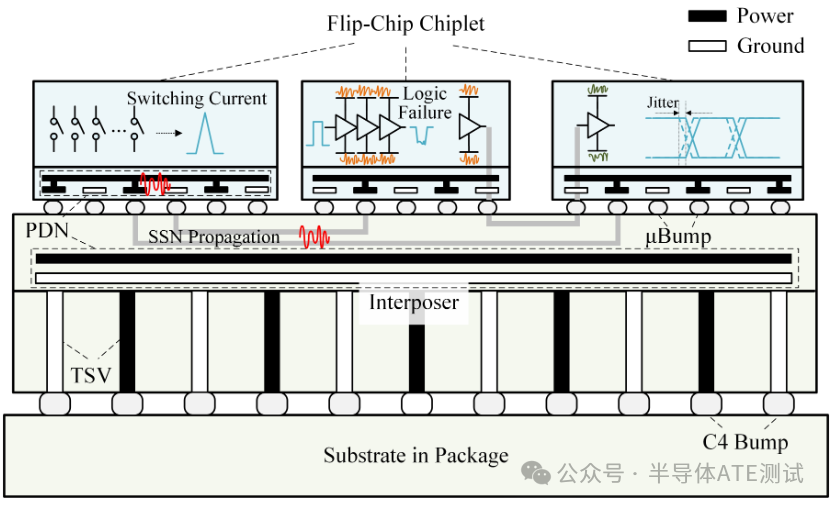

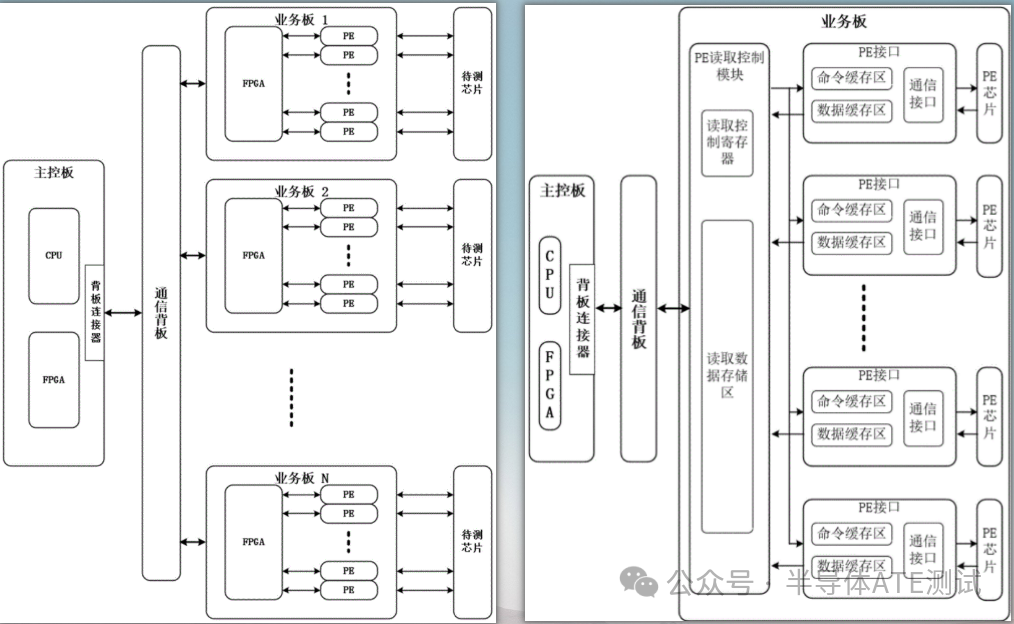

感恩科技的发展,AI 正在逐步改写我们的工作学习模式,Q4各家半导体设备厂商举办的技术峰会里,对AI的讨论也层出不穷。高速接口是谈及AI,一个无法绕过的话题。如今,数据传输速率已从兆赫兹级跃升至百吉赫兹级。尖端的高速接口,如:SerDes、DDR5、PCIe Gen6/7,它们是现代计算的性能基石,但测试它们的速度和精度,已经成为产品能否快速上市(TTM)和制造成(COT)的核心瓶颈。我们不得不正视一个残酷的现实:DUT数据传输的增长速度,如同脱缰的野马,传统的 ATE 架构和测试方法论正在被“甩在身后”,高频高速带来的物理极限——信号完整性(SI)与电源完整性(PI)的挑战,以及海量数据吞吐压力,正不断挤压着测试的边界。本文将尝试解读这场半导体测试领域的“速度与激情”,从高速测试PCB PI&SI约束及限制,笔者了解到的最新ATE系统架构,ATE+SLT+AECQ一体化测试方案,这三个方向进行剖析,争取能窥探这场架构和效率革命一二。 一. 高频高速测试:负载板SI 与 PI 约束探索  1.1 PAM4 的“三只小眼睛”:信号容忍度的崩塌危机为了在有限的带宽内传输更多数据,行业不得不采用更复杂的调制方式。从非归零码(NRZ)到四电平脉冲幅度调制(PAM4)的转变,是带宽“压榨”技术的典型代表。PAM4:通过四个电压电平在同一周期内传输两个比特,理论上速度翻倍了,但这真是免费的午餐吗?代价就是信号容忍度(Signal Margin)的急剧下降。PAM4 将信号的垂直裕度压缩成了传统 NRZ 的三分之一 1。这意味着,眼图被“压扁”成了三只小眼睛,对噪声和抖动的容忍度比以往低得多1。随着数据速率飙升,位错误率(BER)对于设计和测试的容错空间变得越来越小。当测试精度必须追上信号幅度的衰减速度时,任何微小的误差都会被放大,否则你测出的结果就是“盲人摸象”,毫无意义!先进的数字协议(如 PAM4、PAM8)对信号质量变化的容忍度极低 1,这迫使 ATE 设备必须具备更高带宽、更低噪声和更精细的抖动分析能力 1.2 SI 的“隐形杀手”:PCB 走线与“残铜桩”的噩梦高频高速信号在PCB上传输,如同在城市的“高速公路”上行驶,面临着物理世界的种种“陷阱” 。 首先是 PCB走线的困境。随着芯片集成度提高,PCB 上的元器件密度也随之增加,走线必须变窄。窄迹线比宽迹线更有可能成为阻抗不连续的“断崖”。元器件密度的增加还使得走线间的空间越来越小,这直接导致了串扰(Crosstalk)风险急剧上升。串扰是由于感应磁场或寄生电容导致的,你的信号在传输时被邻居的“噪音”吵到了! 这种信号间的“噪音污染”严重恶化了信号质量。 其次是Via Stub(残铜桩)的“噩梦”。传统的贯穿性 Via(通孔)在多层板中连接不同层,但通孔底部未使用的部分会形成一段“线头”。这段“残铜桩”在高频下会成为一个谐振腔,引起严重的信号反射,破坏眼图 。 例如,对于 Nyquist 频率大于 10GHz 的 PAM4 信号,Via Stub 长度被要求小于10mils。为了消除这些影响,必须采用更复杂的制造工艺,如背钻技术(BackDrilling)。背钻能移除通孔底部的残铜桩,但这不仅增加了 PCB 成本,更要求你的 ATE Loadboard 必须达到近乎完美的 SI 标准,否则ATE测的只是负载板! 1.3 PI 的“隐形地基”:目标阻抗与 VVI 的最终防线如果说 SI 是保障信号清晰的“高速公路”,那么 PI(Power Integrity,电源完整性)就是保障这条公路拥有稳定“电力供应”的“地基”。在高速测试中,数字芯片的瞬态电流需求巨大且变化剧烈,任何电源网络的噪声都会直接耦合到信号线上。你的信号之所以“摇摇晃晃”,可能就是“地基”不稳。电源分配网络(PDN)设计必须满足一个核心原则:目标阻抗(Target Impedance)。在频域内,PDN的阻抗在器件工作频率范围内必须低于这个目标阻抗。只有满足目标阻抗要求,才能保证电源轨上的电压波动(Ripple)在可接受的范围内。 为了“打好地基”,**去耦电容(Decaps)**的选择和放置至关重要。 1.Decaps 的选择: 必须利用基于零点和极点的特殊算法,确定使用最少数量的电容来实现目标阻抗,否则就是过度设计,徒增成本! 2.Decaps 的放置: 在频域优化中,目标是优化 Decaps 的物理放置以降低 PDN 阻抗。 然而,即使经过频域优化,时域中的电压违规(Voltage Violations) 仍然可能存在。因此,资深工程师必须进行瞬态电流仿真,并引入电压违规积分(VVI) 作为关键度量。VVI 能够量化电压波动对系统的影响,通过策略性地增加 Decaps 来缓解时域上的电源噪声问题,这是确保数字系统长期可靠工作的“最终防线。 二. 高频高速测试:ATE系统架构变革 2.1 ATE 的“I/O 延迟陷阱”:为何你的测试程序跑不快?传统ATE架构的效率瓶颈,在于其高度依赖主测试程序对硬件资源的集中控制。在测试流程中,程序需要频繁地、串行地访问数量众多的引脚电路芯片(PE)来完成配置和读取数据 2。这种串行、低效的 I/O 访问机制,造成了配置和读取时间的显著延长。随着数据率和通道数的几何级数增长,主程序与 PE 芯片之间的 I/O 延迟,成为了缩短芯片测试时间的主要障碍。 现场可编程门阵列(FPGA)的引入,为解决这一效率困境提供了新的解决思路。 数据并行读取: 通过在ATE业务板上部署 FPGA,将其配置为一个专用的、高效的 I/O 管理器 。FPGA 在预设时间间隔内,能够并行地读取该业务板上所有 PE 中的测试数据,并将数据批量存储在板载缓存中 2。 批量访问: 传统的测试程序现在无需再与速度较慢的PE芯片进行频繁的串行通信。相反,程序只需与高速的 FPGA 进行一次或少数几次通信,以批量获取所有测试数据 2。 这种架构上的转变,大幅减少了测试程序对 PE芯片的访问次数,直接缩短了芯片测试时间,提高了芯片测试效率2。更令人兴奋的是,这种效率提升通常无需做昂贵的硬件调整,只需对业务板上的 FPGA 进行设计升级,此举极大的提高了ATE 设备的性价比。  传统 ATE 串行 vs. FPGA 并行读取 三. 复杂DUT的测全面测试:从“功能验证”到“系统信任” 随着芯片复杂度提升,特别是对于高性能计算、国防等对可靠性要求极高的应用,传统的 ATE 功能测试已经远远不够。我们无法确保在ATE Pass 的芯片在上客户系统板后仍能在复杂多变的环境下长时间稳定的工作。 这是因为:基于ATE 的功能测试,只能将配置后的DUT 作为普通逻辑器件进行参数与功能测试。然而,这种方法存在一个致命的局限性:ATE只能实现功能测试,无法实现DUT 的兼容性、散热、稳定性和性能等关键的系统级测试。 因此,测试策略必须拥抱 系统级测试(SLT)和可靠性测试(AECQ) ,将 ATE 的高精度测量与 SLT系统稳定及AECQ的高压力验证结合起来,这是测试的“临门一脚”。可靠性测试需要遵循一套结构化的策略 3: 兼容性测试是保障芯片能顺利融入目标系统的基础。包括物理兼容性测试(尺寸、安装)和系统兼容性测试(驱动安装、操作系统识别)。 压力测试(StressTest):在安装驱动后,运行测试服务器上的压力测试软件 3,将器件推向性能极限(例如高带宽 I/O 吞吐)。找到器件的性能极限。 散热测试(ThermalTest):在压力测试运行过程中,必须实时查看DUT的实时温度。高温是半导体性能的头号杀手,散热测试确保了芯片在真实、恶劣的工作条件下依然能够可靠运行。 这种测试策略,标志着行业正在从追求“功能良率”转向追求“系统级信任”的质量观升级。 测试的未来,属于架构革命者!!!高频高速接口的挑战,已经将半导体测试推向了一个新的临界点。我们面临的不仅仅是速度问题,更是架构和方法论的系统性变革。 本文简要分析了解决现代测试困境的三大支柱: SI/PI 物理保障: 从 Back Drilling 到目标阻抗VVI,将信号与电源的稳定性武装到牙齿。 分布式架构革命:利用 FPGA 实现系统级加速,通过数据并行读取机制,彻底解决传统 ATE 架构中I/O 延迟导致的效率瓶颈。去中心化的数据管理,是未来测试系统的趋势。 系统级可靠性验证:采用SLT,AECQ混合测试策略,实现从“功能验证”到“系统可靠性工程”的质量观升级。 测试不再是孤立的一环,而是与设计、制造、系统验证深度融合的生态系统。我们正在从简单的功能测试转向全面的系统级信任工程。拥抱FPGA加速和SLT策略,是当前半导体从业者的必修课。高频高速的世界,挑战与机遇并存,愿我们都能紧跟科技发展步伐,不断探索新的认知边界~ |