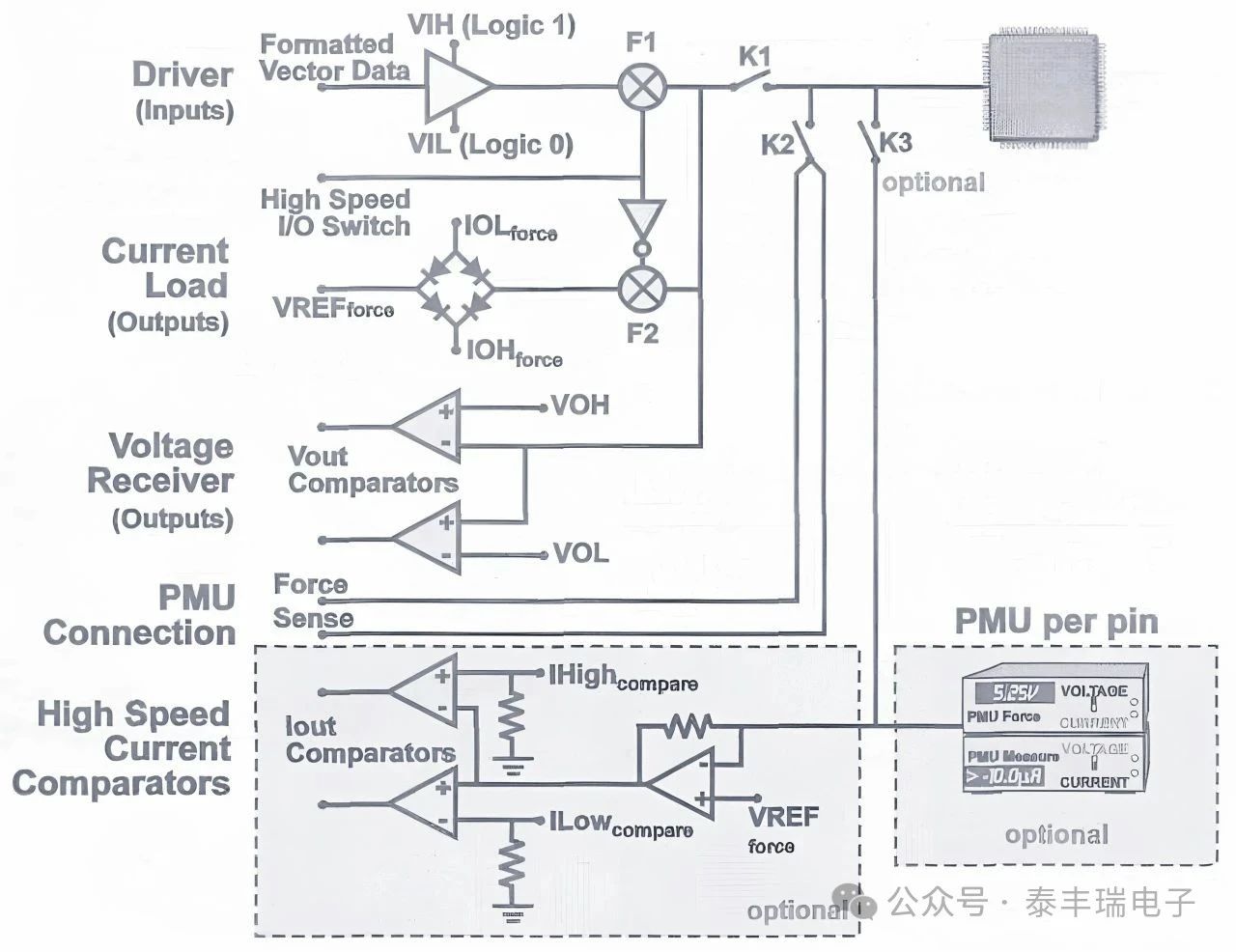

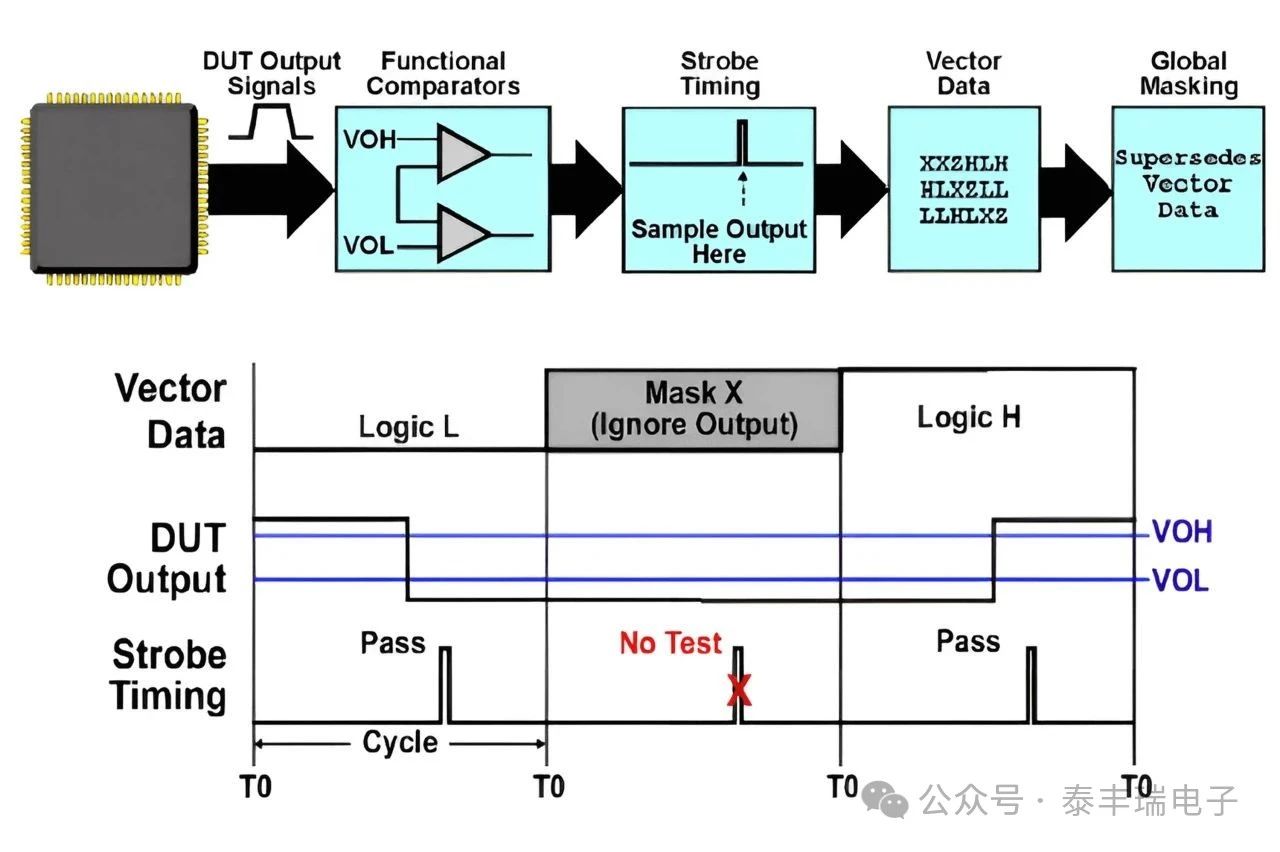

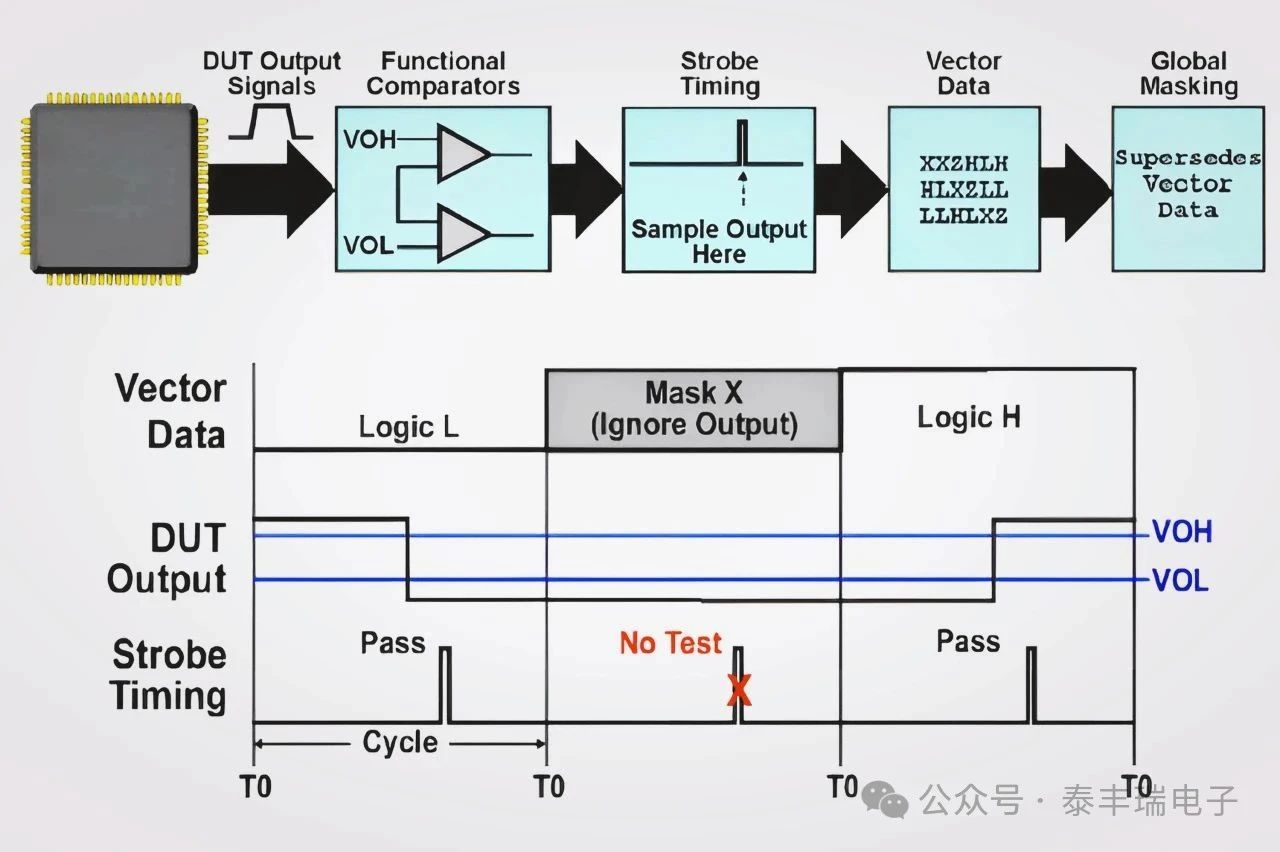

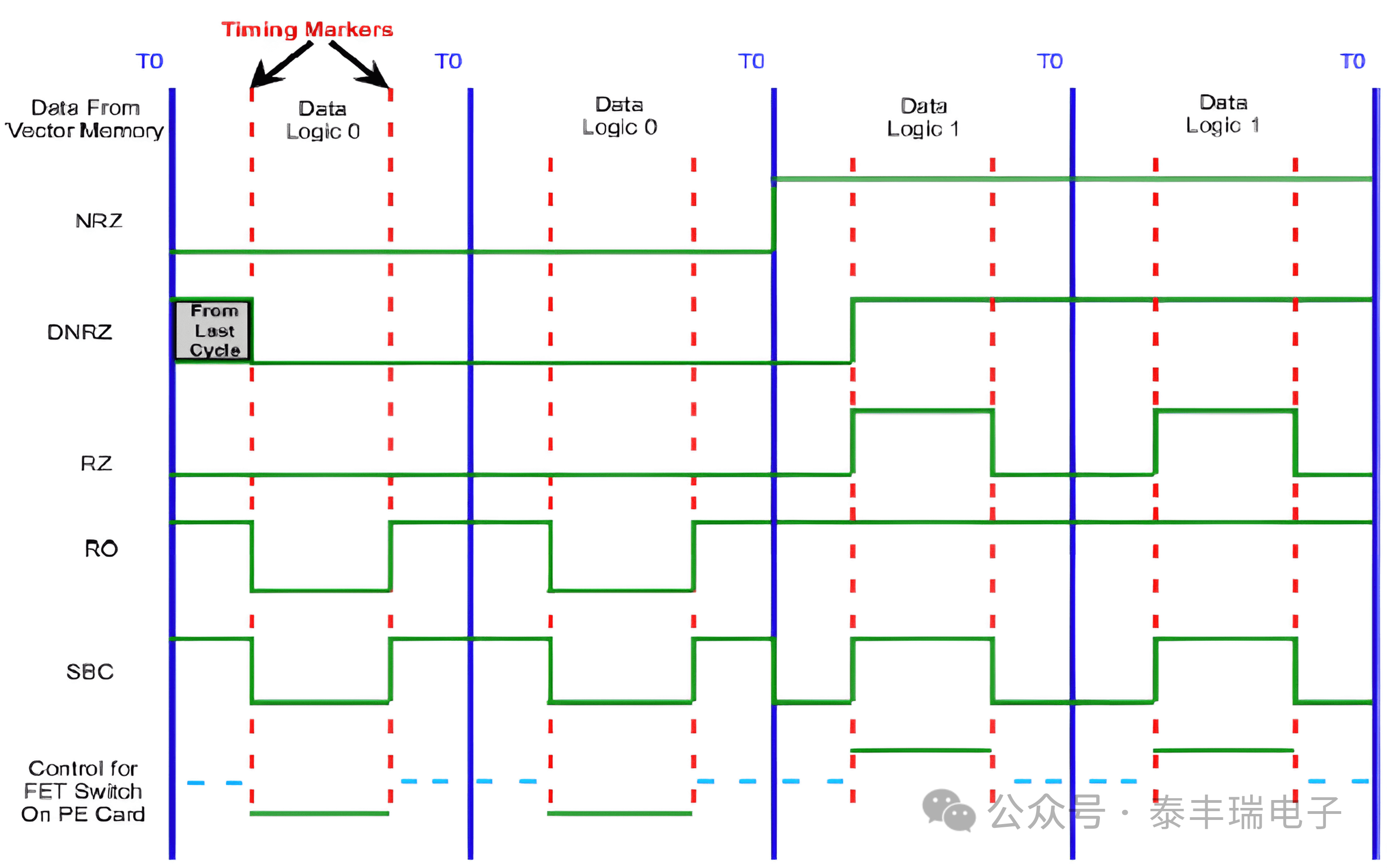

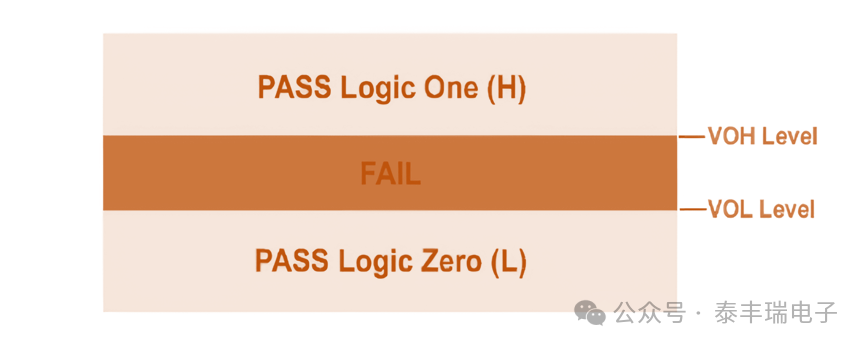

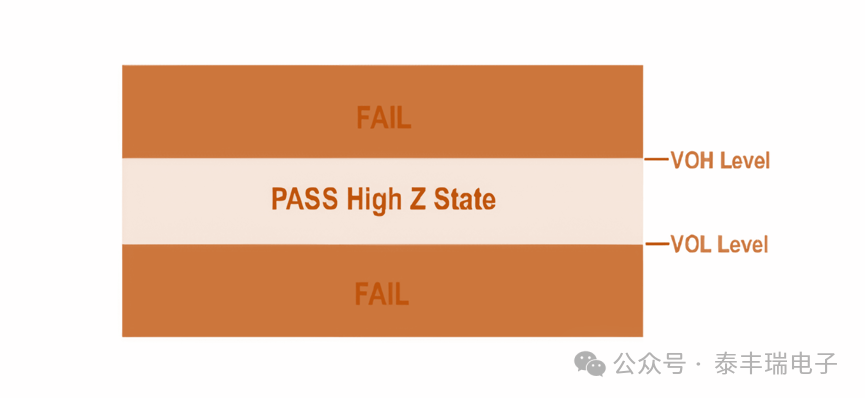

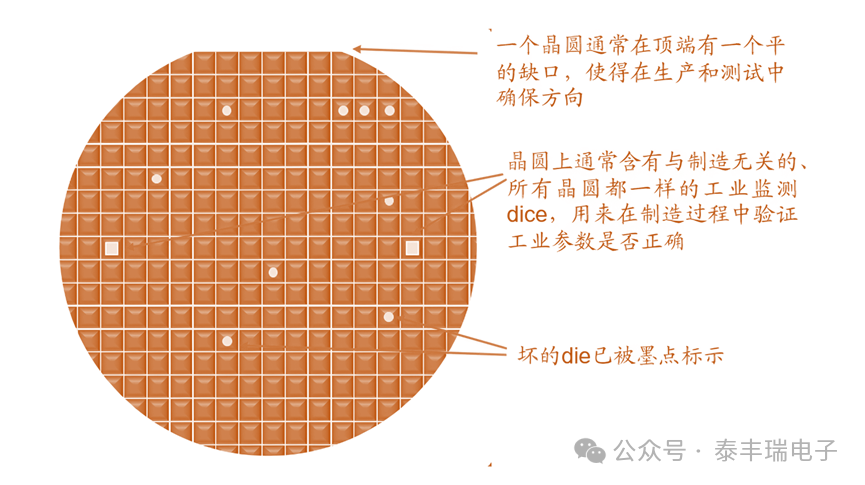

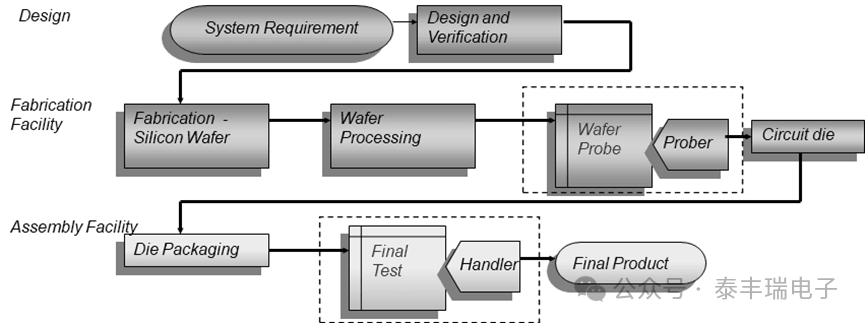

半导体测试 - 基本概念随着芯片集成度越来越高,手动测试已无法满足需求,因此要用到自动化测试设备(ATE,Automated Test Equipment)。因为现在的芯片原来越复杂,普通的 Bench 测试没法满足需求。ATE 可检测集成电路功能之完整性,是集成电路生产制造最终的流程,确保产品质量。芯片测试算是半导体产业链上游里面最末端的一个组成部分。受测试的器件主要分几类:储器、数字电路、模拟电路和混合信号电路。 ATE 内部有很多子系统,包括提供高低电平的驱动电路、可编程的电流负载、检测输出电压的比较器、PMU 连接电路、高速电流比较器、高速开关等。  ATE 测试系统图 从上图可以看出,测试系统主要由输入、输出和动态负载三部分组成: 1.输入部分 给 DUT 提供 VIL/VIH 电压 2.输出部分 将 DUT 的输出电压与 VOL/VOH 作比较 3.动态负载 通过加载 IOL/IOH 电流,得到输出电压,与 VOL/VOH 作比较 直接将输出电流与 ILow/IHigh 作比较(一般高端机台才有) 测试最基础的是测 DC 和 AC 参数。DC 参数用的方法可以是 Static,就是用 PE 卡的 Driver 和 PMU,然后 Force V Measure I 或 Force I Measure V ;也可以用 Functional 的方法,就是 Current Load 和 Voltage Comparator,然后跑 Pattern 来测试。 信号的输入与输出 信号是如何生成并输入 DUT 的:  信号是如何从 DUT 读出并测试的:  输入信号的格式  · RZ(Return to Zero):归零码,在一个周期内用二进制传输数据位,当数据位脉冲结束后,需要维持低电平。这种编码能同时传输时钟与数据信号,但因为一部分带宽被归零占用,所以传输效率相对不高。上升下降沿的位置可受 Edge Timing 控制。 · RO(Return to One):归一码,与 RZ 相反,需要维持在高电平。上升下降沿的位置可受 Edge Timing 控制。 · NRZ(Non Return to Zero):不归零码与 RZ 的区别是它不必归零,所以一个周期可以全部用来传输数据,带宽利用率 100%。如果传输低速异步数据,可以不加时钟线,但要约定通信波特率(如 UART);传输高速同步数据,需要另外配时钟线。NRZ不受 Edge Timing 的控制。 · DNRZ(Delayed Non Return to Zero):延时不归零码是 NRZ 加了时间延迟的波形。延时的时间受 Edge Timing 控制 · SBC(Surrounded By Complement) :补码环绕相当于 RZ 和 RO 的叠加。它每个周期内最多可以有 3 个边沿,在 T0 时反转数据,延迟一定时间后表现为预设的值,维持一定时间后又反转回去。SBC 多用于建立 / 保持信号的控制。 · ZD(Impedance Drive):阻抗驱动用于控制引脚开启或关断(高阻态)。 时钟信号通常使用 RZ/RO 格式,上升沿有效的信号(如片选 CS 或读 READ)常使用 RZ 格式;下降沿有效的信号(如输出始能 OE 常使用 RO 格式;拥有建立和保持时间要求的数据信号常使用 SBC 格式;其他的输入信号则可以使用 NRZ 或 DNRZ 格式。 输入信号的格式 高低电平输出:  引脚输出高低电平逻辑时,高电平必须至少要比 VOH 高,低电平至少比 VOL 低。 高阻态输出:  DUT 引脚由外部负载将电压拉到 VOL 与 VOH 之间,不能输出电压电流。 负载电流输出 DUT 有些引脚可以输出负载电流。如果测试系统有可编程电流负载就可以直接测试,如果没有就可能要外加电阻测试。负载电流输出需要在 VOL/VOH 达标的情况下输出指定的 IOL/IOH 电流。 CP 测试与 FT 测试  CP(Chip Probe)测试是芯片还在 Wafer 阶段时,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试。FT(Final Test)是芯片在封装完成以后进行的最终测试。 测试设备 · DUT(Device Under Test):待测设备,外部信号通过 DUT 的引脚对其进行测试。也称为 UUT(Device Under Test)。 · DPS(Device Power Supplies):为 DUT 直接提供电压与电流的设备。 · PMU(Precision Measurement Unit):精密测量单元,用于精确测量器件的直流特性。 · PPMU(Per Pin Measurement Unit):每个引脚上都有 PMU 用于测量。 · DIB(Device Interface Board):设备接口板,也称 LOAD board。 · PIB(Probe Interface Board):探针接口板,用于 Wafer Probe。 · PDP(Prober docking plate):探针台对接板。 · PROBE CARD:带探针的 PCB,用于 Wafer Probe。 · BINNING:根据测试结果对 DUT 进行筛选。 · MANIPULATOR:支撑测试头并允许其向多个方向移动的结构。 · HANDLER:全称IC pick up and place handler,自动分选机,用于将 DUT 放置在测试头插座中的机械。 · PROBER:探针台,在测试探针下移动晶片的机械单元。 芯片设计与测试的流程  基本测试项目 接触/连续性测试(Contact/Continuity Test):检查器件引脚中开路 / 短路问题。 直流特性测试(DC PARAMETRICS TEST):验证设备 DC 电流和电压参数,包括 IDD。 数字功能测试(DIGITAL FUNCTIONAL TEST):测试 DUT 的逻辑功能。交流时序测试(AC TIMING TEST):验证 AC 规格,包括输出信号质量和信号时序参数。 混合信号测试(MIXED SIGNAL TEST):验证 DUT 的模拟和数字电路的逻辑。 其他的测试项:射频器件(RF Devices)汽车器件(Automotive Devices)存储器件(Memory Devices)电源管理器件(Power Management Devices)RFID 器件、高速数字器件(High Speed Digital devices)等的测试。 测试中的参数介绍 VCC:对 TTL 器件的供电。 VDD:对 CMOS 器件的供电。 ICC:对 TTL 器件的驱动电流。 IDD:对 CMOS 器件的驱动电流。 VSS:提供电源回流路径。 GND:参考电平,在单电源供电设备上常等价于 VSS。 IDD:从 CMOS 设备中消耗的电流。 ICC:从 TTL 设备中消耗的电流。 VIH:高电平输入时的最低电压限制(不会被识别成 0)。 VIL:低电平输入时的最高电压限制(不会被识别成 1)。 VOH:高电平输出时的最低电压限制(不会被识别成 0)。 VOL:低电平输出时的最高电压限制(不会被识别成 1)。 IIH:输入引脚逻辑为高电平时,允许的最大灌电流。 IIL:输入引脚逻辑为低电平时,允许的最大漏电流。 IOH:输出引脚逻辑为高电平时,驱动 / 拉电流(source)的大小。 IOL:输出引脚逻辑为低电平时,灌电流(sink)的大小。 IOZH:输出引脚逻辑为高电平且处于高阻状态时,允许通过的最大电流。 IOZL:输出引脚逻辑为低电平且处于高阻状态时,允许通过的最大电流。 Propagation Delay:从信号输入到输出信号发生改变的时间间隔。 Rise Time:从高电平的 10% 上升到 90% 所需的时间。 Fall Time:与上面相反 |