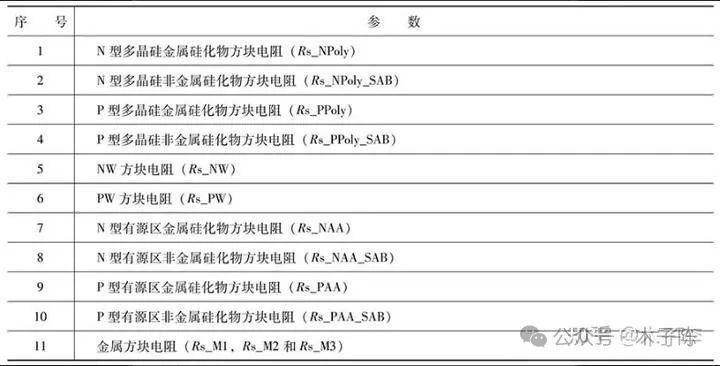

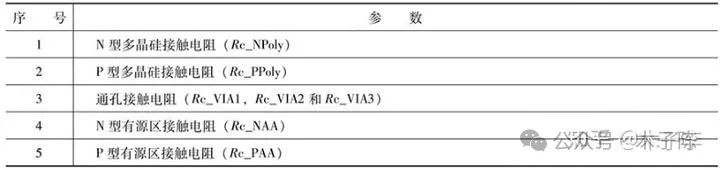

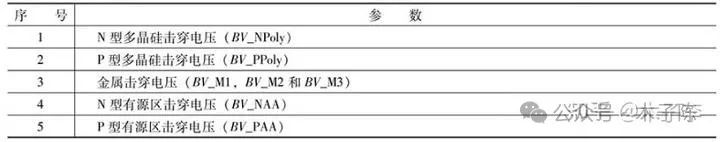

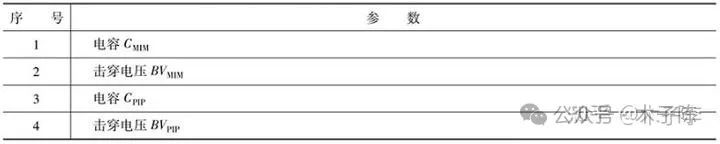

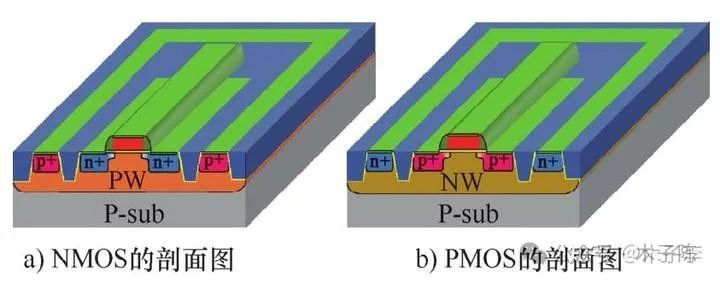

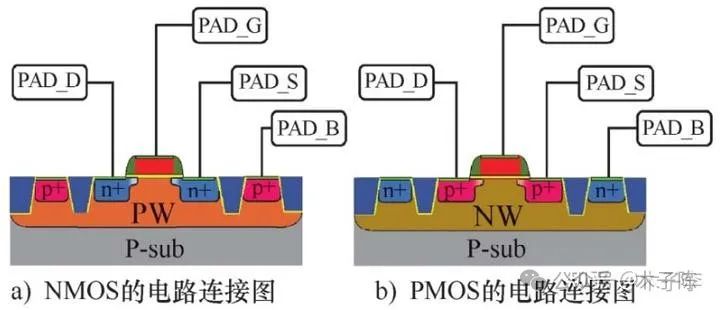

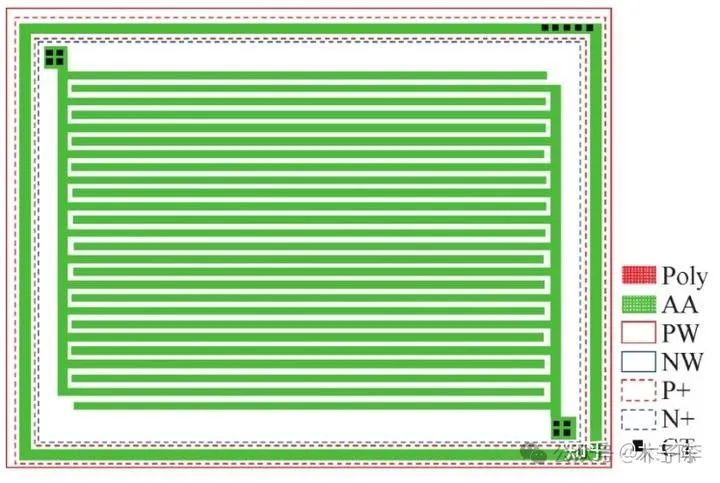

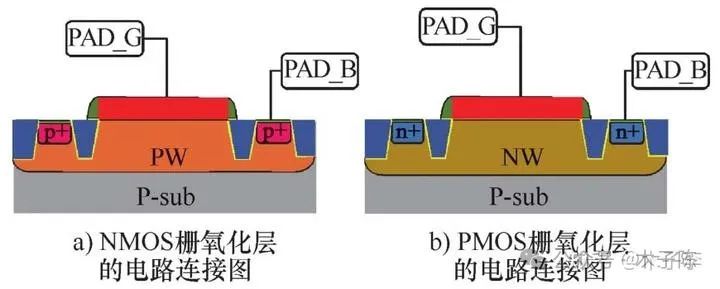

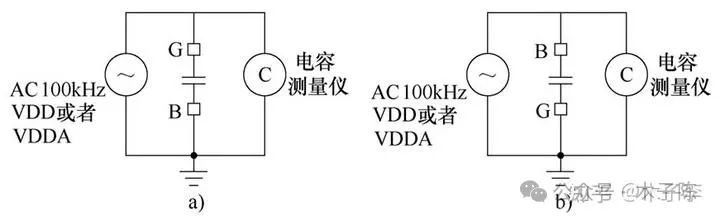

根据之前的介绍,相信大家对芯片出货之前必须做的WAT 测试有了基础的了解,今天就开始具体介绍一下上面文章提到的测试,并针对CMOS进行参数的分析,话不多说,下面就从CMOS制程中必不可少的MOS管开始。一.基础测试参数概述 1.MOS晶体管包括低压NMOS和PMOS,以及中压NMOS和PMOS,它主要测量阈值电压(Vt), 饱和电流(Idsat), 源漏击穿电压(BVD),漏电流(Ioff), 衬底电流(Isub). 2.栅氧化层完整性,主要测量参数有GOI电容(Cgox), GOI击穿电压(BVgox),GOI电性厚度(Tgox). 3.多晶硅栅场效应晶体管和第1层金属栅场效应晶体管,它的主要测量参数是多晶硅栅Vt_Poly_Field,第一层金属栅Vt_M1_Field. 4.n型结和p型结 , 结电容Cjun,结击穿电压BVjun. 5.方块电阻Rs,其主要测试参数如下表,  6.接触电阻Rc,其主要参数如下表,  7. 隔离,其主要测试参数为下表:  8. 金属电容和多晶硅电容,电容测试参数如下图,  以上参数都基于bulk wafer,随着集成电路制程工艺不断发展到纳米级以下,为改善器件性能,会引入不同的应变硅技术、HKMG技术、FD-SOI和FinFET技术。其中,MOS晶体管测试结构的版图尺寸都是按标准的沟道宽度和沟道长度来设计的,但由于不同工艺的特殊性,其器件的接法不同。对于常规Bulk wafer 来说,NMOS和PMOS的剖面图如图所示:  其4个端口栅(Gate)、源(Source)、漏(Drain)和衬底(Body)分别连到PAD_G、PAD_S、PAD_D和PAD_B,WAT测试机器通过这4个端口把电压激励信号加载在MOS晶体管,从而测得所需的电性特性参数数据。对于SOI器件,其Body接出来的方式与bulk不同。MOS是芯片中最重要的有源器件,其电性能非常重要,一般通过Vt、Idsat、BVD、Ioff和Isub来监测MOS管的性能。这里提到的都是DC测试,针对不同的应用场景会增加不同的测试,比如RF的器件会增加射频测试来验证其射频性能。  二.隔离的测试 CMOS工艺技术平台关于隔离的测试结构是梳状结构,它们测试结构分别有AA层、Poly层和金属层。隔离测试结构的结果反映了器件相互隔离的效果,器件相互隔离效果的好坏严重影响电路的性能,fab厂检测它们的WAT参数是击穿电压BV,BV是Breakdown Voltage的缩写。这三种的版图结构及测试方法类似,这里只介绍AA层,其他不再赘余。 · AA隔离,Poly隔离和金属隔离 · CMOS工艺平台的检测AA隔离的结构有n型AA隔离和p型AA隔离。其版图如下图所示:  AA隔离测试结构的版图是交叉梳状非串联的两端器件。n型AA隔离测试结构必须设计在PW里面,p型AA隔离测试结构必须设计在NW里面。n型AA隔离测试结构是三端器件,它的三个端口分别是测试结构的两端和衬底(PW),它们分别连到PAD_N1、PAD_N2和PAD_B。 测量n型AA隔离击穿电压的示意图。它的基本方法是首先在测试结构的一端n型有源区加载DC扫描电压Vb,Vb从0V到12V,另一端n型有源区和衬底接地,从而测得漏电流Ib,得到Vb在Ib=1μA时的值,BV_NAA=Vb就是击穿电压。P型类似。 Poly隔离测试结构是在STI上的,并且它与衬底是完全隔离的。 金属隔离的结构包含该平台的所有金属层。影响因素 1)M1刻蚀尺寸异常; 2)淀积IMD1工艺异常。 3)Poly刻蚀尺寸异常; 4)侧墙工艺异常。 5)n+和p+离子注入异常; 6)AA刻蚀尺寸异常; 7)阱离子注入工艺异常。 三.栅氧化层测试 MOS晶体管栅氧化层完整性(GOI)的测试结构是多晶硅栅-氧化层-PW衬底(NMOS栅氧化层)和多晶硅栅-氧化层-NW衬底(PMOS栅氧化层)的电容结构,其电路连接如图所示:  两个端口栅(Gate)和衬底(Body)分别连到PAD_G和PAD_B,WAT测试机器通过这两个端口把电压激励信号加载在这个电容结构的两端,从而测得所需的电性特性参数数据。 栅氧化层在整个工艺流程里是非常关键,它的质量直接影响的MOS晶体管的电性特性,所以利用NMOS栅氧化层和PMOS栅氧化层的参数栅氧化层的电容(Cgox)、栅氧化层的厚度(Tgox)和栅氧化层的击穿电压(BVgox)检测它。 · 栅氧化层的电容(Cgox) 基本原理:在电容的一端加载AC 100kHz扫描电压,另一端接地,从而测得电容C,Cgox=C/Area,Area是电容的面积。 NMOS栅氧化层电容Cgox的基本方法是首先在栅电容的一端多晶硅栅上加载100kHz(VDD或者VDDA)扫描电压,另一端PW衬底接地,来测试电容C,Cgox=C/Area。 PMOS栅氧化层电容Cgox的基本方法是首先在栅电容的一端NW衬底上加载100kHz(VDD或者VDDA)扫描电压,另一端多晶硅栅上接地,来测试电容C,Cgox=C/Area。  · 电性厚度Tgox 测量栅氧化层电性厚度Tgox的基本原理是在电容的一端加载AC 100kHz扫描电压,另一端接地,从而测得电容C,利用公式Tgox=(εoεoxArea)/C,εo=3.9,εox=8.85418,求得电性厚度Tgox。实际上栅氧化层电性厚度Tgox是在栅氧化层电容C的基础上进行计算得到的。 · 击穿电压BVgox 栅氧化层电容的介质是SiO2。由于SiO2是绝缘体,在一般情况下是不导电的。但是当有一个外加电场存在时,随着外加电场的不断增大,当外加电场强度所提供的能量足以把一部分价带的电子激发到导带时,这时二氧化硅不再表现为绝缘性质,而是开始导电,这时所加的外加电压的值就是所测试的电容击穿电压值。 测量栅氧化层电容的击穿电压BVgox的基本原理是在电容的一端加载反向电压,另一端接地,从而测得栅漏电流Ig或者衬底漏电流Ib,得到单位面积电流强度Ig/Area或者Ib/Area,当漏电流强度达到100pA/μm2时,认为电容被电压击穿。此时加载在电容两端的电压就是击穿电压。 影响栅氧化层的因素包括以下几方面:1)阱离子注入异常;2)离子注入损伤在退火过程中没有激活;3)栅氧化层的厚度异常。 |