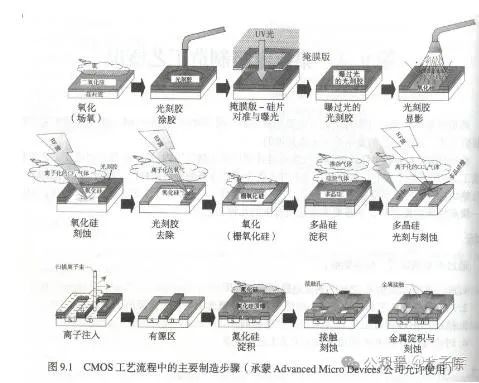

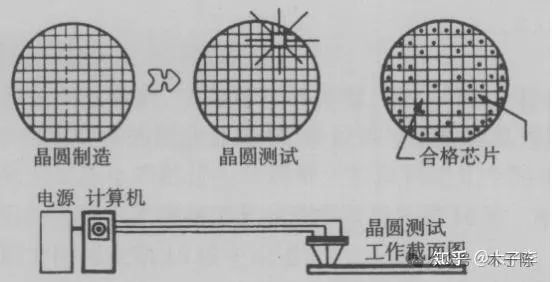

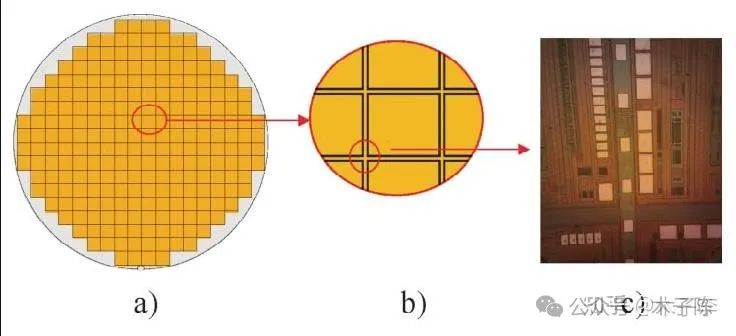

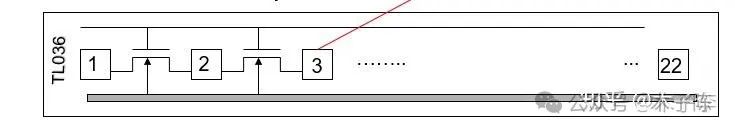

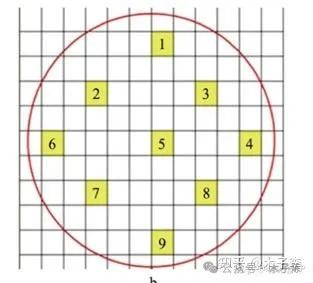

· 一.晶圆测试介绍经过上面的几道工艺之后,晶圆上就形成了一个个格状的晶粒。通过针测的方式对每个晶粒进行电气特性检测,以达到对晶圆的生产制造的精确控制和评估整个工艺制造流程的目的。为达到这个目的,出来在生产过程中精确控制每一步生产的关键尺寸和沉积薄膜的厚度外,还需要在晶圆出货前进行WAT电学测试保证器件的电学参数符合电学设计规则。  一般每个芯片的拥有的晶粒数量是庞大的,组织一次针测试模式是非常复杂的过程,这要求了在生产的时候尽量是同等芯片规格构造的型号的大批量的生产。数量越大相对成本就会越低,这也是为什么主流芯片器件造价低的一个因素。 在测试过程中,每一个芯片的电性能力和电路功能都被检测到。晶圆测试也称为芯片测试。在测试时,晶圆被固定在真空吸力的卡盘上,并与很薄的探针电测器对准,同时探针与芯片的每一个焊接垫相接触(见下图)。 · 电测器在电源的驱动下测试电路并记录下结果。 · 测试的数量、顺序和类型由计算机程序控制。测试机是自动化的,所以在探针电测器与第一片晶圆对准后(人工对准或使用自动视觉系统)的测试工作无需操作员的辅助。  测试是可以实现以下目标。 第一,在晶圆送到封装工厂之前,鉴别出合格的芯片。 第二,对器件/电路的电性参数进行特性评估。工程师们需要监测参数的分布状态来保持工艺的质量水平。 晶圆测试是主要的芯片良品率统计方法之一。随着芯片的面积增大和密度提高使得晶圆测试的费用越来越大。这样一来,芯片需要更长的测试时间,以及更加精密复杂的电源、机械装置和计算机系统,来执行测试工作和监控测试结果。特别是,视觉检查系统也是随着芯片尺寸扩大而更加精密和昂贵的。 二.晶圆接受测试 WAT是英文Wafer Acceptance Test的缩写,意思是晶圆接受测试,业界也称WAT为工艺控制监测(Process Control Monitor,PCM)。 1.为什么要做WAT测试? 1)Monitor Proce ss Window。检测每片晶圆产品的工艺情况,评估半导体制造过程的质量和稳定性,判断晶圆产品是否符合该工艺技术平台的电性规格要求。 2)Check Design Rule.检查并验证Design Rule的合理性与正确性。 3)Control the Process Parameters(SPC),反映生产线的实际生产情况,通过收集和分析WAT数据可以监测生产线的情况,也可以判断生产线变化的趋势,对可能发生的情况进行预警。 4)Debug the Process Error. 对WAT数据进行数理统计分析。通过收集WAT数据,获取工艺技术平台生产线的工艺信息,检测各个WAT参数的波动问题,评估工艺的变化的趋势(如最近一段时间某一技术平台MOS晶体管Vt的数值按生产时间排列是否有逐渐变大或者变小趋势),从而可以对工艺生产线进行预警,还可以通过分析特定的WAT参数的数据得知相关工艺步骤的工艺稳定性。 5)Reliability Characterization.通过特定的WAT测试结构监测客户特别要求的器件结构,检测它们是否符合电性规格要求,以及代工厂内部随机审查晶圆的可靠性测试(金属互连线电迁移和栅氧化层的寿命等)。 6)Device Modeling for Circuit Design.为器件工艺建模提供数据,通过测试不同尺寸器件的WAT参数数据,进行器件建模。 7)Develop next Generation.测试和分析特定的WAT测试结构,改善工艺,或者开发下一代工艺技术平台。 8)也是最重要的一点,WAT数据可以作为晶圆产品出货的判断依据,对晶圆产品进行质量检验。所有的WAT数据必须符合电性规格要求,否则不允许出货给客户。 2.晶圆上用于收集WAT数据的测试结构称为WAT测试结构(WAT testkey),WAT testkey是一条test line,为节约芯片面积及成本,芯片代工厂仅仅把WAT测试结构设计在晶圆上芯片(die)之间的划片槽(Scribe Line)。  WAT Testkey中通常包含工艺技术平台的active device 及 passive device,常见的TestKey 结构如下图所示:  其中,编号1,2,3为PAD,为测试时扎针的地方。 三.WAT Test Rule WAT测试作为验证器件性能重要的测试手段,测试类型非常多的,但基础要求是需要包含该工艺的所有有源器件和无源器件的典型尺寸。FAB会针对这些尺寸信息,根据工艺制定一套WAT参数或PCM targe,作为客户设计阶段的参考。 对于测试而言,总有出现fail的情况,那么出现fail了,要怎么判断该wafer可以继续进行下一步呢?这就涉及到WAT Test Rule ,主要分为以下两部分: 1.Sampling Rule · WAT 测试需要涵盖every LOT, every Wafer. · WAT 测试对12寸 Wafer来说为9点测试,8寸为5点测试。8寸五点测试2收3退,即2点fail 可以接受但3点fail不可接受,12寸为4收5退。 · WAT 测试每个点都要测关键参数。  2. WAT Fail Defination · Item Fail: 这里的Item 指的是 WAT 测试项,如果测试项有fail,则为item fail. · Site Fail: 如果wafer上有同一个点的多个item fail,则该 site fail. · Wafer Fail: 如果同一片wafer上有超过5个点fail, then this wafer fail. 那么,针对CMOS工艺技术平台,WAT测试又要测哪些呢?根据对FAB的调研,总结主要为以下几类: 1.MOS晶体管、栅氧化层的完整性(Gate Oxide Integrity,GOI) 2.多晶硅栅场效应晶体管(Poly Field Device) 3.第1层金属栅场效应晶体管(Metal1 Field Device) 4.n型结(n-diode结构)和p型结(p-diode结构) 5.方块电阻Rs(Sheet Resistance)、接触电阻Rc(Contact Resistance) 6.隔离、金属电容(MIM Capacitor)和多晶硅电容(PIP Capacitor)。 |