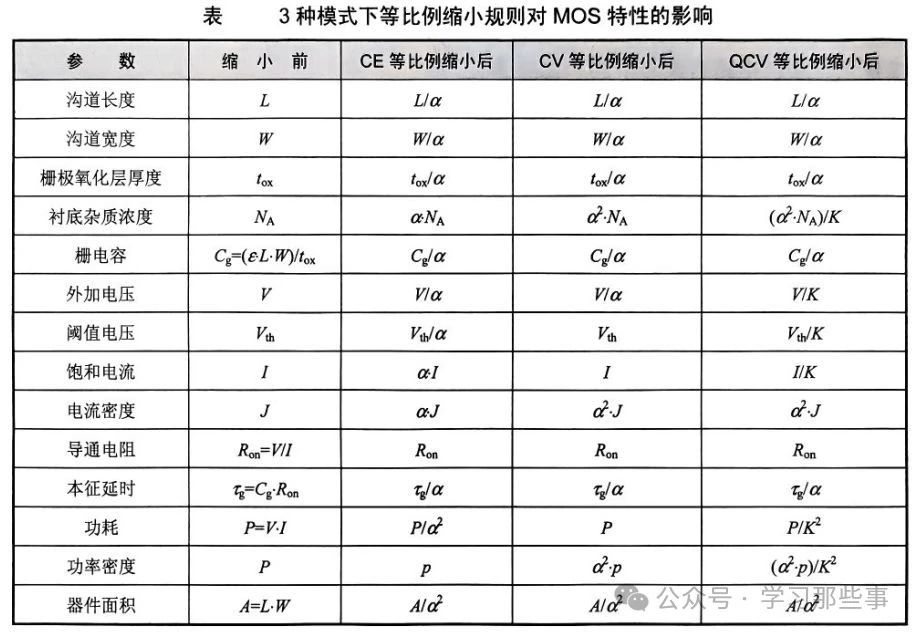

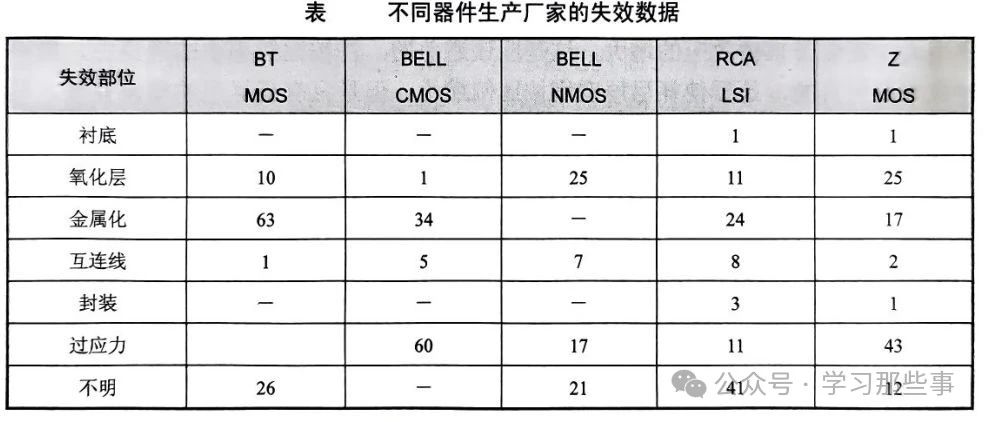

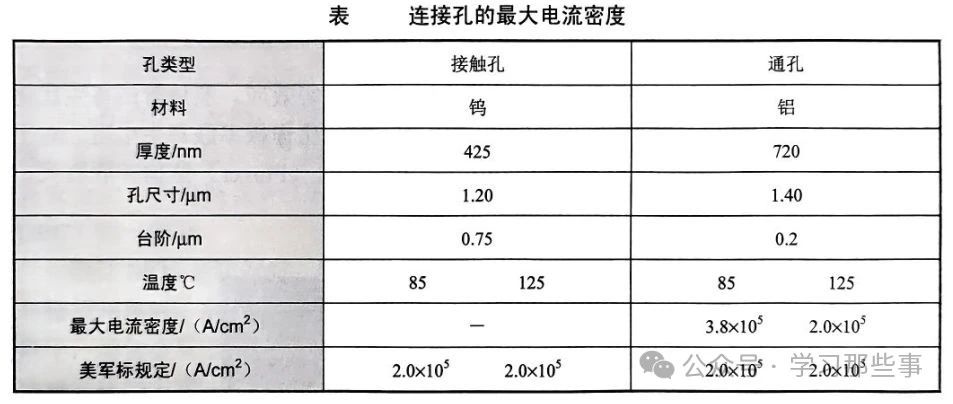

等比例缩小规则等比例缩小规则是MOS集成电路设计中常用的一个规则,它有助于理解微电子工艺升级对集成电路性能提升所起的作用。这个规则主要包括恒定电场(CE)理论、恒定电源电压(CV)理论和准恒定电源电压(QCV)理论,本文分述如下: 等比例缩小的3个规则 VLSI突出的可靠性问题 1.等比例缩小的3个规则 1.恒定电场等比例缩小规则 基本原理:在器件横向和纵向尺寸缩小的同时,将其电压按同一比例因子a缩小,目的是保持在缩小的器件中电场形态与在原先的器件中一样。由于电压和电流同时缩小,导通电阻保持不变,本征延时的减少主要得益于栅电容的缩小。 优点:器件的速度提高为原来的a倍,消耗的功率为原来的1/a²,占用的芯片面积为原来的1/a²。电路的速度将以线性关系增加,芯片的集成度按二次方关系增加,而功率密度仍然保持不变。 2 恒定电源电压等比例缩小规则 基本原理:只有器件的尺寸缩小,而电源电压保持不变。 优点:相比CE理论,CV理论在实际应用中更容易实现;器件的性能得到一定的提升,同时避免了CE理论中一些参数不能按比例变化的问题。 缺点:由于电源电压保持不变,器件的功耗密度可能会增加;需要采取其他措施来降低功耗,如优化电路设计和工艺参数。 挑战:功耗密度增加,功耗密度按面积平方的关系增大,对电路的大规模集成不利;热载流子注入效应,器件尺寸缩小导致沟道横向电场强度增加,引发热载流子注入效应;栅氧的经时击穿,栅氧化层减薄导致强电场下碰撞电离产生的高能量电子破坏栅氧化层的绝缘性。 解决方案:准恒定电压等比例缩小规则(QCV理论),器件尺寸和电源电压按不同的比例因子缩小,以平衡性能和功耗;优化电路设计和工艺参数,通过优化电路设计和工艺参数来降低功耗,如采用LDD工艺技术改善热载流子注入效应;采用高k栅介质材料,使用高k栅介质材料来增强栅氧化层的绝缘性,减少经时击穿的风险。 3.准恒定电源电压等比例缩小规则 基本原理:器件的尺寸和电源电压都按一定的比例缩小,但缩小的比例不完全相同。 优点:相比CE和CV理论,QCV理论在实际应用中更加灵活。可以在一定程度上平衡器件性能和功耗之间的关系。 缺点:需要精确控制器件尺寸和电源电压的缩小比例,以实现最佳的性能和功耗平衡。 实现方式:QCV理论,作为CE理论和CV理论的折中,QCV理论使工艺尺寸和电压分别按不同的比例因子进行缩小,以平衡性能和功耗。 技术细节:缩小比例,QCV理论中,器件尺寸和电源电压的缩小比例并不完全相同,具体比例取决于设计需求和工艺条件;对电路性能的影响,通过优化器件尺寸和电源电压的缩小比例,QCV理论能够在提升电路性能的同时,有效控制功耗。 实际应用案例:便携式电子设备,随着器件特征尺寸缩小到微纳米量级,便携式电子设备对降低电路功耗提出了更高要求。QCV理论通过折中考虑电源电压和器件尺寸的缩小比例,满足了这一需求;DRAM发展,在DRAM的发展中,QCV理论也得到了应用。通过缩小存储单元面积、增大芯片面积和改进单元结构设计,QCV理论有助于提高DRAM的集成度和性能。 电路性能提升:速度和功耗平衡,QCV理论通过平衡器件性能和功耗之间的关系,实现了电路速度的提升和功耗的有效控制;可靠性提升,采用QCV理论设计的电路具有更高的可靠性,能够满足高性能及高可靠性的要求。  4.等比例缩小规则在MOS集成电路中的应用 提高电路性能:通过缩小器件尺寸,可以减小沟道长度和寄生电容,从而改善集成电路的性能和集成度。 降低功耗:缩小器件尺寸可以降低功耗,提高电路的能效比。 增加集成度:缩小器件尺寸可以增加芯片的集成度,实现更多的功能在更小的芯片面积内。 等比例缩小规则在MOS集成电路设计中具有重要意义。在实际应用中,需要根据具体需求选择合适的缩小理论,并进行相应的电路设计和工艺参数优化,以实现最佳的性能和功耗平衡。 2.VLSI突出的可靠性问题 在等比例缩小原理下,器件尺寸缩小k倍,电源电压减少k倍,掺杂浓度增加k倍。这一规则使器件沟道长度缩小到90nm,但也带来了两个致命的可靠性问题:电迁移危险增加和栅氧化层中的电场增强。如果器件为保持与现有逻辑兼容而保持恒定电源电压的等比例缩小,这些问题将更为严重,电流密度和电场将随缩小因子增加,导致功率密度增加和结温升高。  上表列出了不同厂家器件的失效数据,其中主要失效机理包括铝金属化腐蚀和氧化层问题,这与VLSI的可靠性问题相吻合。MOS器件的栅氧化层对电场增强特别敏感,高电场会引起薄氧化层的击穿和热电子的俘获,这是MOS器件的基本失效机理。目前,MOS器件的栅氧化层厚度可以小于1.2nm,但为了在25℃、5V环境下工作10年,最薄的栅氧化层厚度应不小于7.2nm,随着温度的上升,氧化层还需加厚。 电迁移是接触和互连的主要失效机理,是由电流引起的金属原子沿互连线的迁移。金属原子受静电和“电子风”力的作用而产生移动,引起金属线或接触部位断路或相邻金属线的短路。  上表列出了连接孔的最大电流密度。在设计上通常规定金属铝通过的最大电流密度是1mA/1um铝线宽,其他金属也可以根据具体情况进行折合。 针对以上可靠性问题,可以采取以下解决方案和缓解措施: 电迁移问题 材料选择:用铜(Cu)代替铝(Al)互连,因为Cu具有较低的电阻率、较高的电导率和较高的熔点。 合金使用:使用Al和Cu合金互连,以提高平均失效时间(MTTF)。 设计优化:避免互连中的直角弯曲,采用层间电介质和互连掺杂剂来减少传播延迟和内部电容。 控制电流密度:在设计上规定金属铝通过的最大电流密度,以避免电迁移引起的金属线或接触部位断路或短路。 改进互连设计:减少VLSI电路块之间的信号时间延迟,降低时钟偏斜。 栅氧化层击穿问题 降低工作电压:从电路设计的观点看,降低工作电压无疑是提高可靠性指标的一个重要因素。 增加氧化层厚度:加速试验表明,为了使器件能在25℃、5V环境下工作10年,最薄的栅氧化层厚度应不小于7.2nm,随着温度的上升氧化层还得加厚。 信号完整性和噪声问题 解决方案:使用去耦电容来抑制电源噪声,在布线设计时采用适当的屏蔽和间距来减少串扰,设计合理的电源和地线网络,以减少地弹噪声,采用终端匹配技术减少信号传输线上的反射。 缓解措施:在电路设计阶段就需考虑信号完整性的要求,通过仿真工具在早期发现并解决潜在的问题。 通过以上措施,可以有效提高VLSI器件的可靠性,满足高性能和高可靠性的要求。 |