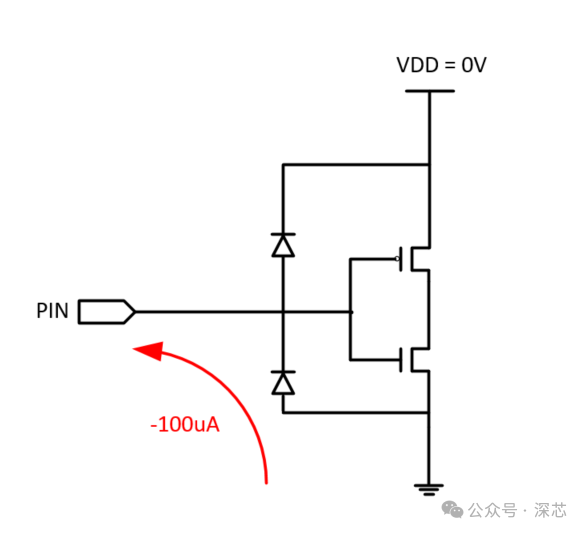

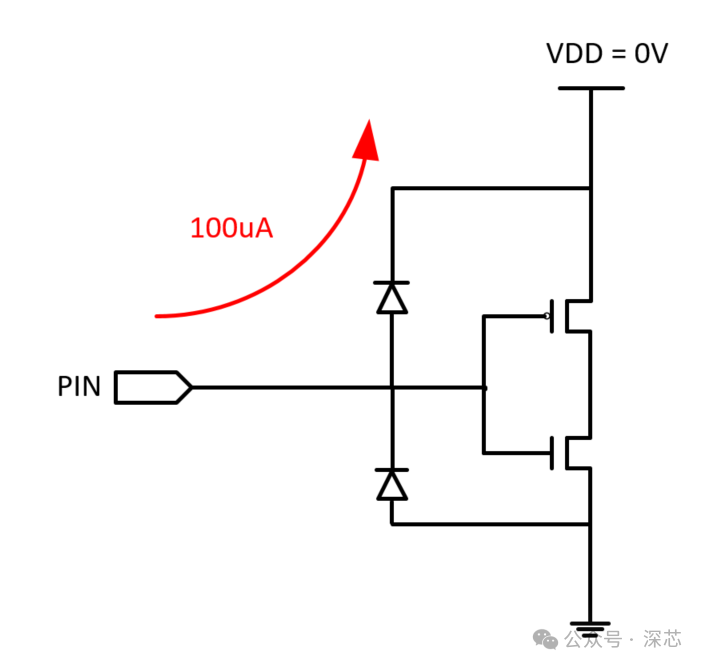

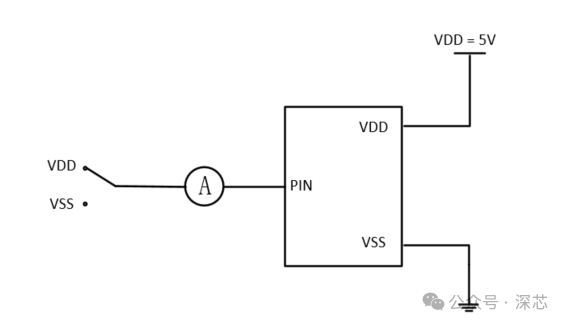

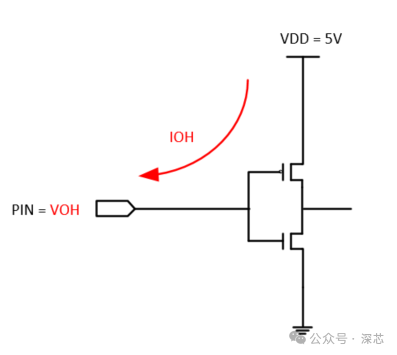

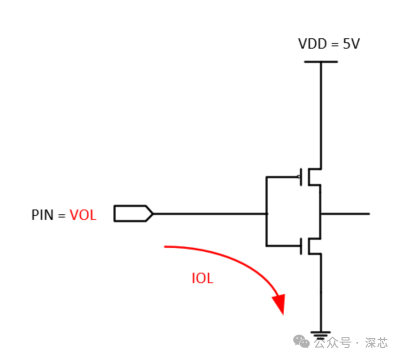

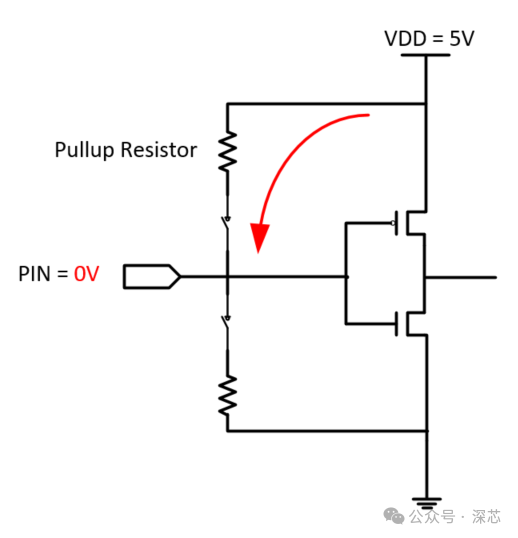

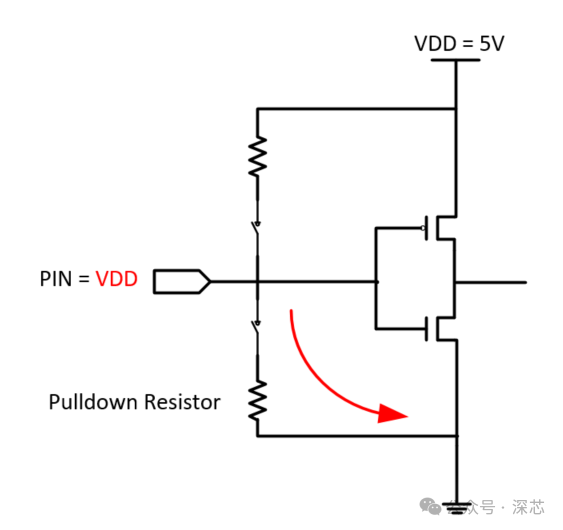

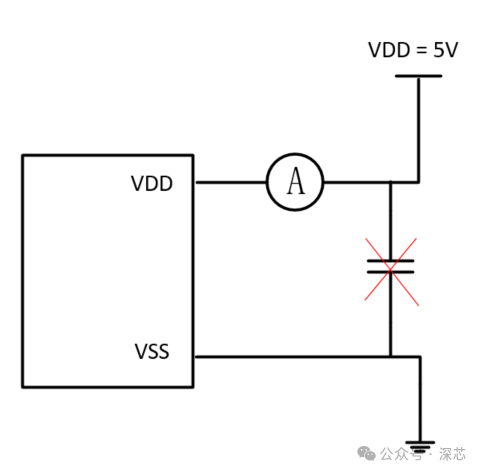

做芯片测试的同学经常会涉及到Continuity测试、Leakage测试、GPIO drive capability测试、GPIO pullup/pulldown resistor测试、standby idd、run idd、IDDQ、MBIST、SCAN等测试,小编在此带大家总结一下这些测试的基本原理。1. Continuity测试(即OS测试) 该测试主要是测试芯片的open/short特性,即测量芯片pin脚对VDD或者GND有没有短路(short)或断路(open)。 当测某一pin的OS时,应使VDD=0V,同时其他pin的电压也全为0。下图为测某一pin对GND的OS测试时的示意图,ATE会从pin抽一个100uA的电流,下方的二极管导通,在正常工作的情况下,测得的电压应该在-0.2V~-0.7V之间。  下图为测某一pin对VDD的OS测试时的示意图,ATE会从pin灌入100uA的电流,上方的二极管导通,在正常工作的情况下,测得的电压应该在0.2V~0.7V之间。  如果有short情况发生,测得的电压一般接近0V;如果是open的情况,则测得的电压一般为5V/-5V(测试程序中设置的钳位电压)。 2. Leakage测试即漏电流测试。在该测试过程中一般将芯片正常上电,然后将pin配置成input状态,给pin上分别灌入VSS(0V)和VDD的电压,测量该pin上的电流,一般测量值为-1uA~1uA。  当pin电压等于VDD时,测得的电流为对GND的漏电流当pin电压等于VSS时,测得的电流为对VDD的漏电流 3. GPIO drive capability测试即为GPIO的驱动能力测试 GPIO drive capability一般对应datasheet中的VOH/VOL或者IOH/IOL指标,其实VOH/VOL和IOH/IOL是同一个指标,只不过测试方法不同。 下图为VOH或者IOH的测试示意图。将GPIO配置成output模式,并且输出高电平(逻辑1)。当测量IOH时,则ATE在pin上施加VDD-0.8V电压,此时该pin上电流即为IOH。当测量VOH时,则ATE从该pin拉5mA/20mA电流(视该pin的驱动能力而定),此时该pin上测得的电压即为VOH。  下图为VOL或者IOL的测试示意图,同样将GPIO配置成output模式,只不过此时输出低电平(逻辑0)。当测量IOL时,则ATE在pin上施加0.8V电压,此时该pin上电流即为IOL。当测量VOL时,则ATE从该pin灌入5mA/20mA电流(视该pin的驱动能力而定),此时该pin上测得的电压即为VOL。  4. Pullup/Pulldown resistor测试 该测试目的是测试芯片引脚内部的上拉/下拉电阻的大小。在测试时该pin需要配置成input模式。 下图为上拉电阻的测试示意图。当测试上拉电阻时需将该pin配置成input状态,同时打开pullup设置,给pin脚施加电压0V,测量pin脚上电流,然后根据R=U/I可以计算出上拉电阻的阻值。  下图为下拉电阻的测试示意图。当测试下拉电阻时需将该pin配置成input状态,同时打开pulldown设置,给pin脚施加VDD电压5V,测量pin脚上电流,然后根据R=U/I可以计算出下拉拉电阻的阻值。  5. standby idd 对于MCU来说,standby idd即是在standby mode下测量VDD pin上电流。Standby mode一般为芯片的低功耗模式,芯片内部大部分时钟均处于关闭的状态,只保留LPO时钟作为芯片的唤醒时钟。需要注意的是一般测standby idd时候需要将VDD pin上并接的电容去掉,因为电容存在充放电的过程,可能会对电流的测量产生影响。  6. Run iddRun idd的测试与standby idd基本一致,只不过会让芯片处于run mode,有些会要求将外设的时钟打开进行测试。 7. IDDQIDDQ即静态电流,指CMOS电路在稳定状态(无信号跳变)下的电源电流。在无缺陷的CMOS电路中,静态电流应接近零(仅有漏电流,一般微安级)。正常CMOS逻辑在稳态下,PMOS和NMOS管不同时导通,理论静态电流很小。缺陷影响:物理缺陷(如栅极氧化物短路、电源/地桥接)会形成额外电流路径,导致IDDQ升高。 8. MBISTMBIST一般指SRAM的测试,采用芯片内部自建的一些测试逻辑来进行测试,机台只需要通过JTAG接口下达测试的指令,即可从TDO接口获取测试结果。MBIST测试结束后一般会有两个信号输出BIST_DONE和BIST_FAIL。 9. SCANscan就是把普通寄存器替换成可扫描的寄存器,目的是创建control和observation点,然后把所有的可扫描寄存器连接在一起串成扫描链(scan chain),利用扫描链,工具自动产生测试patterns,让寄存器处于一个特定的值(control),然后将期望的值移出来进行对比(observe),来判断芯片是否有缺陷。SCAN测试一般分stuck-at和transition测试,stuch-at测试覆盖固定电平缺陷,但对时序敏感缺陷无效;transition则主要针对时序路径的延迟缺陷。 |