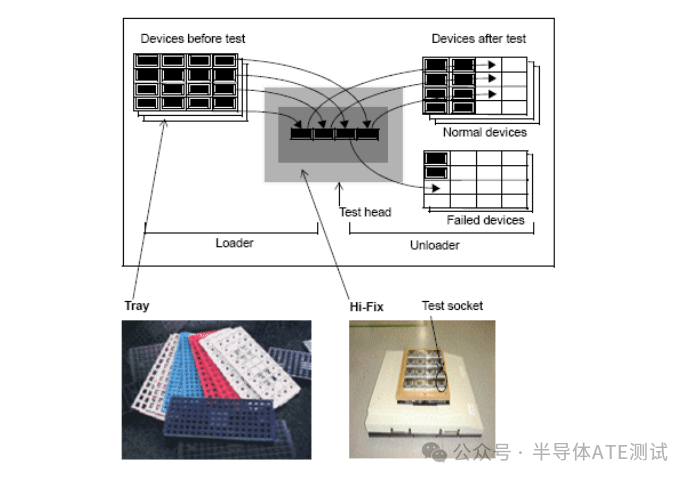

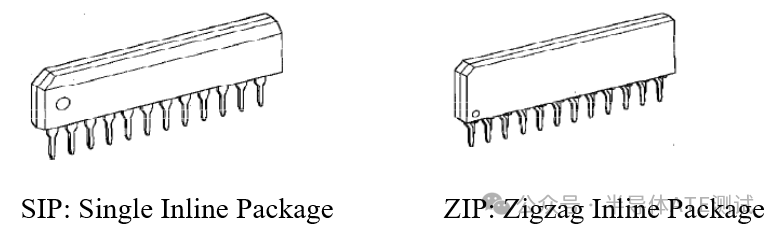

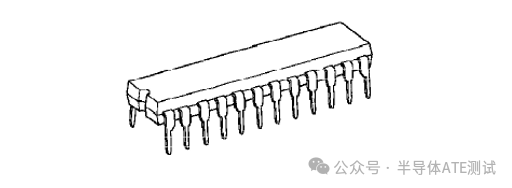

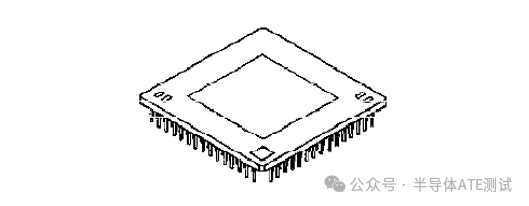

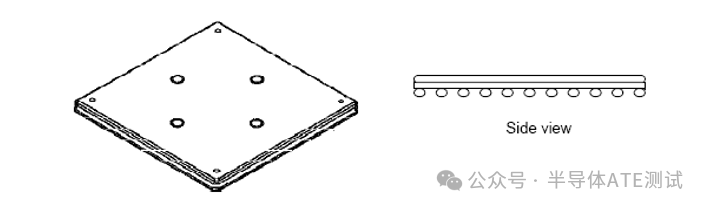

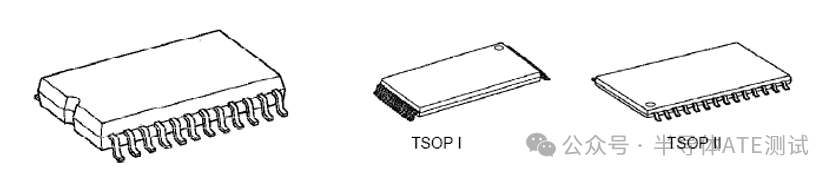

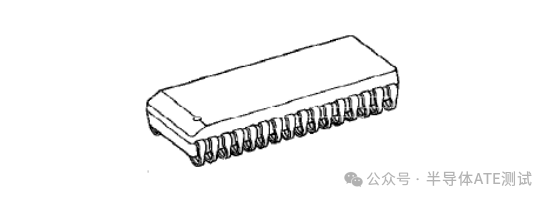

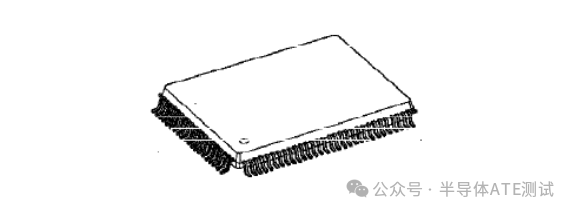

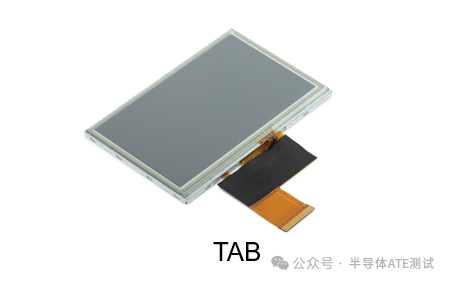

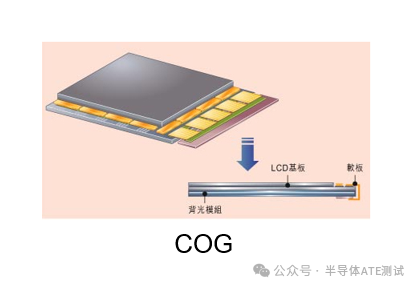

引言后道生产中的器件检测称为封装测试(Package Test)或终测(Final Test)。该测试是对经过多道制程完成的半导体器件进行的最终电性验证。在封装测试阶段,ATE系统会对器件制造商承诺的电气特性(DC/AC参数、功能测试等)和机械规格(引脚阻抗、封装完整性等)进行全检,并执行包括高低温循环测试在内的可靠性验证。 测试系统与分选机 在后道生产测试中,会使用测试系统和动态测试分选机(以下简称分选机)进行检测。  <1> 测试系统 与前端生产测试方式相同,测试系统向器件施加信号,测量器件的输出信号,执行PASS/FAIL测试,并将测试结果传输至分选机。 <2> 分选机 分选机将器件从载盘(Tray)中移出,并将其插入测试点的测试插座(Test Socket)。测试完成后,分选机接收来自测试系统的测试结果(PASS/FAIL结果),并将良品(PASS)和不良品(FAIL)分开放置。此外,分选机具备温度调节功能,可在低温至高温范围内设定器件温度,以支持可靠性测试。  半导体封装 · 封装(Package)是电子元器件的保护性外壳。封装外部设有连接端子(connectors)。器件并非直接焊接在印刷电路板(PCB)上,而是安装在专用IC插座(IC socket)中,以便后续设备配置升级。 · 封装外形主要分为两类:通孔插装型(through-board mount type)和表面贴装型(surface-mount type)。 通孔插装型和表面贴装型各自具有多种封装形态。 · 通孔插装型封装 通孔插装型器件的引脚(leads/pins)需插入印刷电路板的通孔(through hole)中,通过焊接实现与PCB线路(wiring patterns)的连接。常见类型包括: · 单列直插封装(SIP, Single Inline Package)在器件单侧排列单排引脚。 § 若引脚呈交错锯齿状排列,则称为ZIP(Zigzag Inline Package)。  双列直插封装(DIP, Dual Inline Package) · § DIP封装在器件两侧对称排列两排引脚,是早期集成电路的典型封装形式,引脚间距(pitch)通常为2.54mm(100mil)。根据材质可分为: o 塑料双列直插封装(PDIP) o 陶瓷双列直插封装(CDIP)  · 针栅阵列封装(PGA, Pin Grid Array) PGA封装在封装底部以矩阵形式排列引脚阵列,具有高密度互连特性,主要特点包括: o 引脚采用垂直针状设计,可插入专用插座(PGA socket) o 常见于高性能CPU(如Intel 80486/Pentium系列) o 衍生类型包括: I. 塑料针栅阵列(PPGA) II. 陶瓷针栅阵列(CPGA) III. 倒装针栅阵列(FliPGA)  表面贴装型封装(Surface-Mount Type Packages) · 表面贴装型器件的引脚直接与印刷电路板(PCB)上的焊盘(connection pad)接触,通过焊接实现与电路板线路(wiring pattern)的连接。主要封装类型包括BGA、SOP、SOJ和QFP等。 · 球栅阵列封装(BGA, Ball Grid Array) § 封装底部以矩阵形式排列焊球(solder balls)作为互连端子 § 具有高密度互连、低寄生电感等优势 § 衍生类型: o 芯片级封装(CSP, Chip Scale Package) o 尺寸接近半导体芯片本身的超小型BGA,封装面积不超过芯片面积的1.2倍  小外形封装(SOP, Small Outline Package) § 两侧采用"鸥翼形"(gull-wing)引脚设计 § 重要子类: o 薄型小外形封装(TSOP, Thin SOP) · 定义:安装高度≤1.2mm的超薄封装 §分类标准: I. TSOP I:从封装较长边引出引脚(常见于存储器) II. TSOP II:从封装较短边引出引脚  · 小外形J引脚封装(SOJ, Small Outline J-Leaded Package) § 结构特点:两侧采用"J形"引脚设计(引脚末端向内弯曲呈J形钩状) § 典型引脚间距:1.27mm(50mil) § 主要应用:DRAM模块等需要插座安装的存储器器件  · 四方扁平封装(QFP, Quad Flat Package) § 核心特征: o 四边均布"鸥翼形"(gull-wing)引脚 o 标准引脚间距范围:0.4mm~1.0mm § 重要变体: o 薄型QFP(TQFP):厚度≤1.4mm o 低剖面QFP(LQFP):厚度1.4mm~2.7mm o 细间距QFP(FQFP):引脚间距≤0.65mm  · TAB(Tape Automated Bonding,载带自动键合) § 技术特点: o 使用柔性载带(Tape)实现芯片与基板的互连 o 通过凸块(Bump)实现各向异性导电连接 § 技术特点: o 使用柔性载带(Tape)实现芯片与基板的互连 o 通过凸块(Bump)实现各向异性导电连接 o 典型应用:LCD驱动IC、高密度柔性电子组装  · COG(Chip On Glass,玻璃覆晶封装) · § 核心工艺: o 将IC芯片直接邦定(Bonding)到LCD玻璃基板 o 采用各向异性导电胶(ACF)实现电气连接 o 技术优势:减少60%模块体积,提升显示模组可靠性  · COF(Chip On Film,薄膜覆晶封装) § 技术实现: o 在柔性薄膜(Polyimide)上集成驱动IC o 使用微细铜线路(线宽可达10μm) § 行业应用:智能手机窄边框显示模组、可折叠设备  |