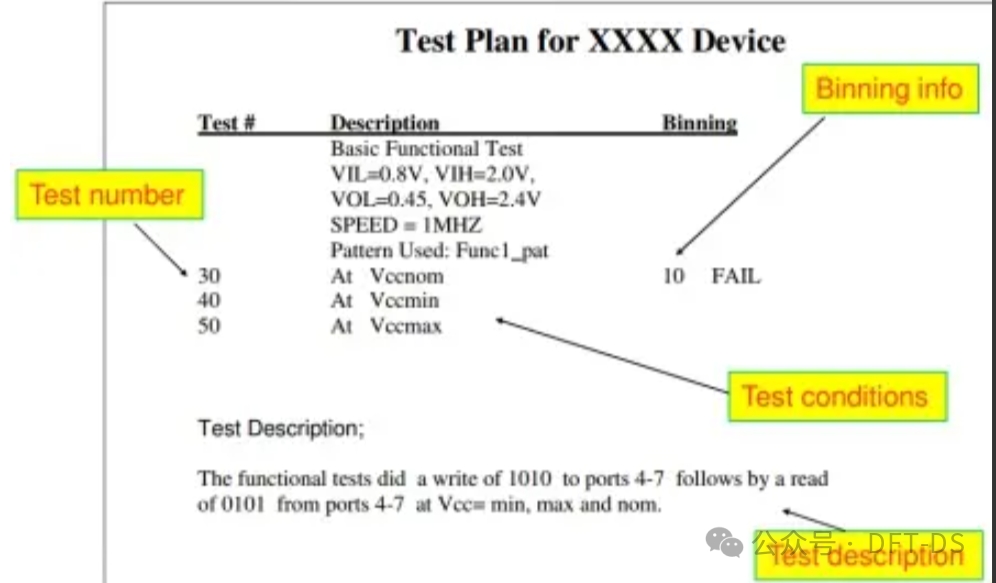

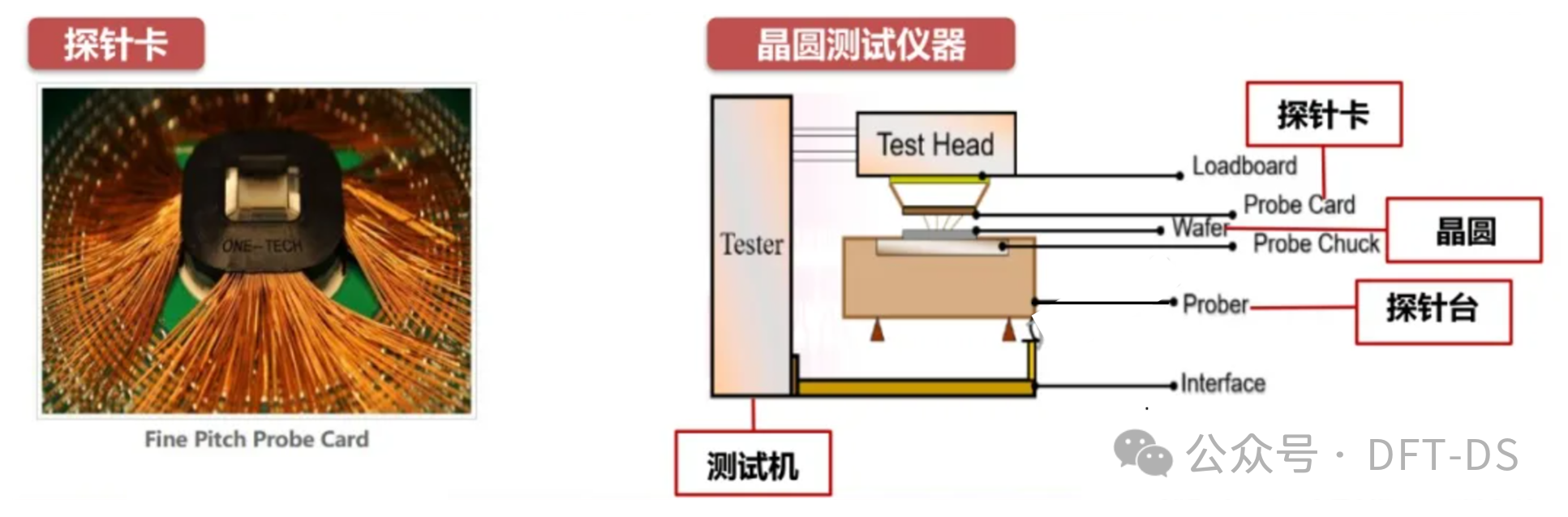

在半导体制造流程中,确保每一颗芯片在出厂前都具备良好的功能和性能,是保证产品质量和客户满意度的关键。为此,芯片测试被划分为多个阶段,其中CP测试(Circuit Probing Test,通常称为晶圆测试或Wafer Test)是整个测试流程中的一个重要环节。CP测试在芯片封装之前进行,通过探针卡(Probe Card)与晶圆上的焊盘(Pad)接触,对每一个尚未切割的芯片(Die)进行电性与功能测试。本文将系统介绍CP测试的定义、目的、流程、关键技术、挑战及其在芯片制造中的重要作用。一、基本概念介绍

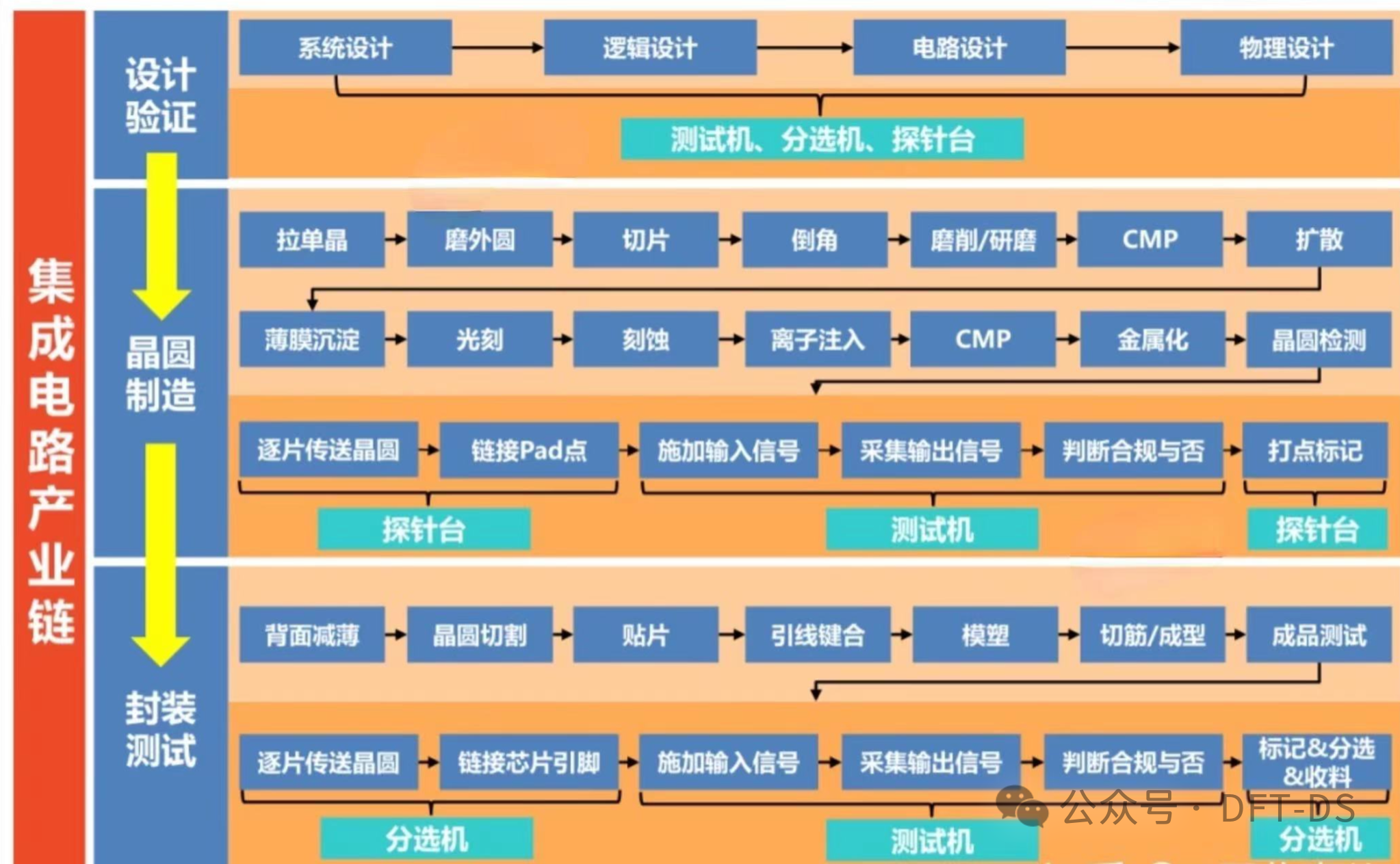

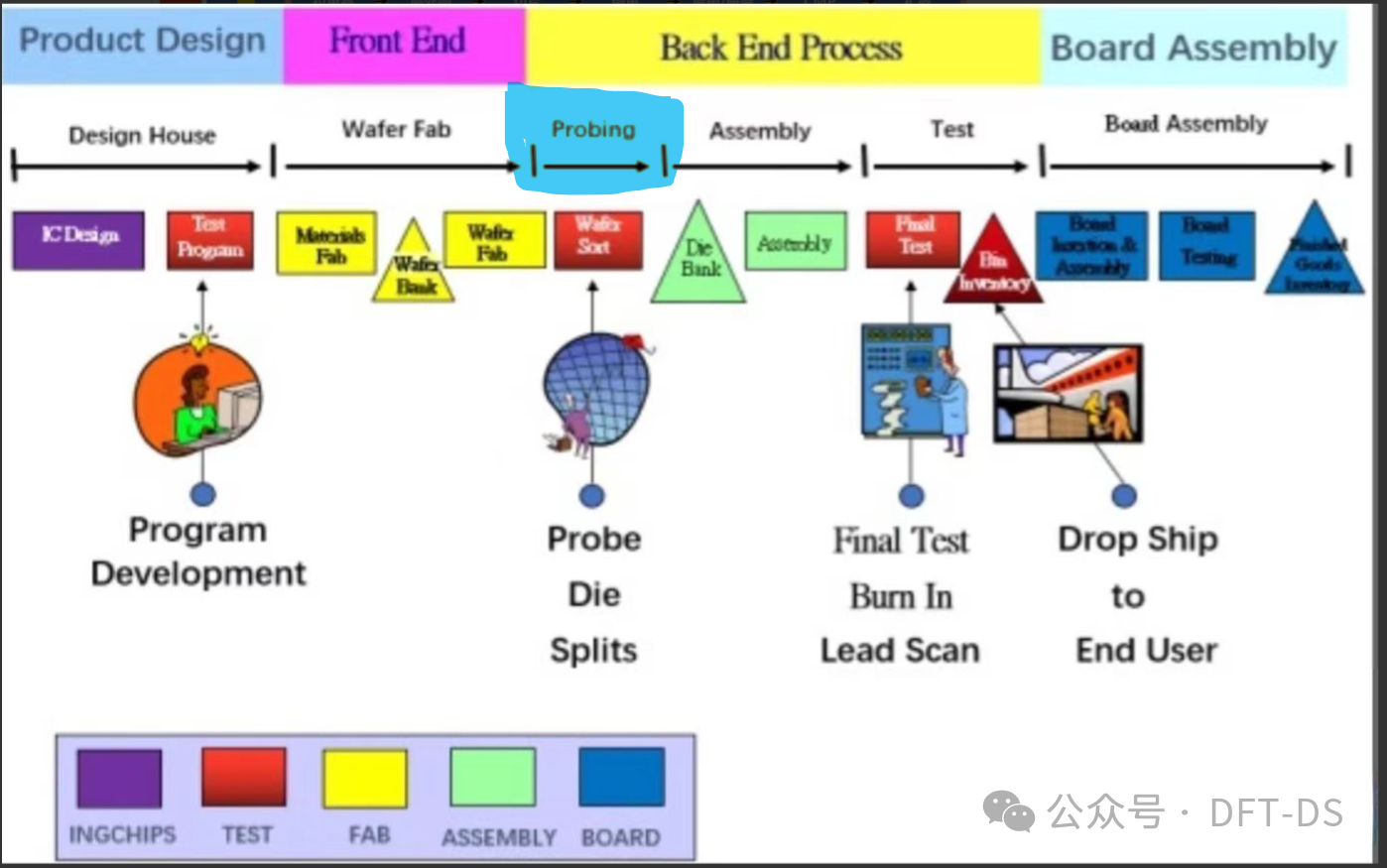

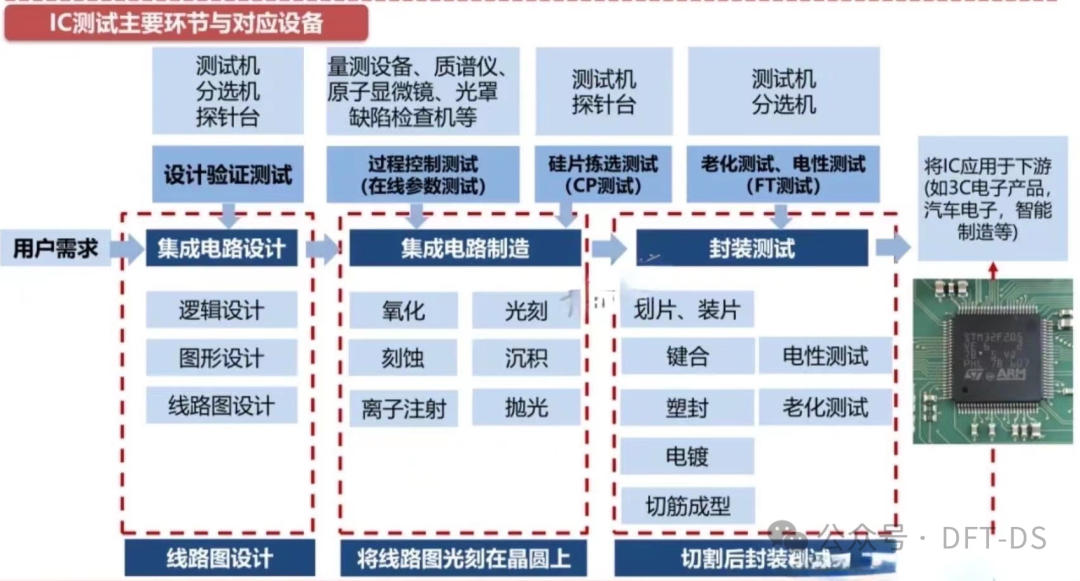

如下图所示,一颗芯片最终做到终端产品上,一般需要经过设计,晶圆制造,晶圆测试,封装,成品测试,板级封测等很多环节。 |

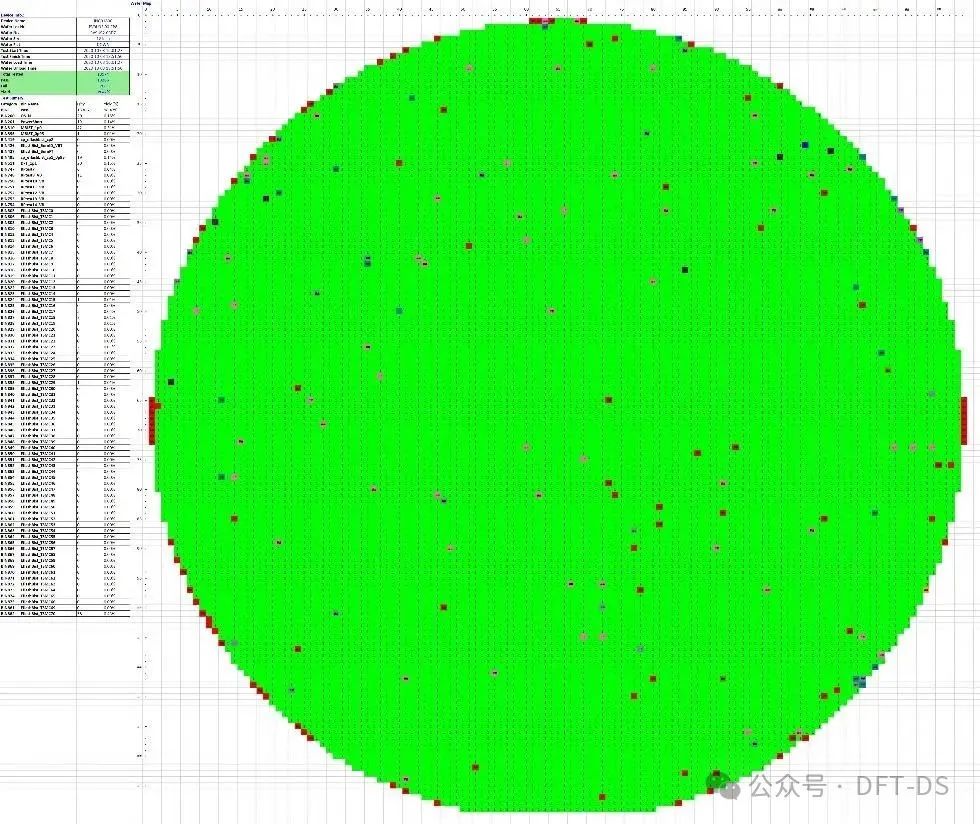

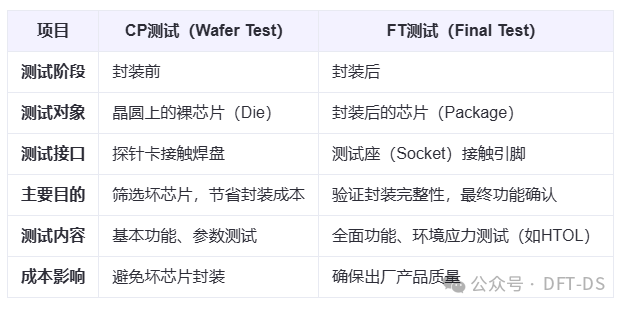

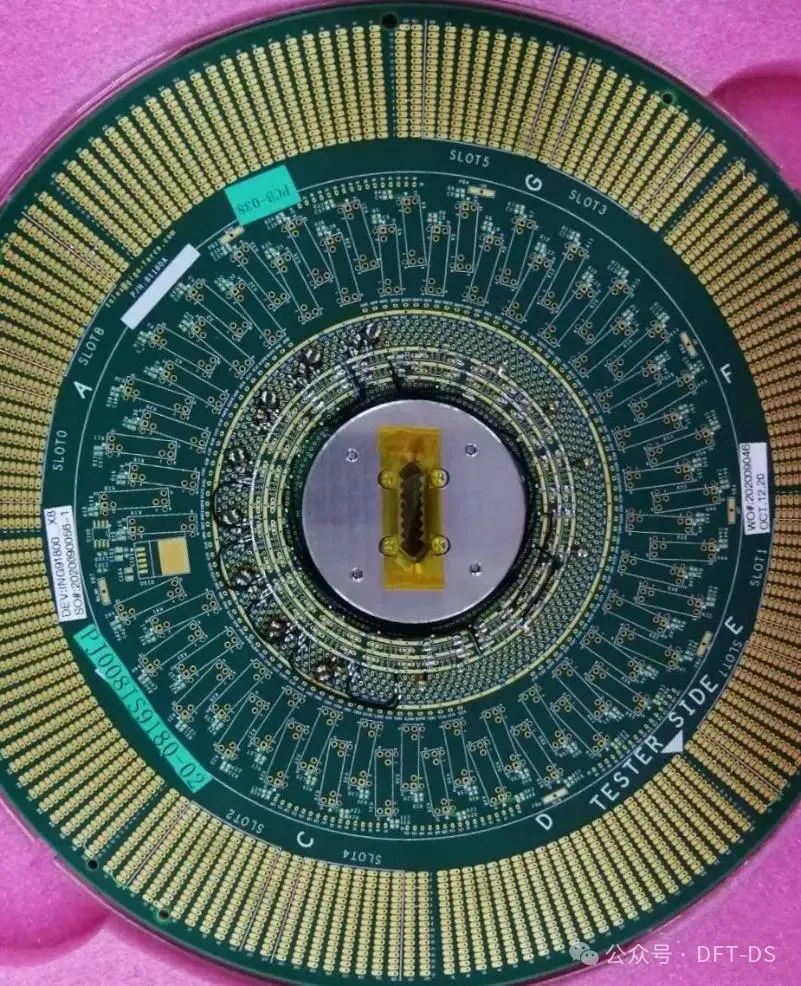

图

图