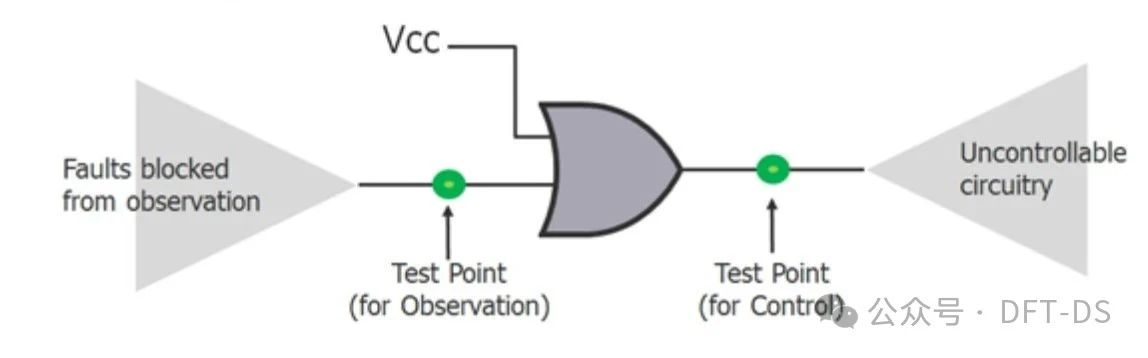

在现代数字集成电路(IC)设计中,可测性设计(Design for Testability, DFT)是确保芯片制造后能够被有效测试、快速定位缺陷并提升良率的关键技术。随着工艺节点不断缩小、芯片复杂度持续上升,传统的外部引脚测试已无法满足对内部逻辑的可观测性(Observability)和可控制性(Controllability)需求。为此,DFT 引入了 Test Point(测试点) 技术,作为增强测试覆盖率、优化测试质量的重要手段。 一、什么是 Test Point?Test Point(测试点) 是在芯片设计中人为插入的额外逻辑节点,用于: · 提高内部信号的可控制性(Controllability):更容易将特定值驱动到难以到达的节点。 · 提高内部信号的可观测性(Observability):更容易将内部状态传递到可观察的输出端(如扫描链)。 测试点不是功能逻辑的一部分,而是专为测试服务的辅助结构,通常在功能模式下不工作,在测试模式(如扫描测试、MBIST)下启用。 它通过对关键节点的状态进行主动控制或被动观测,使原本无法被测试向量覆盖的故障变得可检测,从而降低测试难度、提高测试质量。  Uncontrollable and Unobservable Circuitry

|

| 场景 | 问题 | Test Point 解决方案 |

| 深层组合逻辑 | 输入难以驱动内部节点 | 插入可控性测试点(Mux) |

| 高扇出节点 | 信号变化难以观测 | 插入可观测性测试点 |

| 异步逻辑块 | 不在扫描链中,不可测 | 添加旁路或观测路径 |

| 加密模块 | 功能模式下不可访问 | 测试模式下启用测试接口 |

| 模拟/混合信号接口 | 数字测试难以覆盖 | 添加数字scan loop 电路 |

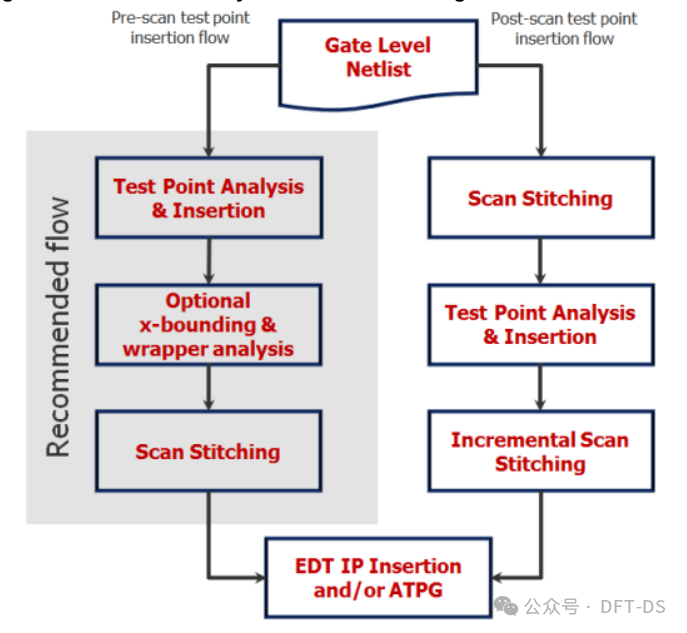

五、测试点的插入流程与策略

测试点的插入需结合 ATPG 工具的故障分析结果,遵循 “最小代价最大化覆盖率” 原则,流程如下:

1. 故障覆盖率分析(Pre-TP Analysis)

在插入测试点前,首先通过 ATPG 工具对初始设计进行故障仿真,生成未覆盖故障列表,并分析未覆盖原因:

标记 “因可控性不足未覆盖” 的故障(需插入控制测试点);

标记 “因可观测性不足未覆盖” 的故障(需插入观测测试点); 排除 “固有不可测故障”(如冗余逻辑故障,无需处理)。

2. 测试点位置优化

为避免过度插入(增加面积和功耗),需通过算法优化测试点位置:

共享性优先

:优先选择能覆盖多个未测故障的节点(如高扇出节点,一个测试点可解决多个下游故障);逻辑深度优先:优先处理深逻辑层节点(表层节点通常可控 / 可观测性更好);代价评估:计算每个潜在测试点的 “覆盖率收益 / 面积开销比”,优先插入高收益点。

3. 插入与验证(Post-TP Implementation)

· 插入测试点后,需更新网表和 DFT 约束(如test_en、test_ctrl的时序约束);

· 重新运行 ATPG,验证故障覆盖率提升效果以及pattern数目减少的数量;

· 进行时序验证(STA),确保测试点引入的延迟不影响功能模式和测试模式的时序收敛;

· 进行功能仿真,验证测试点在功能模式下的透明性(不干扰正常逻辑)。

工具插入流程(以 Tessent 为例)

SETUP>

set_system_mode analysis

ANALYSIS>

set_test_point_analysis_options -total_number 1000

ANALYSIS>

set_test_point_analysis_options

ANALYSIS>

set_test_point_insertion_options \ -control_point_enable cp_en -observe_point_enable op_en

ANALYSIS>

analyze_test_points

ANALYSIS>

insert_test_logic //生成带 TP 的新网表 + 新 SDC。

INSERTION> report_test_points > testpoints.txt

INSERTION> write_design -output_file my_modified_design.v

六、插入Test Point 的优缺点

| 优点 | 缺点 |

| ✅ 提高测试覆盖率(尤其是 transition fault) | ❌ 增加芯片面积(每点约几十到几百μm²) |

| ✅ 减少测试向量数量,缩短测试时间 | ❌ 可能影响功能时序(插入逻辑引入延迟) |

| ✅ 改善难测节点的可控制性与可观测性 | ❌ 增加功耗(额外逻辑翻转) |

| ✅ 有助于调试和良率分析 | ❌ 设计复杂度上升 |

七、最佳实践与设计建议

1. 优先使用工具自动分析:让 ATPG 工具识别“难测”节点,再决定是否插入。2. 控制数量:避免过度插入,平衡覆盖率与面积开销。

3. 避免关键路径:不要在时序关键路径上插入 Test Point,以免影响性能。

4. 测试模式隔离:确保 Test Point 在功能模式下不干扰正常逻辑。

5. DFT 模式控制:使用统一的 test_mode 信号控制所有 Test Point。

6. 避免增加Function功耗:确保 Test Point 相关逻辑在功能模式下处于静态(不消耗电流)。

7. 验证 Test Point 功能:

· 形式验证(Formal Verification)确保功能模式下无影响。

· DFT pattern的仿真验证测试模式下的行为正确。

总结

Test Point 是 DFT 中一种“以小换大”的优化策略 —— 通过少量面积开销,换取显著的测试质量提升。它不是必须的,但在以下场景中极具价值:

· 高复杂度 SoC

· 低良率产品(需精细故障分析)

· 安全关键应用(如汽车、医疗)

· 先进工艺节点(7nm 及以下)

掌握 Test Point 的原理、类型与插入方法,是 DFT 工程师和数字设计工程师的重要技能。在实际项目中,应结合 ATPG 工具分析,适时、节制地使用 Test Point,实现测试覆盖率、测试成本与芯片性能的最佳平衡。