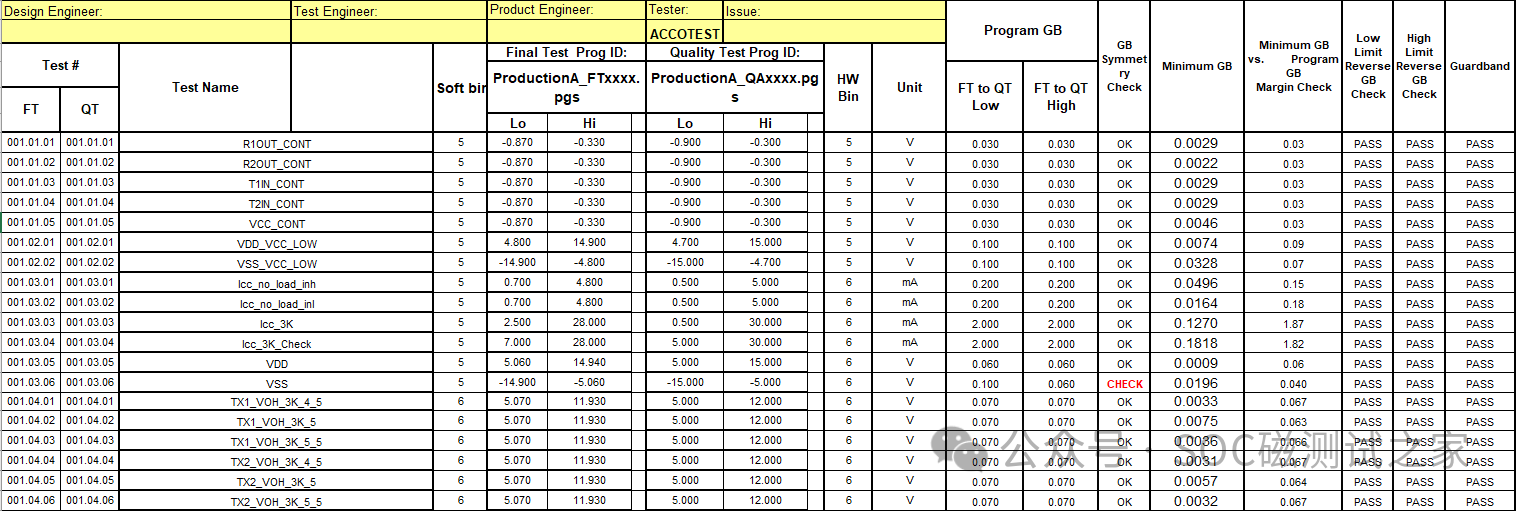

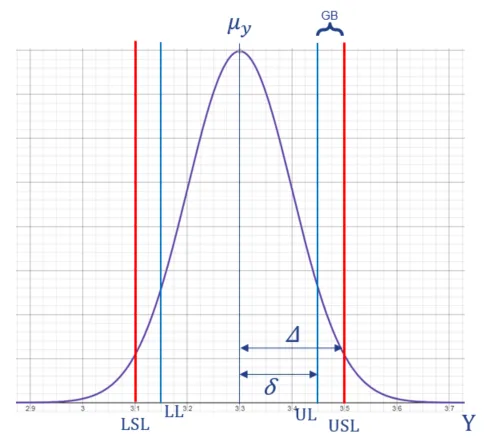

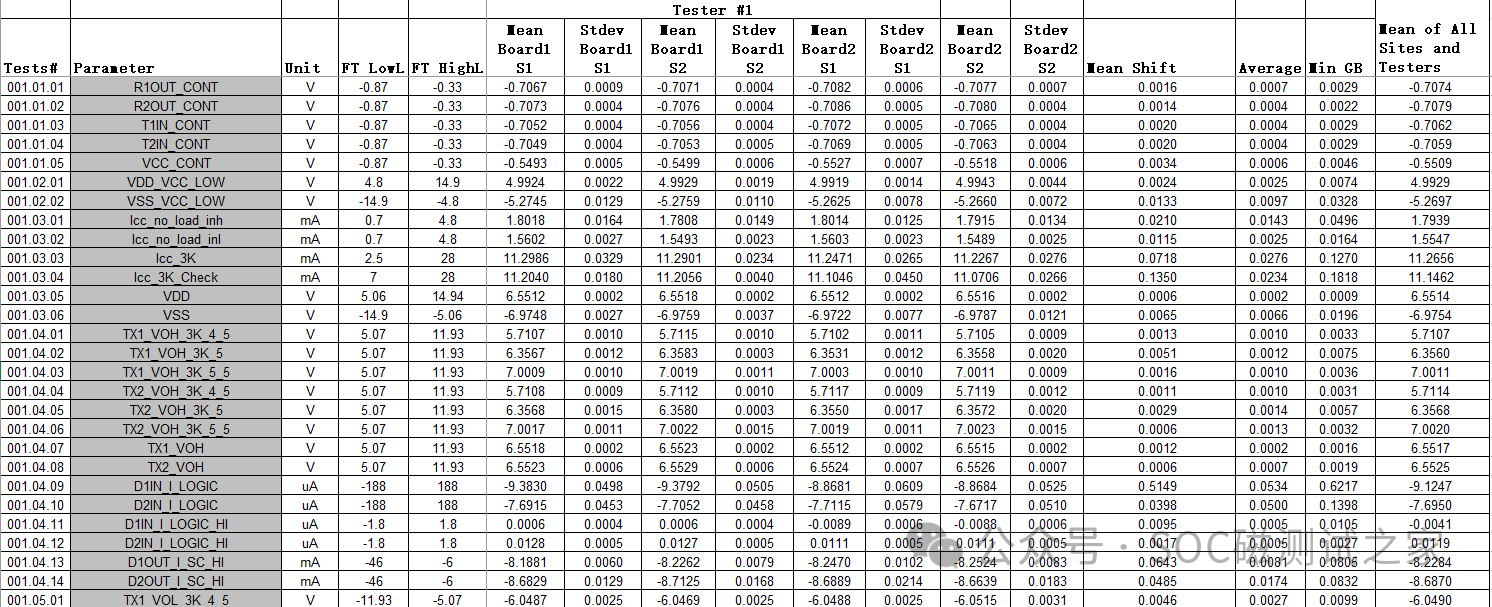

芯片测试中的防护带GuardBand在芯片测试流程中,防护带(Guardband)是确保产品可靠性的重要技术手段,通过设置安全裕度来补偿测试系统的潜在误差。每次测量都会受到误差的影响:系统的和随机的。通过校准进行修正能够减少系统误差。更准确地说,重复测量(减少随机误差)并不会减少误差,但其平均值会更好地贴近实际值,从而减少偏差。不同测试阶段(WAT、CP、FT)的防护带应用策略存在明显差异:  图1:GuardBand的位置示意图 1. WAT测试:工艺监控为主WAT测试的核心是监控晶圆制造的工艺稳定性,主要通过测量划片槽内测试结构的电性参数(如电阻、电容、晶体管阈值电压等),判断工艺偏差是否可控。· 防护带特点 这里没有传统意义上的防护带,因为测试限值直接基于工艺设计规则设定,无需额外收紧。 间接防护作用 若WAT参数超标,晶圆会直接报废,相当于从源头拦截了后续可能流入CP/FT测试的边缘芯片,形成一种系统级的防护机制。  图2:Min GuardBand的计算逻辑和算法 2. CP测试:聚焦封装前的参数裕度CP测试在封装前筛选晶圆上的裸片(Die),其防护带的核心作用是应对封装环节可能引发的参数漂移。· 关键策略 o 限值加严 CP测试的限值通常比FT更严格。例如某电源芯片的导通电阻(Rdson),CP要求≤50mΩ,而FT放宽到≤55mΩ,预留的5mΩ裕度专门用于覆盖封装过程中的热应力等变异。 o 测试项选择 仅执行封装后无法复测的项目(如栅极漏电流Igss),并规避探针电流限制(≤10A)导致无法进行的大电流测试,后者会留到FT阶段完成。

|

| 测试阶段 | 防护带作用 | 典型操作 | 主要考量 |

| WAT | 工艺超标拦截 | 参数直接对标设计规则 | 工艺稳定性(Cpk≥1.33) |

| CP | 覆盖封装参数漂移 | CP限值比FT严(如:CP上限=FT上限-温度shiftoffset) | 封装变异、测试项选择性 |

| FT | 覆盖客户端风险+测试系统误差 | 关键参数追加裕度(如高温限值压缩10%) | 三温覆盖、机台误差补偿 |

核心逻辑与趋势

· 分层防护WAT从工艺源头拦截风险,CP在封装前剔除参数边缘芯片,FT最终拦截系统级缺陷,形成递进式防护体系。

· 成本平衡

CP阶段防护带过严会推高良率损失成本,而FT阶段过松则可能导致客户端失效,需在可靠性与成本间精细权衡。

· 技术演进

传统固定裕度正被AI动态防护带取代——通过实时分析机台误差自动调整限值,提升效率的同时减少误判。

结语

防护带的本质是在不确定中建立确定性。从晶圆厂到终端产品,通过精准匹配不同测试阶段的策略,芯片制造得以在可靠性保障与成本控制间找到最优解。随着智能化技术的渗透,防护带正从被动防御转向主动预测,逐步逼近“零缺陷”的理想目标。