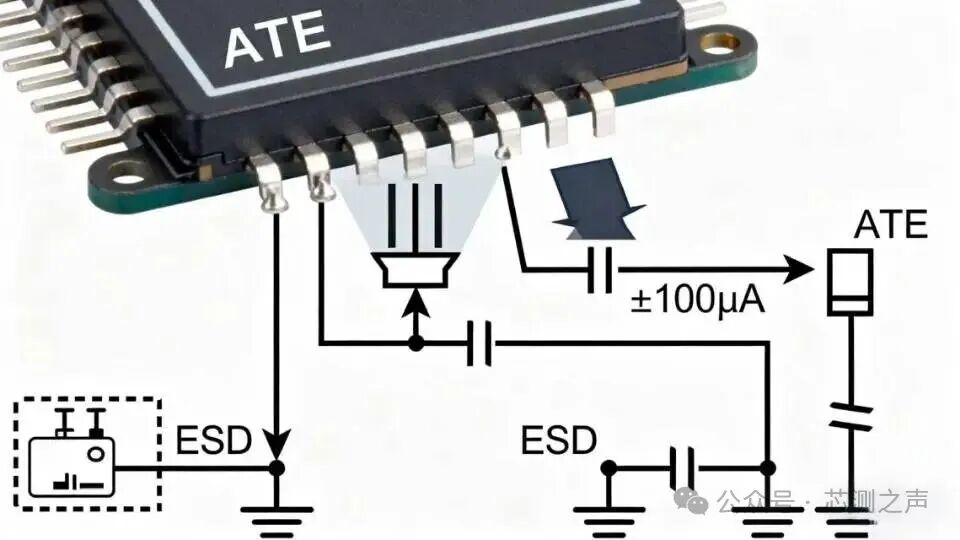

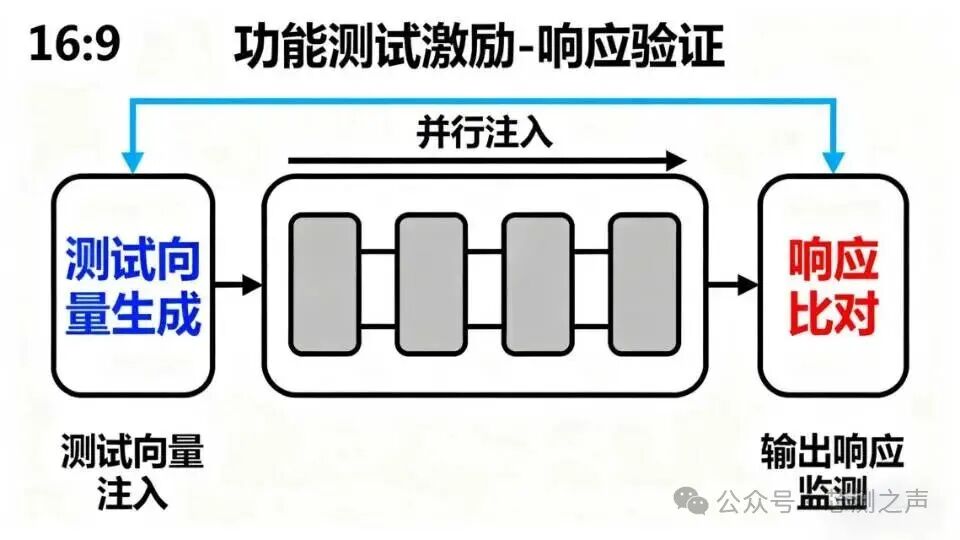

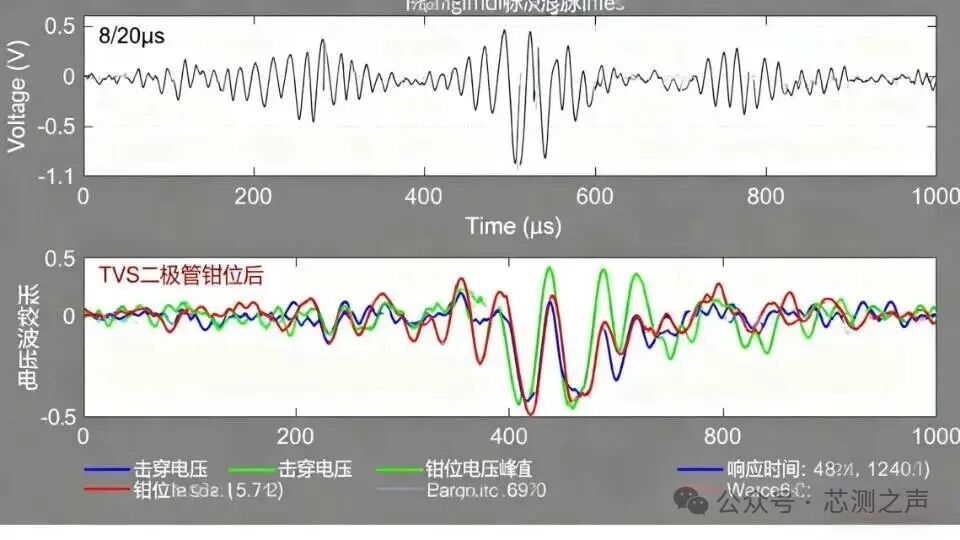

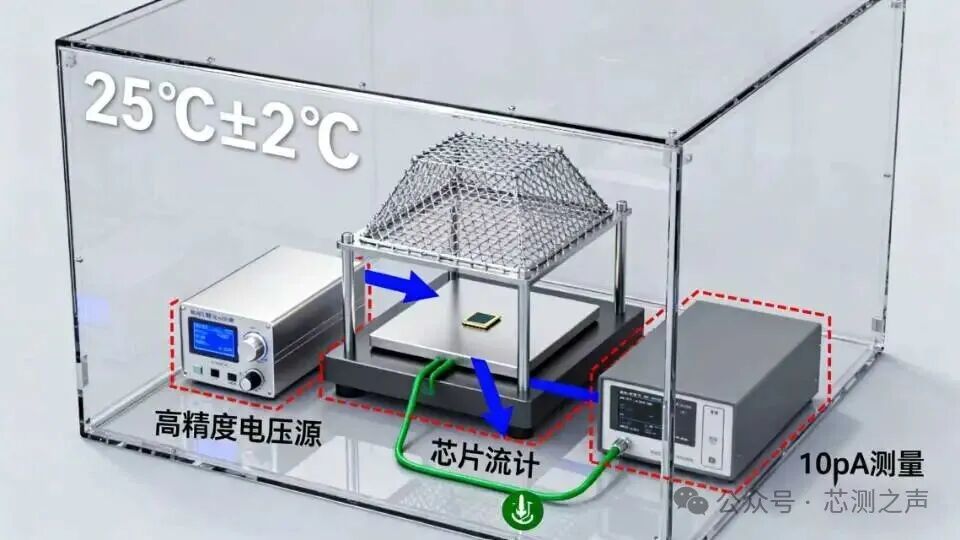

芯片测试四大核心技术解析!连接性 / 功能 / 钳位电压 / 漏电流原理大揭秘芯片从设计到量产,测试是保障品质的关键环节。其中连接性、功能、输入钳位电压和漏电流测试,堪称芯片出厂前的 “四大体检项目”。今天就带大家通俗搞懂这四项测试的核心原理,看懂芯片如何通过 “层层考核”!一、连接性测试:芯片的 “基础电路体检” 连接性测试是芯片测试的第一步,相当于给芯片做 “基础电路体检”,快速排查封装环节的潜在问题。 其核心原理主要依赖三点: 借助芯片引脚内置的 ESD 保护二极管,这些二极管与电源或地并联,正常工作时不干扰信号,测试时通过微小电流可使其正向导通,成为检测媒介。 采用电流 - 电压测量逻辑,所有引脚接地后,ATE 设备向被测引脚施加 ±100μA 电流,根据欧姆定律通过测量电压判断状态,趋近 0V 为短路,超过钳位值为开路。 考虑材料差异影响,硅衬底和锗衬底二极管导通压降不同,需设定对应电压上下限,超出范围即判定异常。 测试方式分为串行和并行两种:串行逐脚测量精度高但耗时久,并行多脚同步测量效率高,不过需通过分组优化解决 Pin-To-Pin 短路检测难题。  二、功能测试:芯片的 “实战能力考核” 如果说连接性测试是查 “硬件通不通”,功能测试就是考 “软件好不好用”,验证芯片能否实现设计功能。 核心原理围绕两大核心: 采用激励 - 响应验证机制,向芯片输入预设的测试向量(相当于 “指令”),监测输出响应是否与预期一致,比如通过扫描链技术实现内部寄存器状态的完全可控可观测。 精准匹配真实工作场景,模拟芯片实际工作频率下的信号交互,检测时序是否合规,避免实际使用中出现数据采样错误等问题。 测试时先通过需求分析生成测试向量,再采用多通道并行策略注入向量,大幅缩短测试时间,某 SoC 芯片通过 4 路并行测试,单颗测试时间从 800ms 降至 220ms,产能提升显著。  三、输入钳位电压测试:芯片的 “防雷击护盾检测” 输入钳位电压测试专门验证芯片的瞬态过压保护能力,就像检测芯片的 “防雷击护盾”,保障复杂环境下的稳定性。 核心原理基于两大特性: 利用 TVS 二极管的雪崩击穿特性,当输入电压超过击穿电压时,TVS 二极管迅速导通,将电压钳位在安全范围,避免下游电路受损。 采用 8/20μs 标准浪涌脉冲模型,模拟真实场景中的瞬态干扰,通过调整脉冲电流(最高可达 10kA),评估器件的能量吸收能力。 测试时通过脉冲发生器施加特定波形的脉冲,用示波器捕获电压波形,提取钳位电压峰值,连续多次测试确保稳定性,比如工业 PLC 芯片需通过 6kV 接触放电测试,钳位响应时间需小于 1ns。  四、漏电流测试:芯片的 “节能与绝缘检测” 漏电流测试聚焦芯片的功耗控制和绝缘性能,既是 “节能检测”,也是 “绝缘体检”,尤其对低功耗芯片至关重要。 核心原理包含两个关键点: 基于欧姆定律的高精度测量,向芯片施加恒定电压(如最大工作电压),通过高精度设备测量微小漏电流,分辨率可达 10pA,能检测 1GΩ 以上的绝缘电阻。 利用 PN 结反向特性,正常情况下反向偏置的 PN 结漏电流极小,若漏电流异常增大,往往意味着结区存在掺杂不均等缺陷。 测试需在严格控制的环境中进行,温度保持 25℃±2℃,同时做好电磁屏蔽和接地处理,避免环境噪声影响测量精度,确保检测出栅氧退化、PN 结缺陷等潜在问题。  芯片测试是保障产品可靠性的最后一道防线,这四项测试层层递进,从基础连接到功能实现,从环境适应到能耗控制,全方位守护芯片品质。无论是大规模量产还是高端芯片定制,精准的测试都能有效降低成本、提升产品竞争力。 |