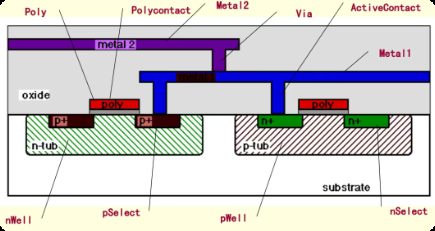

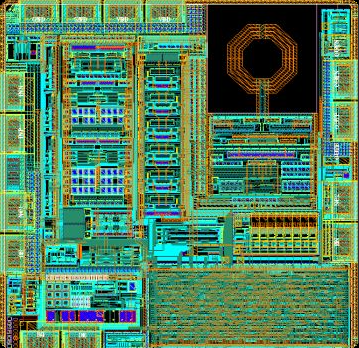

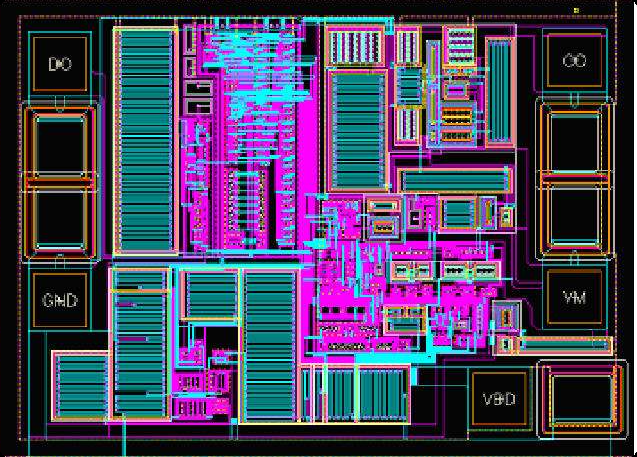

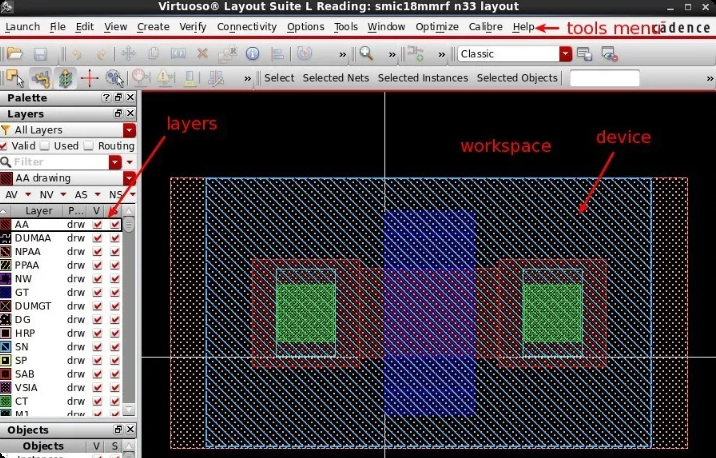

在集成电路设计中,版图(Layout)是芯片设计的核心环节之一,指芯片电路的物理实现图。它描述了电路中所有元器件(如晶体管、电阻、电容等)及其连接方式在硅片上的具体布局。版图是将电路设计转化为实际可制造物理形态的关键步骤,类似于建筑设计中平面图到实际结构的转化。 核心组成与目标 版图设计作为芯片设计的后端环节,主要任务是将逻辑电路和功能模块转化为物理布局。其核心内容包括: 元器件布局:根据设计需求合理安排标准元器件(如逻辑门、存储单元等)的位置,需兼顾功能实现、信号传输速度和电源供给效率; 金属互连:通过金属层连接元器件,需精确选择金属层并考量线宽、间距,确保信号可靠性和时序准确性;  电源与地线布局:科学规划电源线(VDD)和地线(GND),保障全芯片电力供应稳定,抑制电源噪声干扰; 隔离与保护:设计隔离措施防止信号串扰,并对高功率区域实施有效散热方案。 版图设计的核心目标是在确保电路功能正确的前提下,最大化电路性能并满足质量要求。具体包括:实现预定电路功能;通过优化布局布线缩短连线长度,降低信号延时以提升速度;最小化芯片面积以降低成本;保证设计的可靠性和可制造性,使其能成功生产并长期稳定工作。 关键步骤与规则约束 版图设计需遵循严谨的流程: 综合(Synthesis):利用工具将高级描述语言(如Verilog/VHDL)转化为标准单元(Standard Cells),为物理实现奠定基础; 布局(Place):确定每个标准单元在芯片上的具体位置,需综合考量面积限制、信号传输距离和电源分布,目标是优化性能和降低功耗;  布线(Route):完成元器件间的物理金属连线,需最小化传输延迟并规避信号干扰及时序问题。 设计规则是版图必须遵循的核心准则,由制造商制定,是设计与工艺间的接口。规则分为: 绝对值规则:以实际尺寸为单位(如金属层最小宽度100纳米); 相对值规则:基于比例因子定义(如宽度w = mA)。常见要求包括:保证导线可靠性的最小宽度;防止短路的最小间距;利于光刻对齐的最短露头;避免元件相互影响的边界距离。 几何形状上,版图普遍采用“曼哈顿几何”,即由水平或垂直直角线段构成。这符合光刻工艺对精度与稳定性的要求,也便于规则检验和自动化布线工具处理。 挑战与发展 1.挑战 时序问题:布局不当导致信号传播延迟,需通过时序分析确保信号准时到达; 电源完整性:不合理电源线布局引发电压降落或噪声,需优化供电网络; 热管理:高功率区域布局不佳引致局部过热,需考量热分布并设计散热方案。 2.验证 静态时序分析(STA):检查信号传播延迟,预防时序违例; 设计规则检查(DRC):确保版图符合工艺物理规则(线宽、间距等); 版图与原理图一致性检查(LVS):确认版图功能与原始电路图一致。  3.趋势 更小尺寸与更高集成度:7nm及以下制程使设计规则更严苛,需应对更多物理效应; 3D IC技术:芯片垂直堆叠带来布局布线新挑战,需解决层间热管理和信号传输问题; 智能化EDA工具:AI技术推动工具自动化,可自动识别并优化设计瓶颈。 版图设计是集成电路从逻辑到物理实现的核心环节,其价值在于将抽象电路转化为可制造的硅片布局。它远非简单的元器件排布,而是需统筹时序、电源、散热等多维因素的复杂工程,直接影响芯片性能、功耗、成本和可靠性。随着工艺演进和新技术涌现,版图设计将持续面临挑战,同时也将借助创新工具不断推动芯片向高性能、高集成度发展。 |