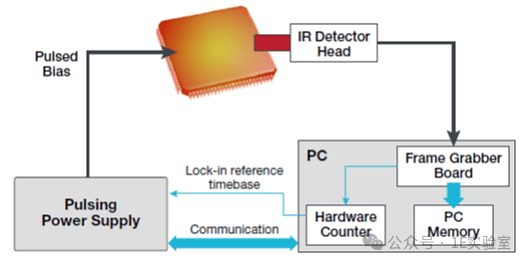

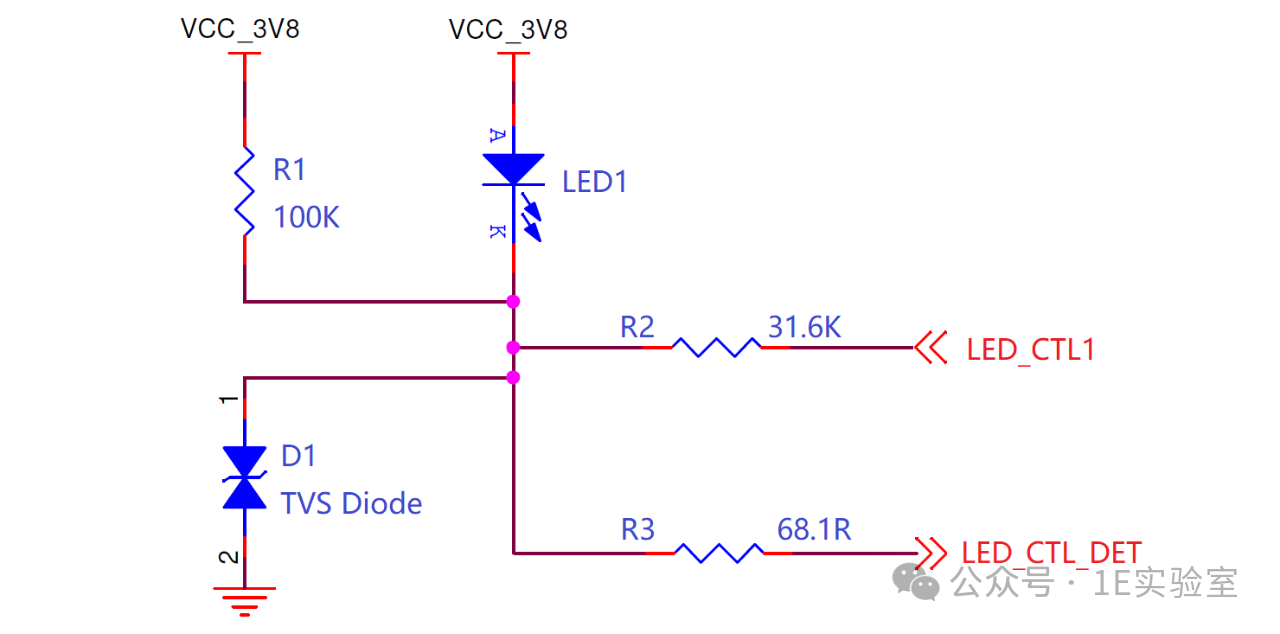

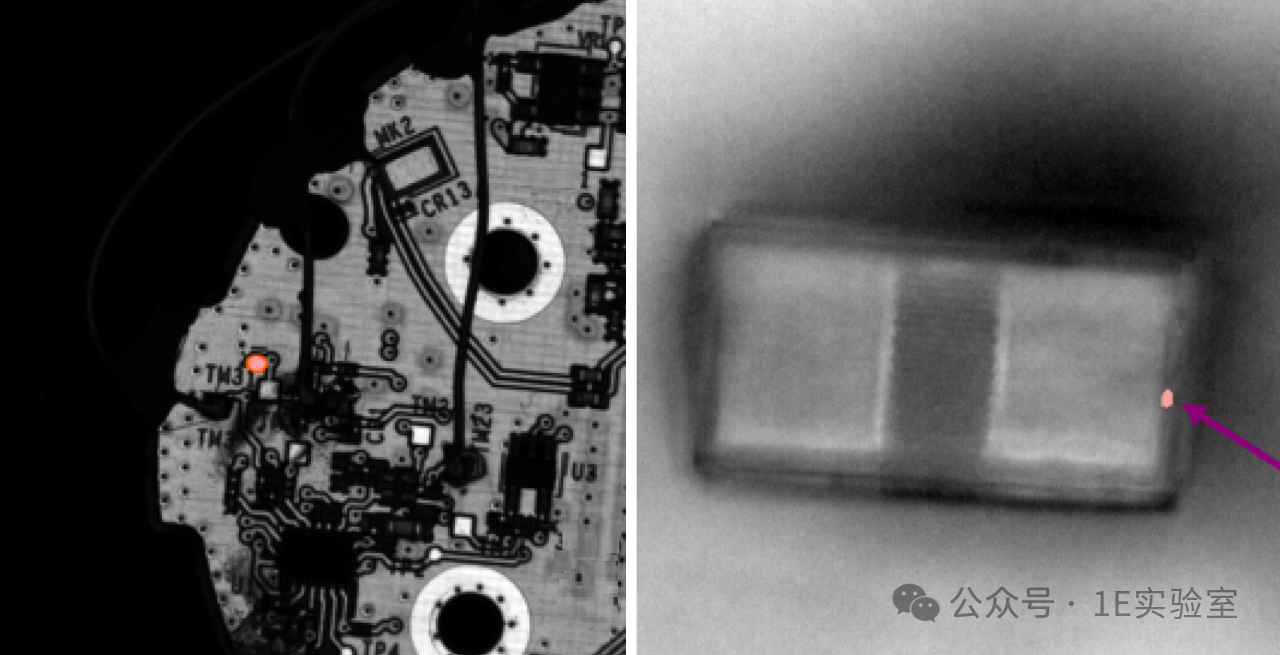

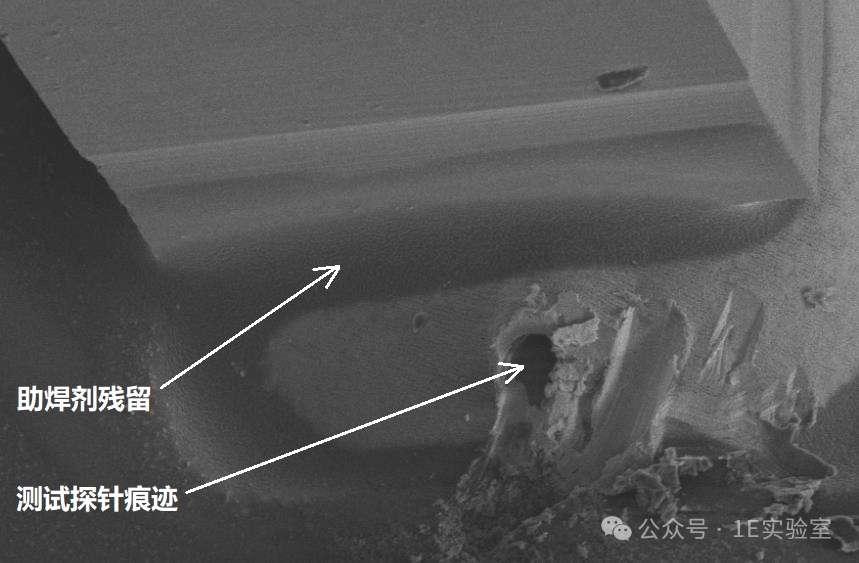

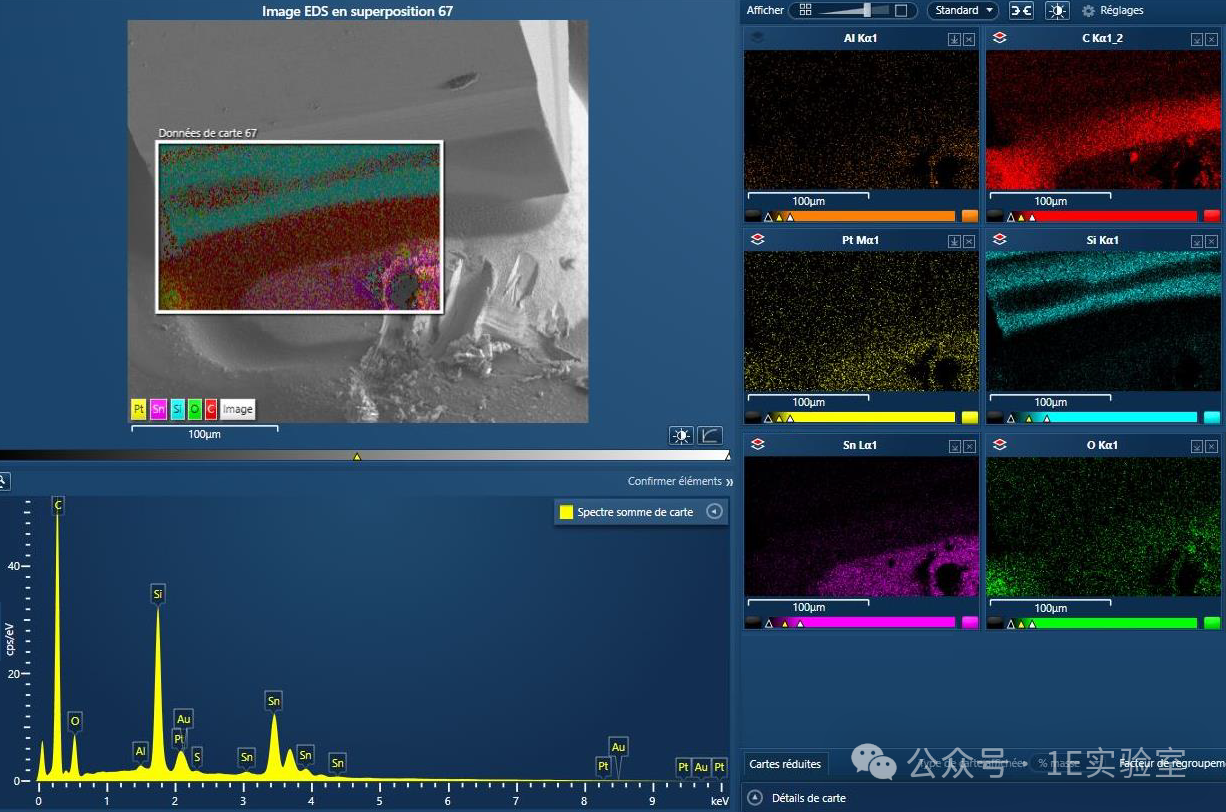

在WLCSP封装TVS管的异常漏电分析(一)中,我们从电路板和器件两个层面分析了WLCSP封装TVS管出现异常漏电的原因,发现是由于PCB焊盘设计过大,使得焊接时焊锡溢出,接触到了芯片侧面裸露的硅基体,从而导致了异常漏电。 ▲ 异常漏电的TVS管(尺寸0.6*0.3*0.3mm) 由于硅材料本身不沾锡,在普通光学显微镜下很难判断焊锡是否真的接触到了芯片侧壁,因此不能直接证明这就是漏电的根本原因。为此,本文将采用锁相热成像(LIT)、扫描电子显微镜(SEM)和能量色散X射线光谱(EDX)等先进分析技术,深入观察焊锡与器件侧壁的接触情况,并试图找出导致漏电的根本原因。 1. 锁相热成像(LIT)分析 锁相热成像(Lock-in Thermography, LIT)也称锁定热成像,是一种基于热激励+红外热成像+锁相检测技术的高灵敏度非破坏性检测方法。它通过向样品施加周期性的热激励(光或电),并利用高分辨率红外相机捕捉样品表面温度变化,再通过锁相放大技术提取与激励信号同步的热响应信号,从而实现对电子器件热异常、电流泄漏等问题的高精度检测。 LIT的精度可达空间分辨率 5~20 um、温度分辨率 50~200 mK(0.05 ℃~0.2 ℃),结合锁相技术后信噪比提升至40~60 dB,可以定位微米级/微弱热异常,在电子失效分析中能精准定位故障点。  ▲ 典型的锁相热成像技术系统框图 图源:Tektronix 本案例中的热激励源为施加在 TVS 管D1 两端的电压。需特别注意的是,在测试前必须移除与 D1 相连的所有外围器件,包括电阻 R1。若不移除R1,电路板上仍存在“R1 → 其他使用3.8V 电源的芯片 → 地”的电流回路,从而干扰测试结果。  ▲ 电路图 下图是通过LIT技术观测到的 TVS 管热点分布图,对应的漏电流为487nA@2.7V。可以看出,热点位于TVS管第1脚的中间位置,该位置即为漏电发生的区域。  ▲ 通过LIT观测到的热点(漏电点) 2. 扫描电子显微镜(SEM)分析 扫描电子显微镜(Scanning Electron Microscopy, SEM)简称扫描电镜,是一种利用聚焦电子束扫描样品表面,并通过检测电子与样品相互作用产生的信号(如二次电子、背散射电子等)来获得高分辨率、高放大倍数图像的显微分析技术。 SEM具有高分辨率(可达0.1~1纳米)、大景深(比光学显微镜高数百倍)、放大倍数(10万倍以上)的特点,可提供样品表面纳米级形貌与三维结构信息,是微观分析的核心工具。  ▲ 扫描电子显微镜实物图 针对LIT定位的热点位置,光学显微镜及SEM观测结果如下:  ▲ TVS管热点位置照片  ▲ TVS管热点位置SEM照片 SEM分析显示,TVS管边缘存在助焊剂残留,并已覆盖侧面裸露的硅基体。虽然助焊剂的主要成分松香具有绝缘特性,但残留物中可能存在的微量活化剂及导电离子(如Cl⁻、Br⁻),仍可能导致局部漏电或电化学迁移风险。因此,高可靠性应用(如医疗、航天)必须彻底清除残留,而消费类电子产品在满足工艺要求的前提下通常可采用免清洗方案。 值得注意的是,SEM虽然是非破坏性的“成像”技术,但由于其前处理过程、电子束作用及真空环境的影响,极有可能对电子器件的电学结构和特性造成不可逆改变,从而导致后续的电性测试无法进行或结果失真。 3. 能量色散X射线光谱(EDX)分析 能量色散X射线光谱(Energy Dispersive X-ray Spectroscopy, EDX)又称EDS,是一种基于电子束激发样品产生特征X射线的元素分析技术。当高能电子束(如SEM的电子枪)轰击样品时,原子内层电子被激发,外层电子跃迁填补空位并释放特征X射线。通过检测这些X射线的能量和强度,可定性/定量分析样品中的元素组成。  ▲ EDX分析结果 根据EDX分析结果(左上图为检测区域,左下图为元素谱图),碳(C)、硅(Si)和锡(Sn)为主要成分,同时检测到铝(Al)、氧(O)、金(Au)、铂(Pt)及硫(S)。右图元素分布显示: o 碳(C):主要来源于松香或合成助焊剂中的碳氢化合物残留; o 硅(Si):对应TVS器件的硅基体; o 锡(Sn):源自焊点焊料。 初步结论是:TVS管侧壁存在明显的助焊剂残留(碳元素含量较高);由于电路板焊点的锡(Sn)元素干扰,无法确定焊锡是否直接接触TVS管侧壁。 在后续分析中,我们使用热风枪将TVS管从电路板上取下。由于解焊过程中TVS管侧壁可能接触到焊锡,导致TVS管单体的EDX分析结果存在不确定性。然而,所有取下的TVS管单体均未复现异常漏电现象,这表明: o 器件边缘的助焊剂残留或微量焊锡接触是导致漏电的根本原因; o 问题仅发生在器件焊接于PCB时的特定接触状态。 备注:一个更可靠的分析方法是直接使用机械外力完整取下TVS管单体,这样可以避免热风解焊带来的焊锡污染问题,从而获得更准确的分析结果。 根本原因与改善对策 分析表明,以下两种情况均会使TVS管在工作电压下产生漏电通路:一是助焊剂残留的导电离子在电场作用下形成离子迁移通道;二是焊锡与器件侧壁硅基体形成非预期的金属-半导体微接触。 综上,在器件选型和设计方面,我们应采取以下优化措施以提升产品可靠性: o 优先选择WLCSP封装器件,其自带锡球的结构设计可彻底消除侧壁接触风险; o 或选用全绝缘包封型TVS器件,通过物理隔离方式完全阻断漏电通道; o 严格遵循器件厂商的推荐设计规范; o 对于无锡球切侧壁裸露硅基材的器件,确保焊盘尺寸不超过其本体范围。 总结 本文通过锁相热成像(LIT)技术成功定位漏电相关的局部热点,并采用SEM/EDX联用技术对异常区域进行深入分析。SEM的高分辨成像揭示了器件侧壁的微观形貌特征,而EDX则通过特征X射线分析确认了助焊剂残留(含C、O等元素)及潜在的焊锡(Sn)接触,二者结合实现了形貌与化学成分的精准对应,为漏电机理分析提供了关键证据。 |