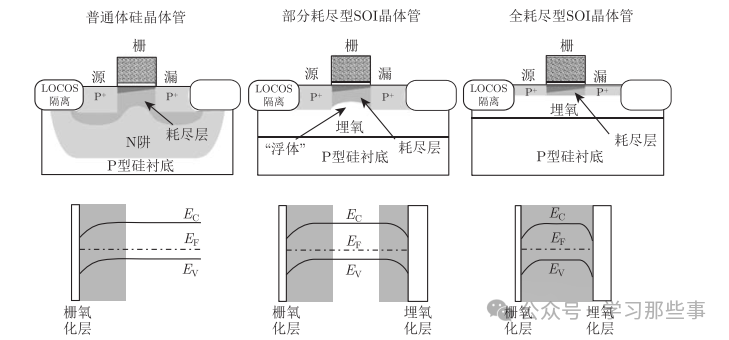

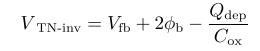

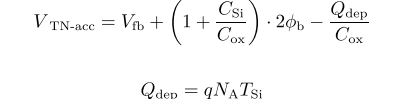

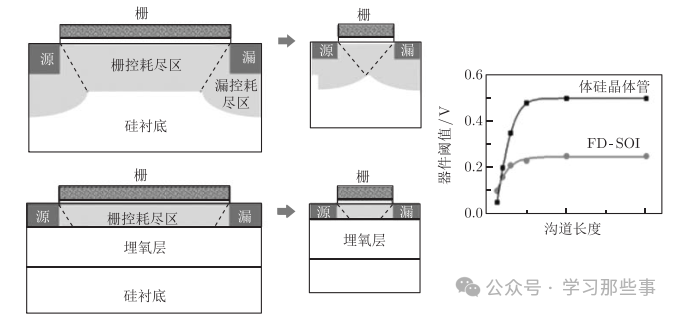

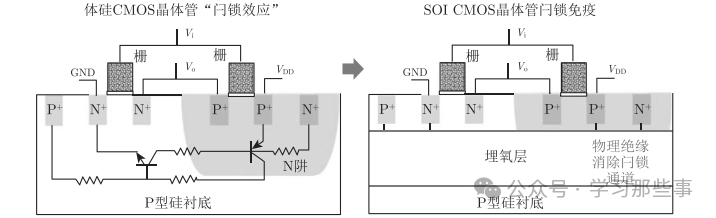

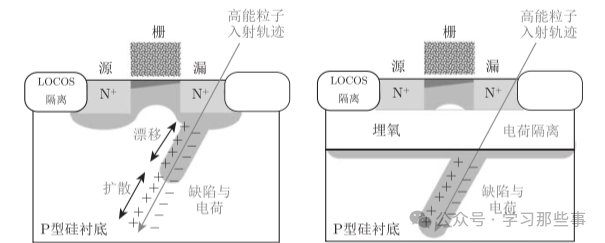

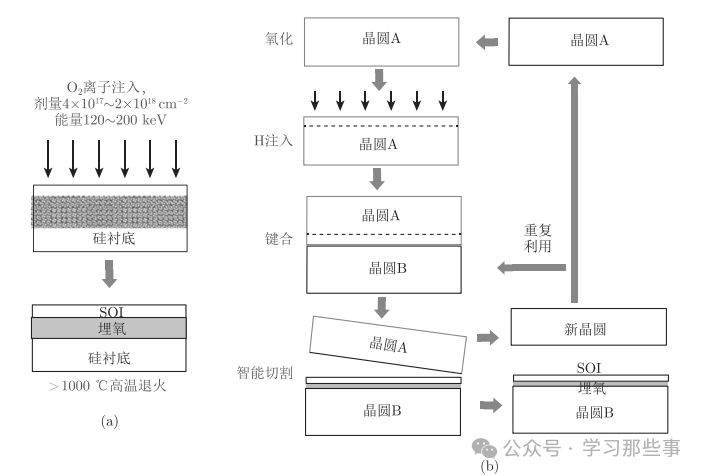

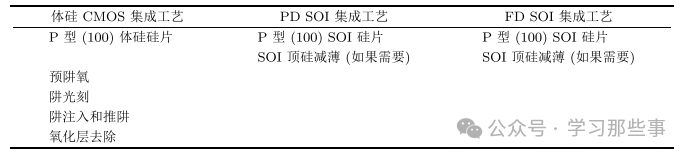

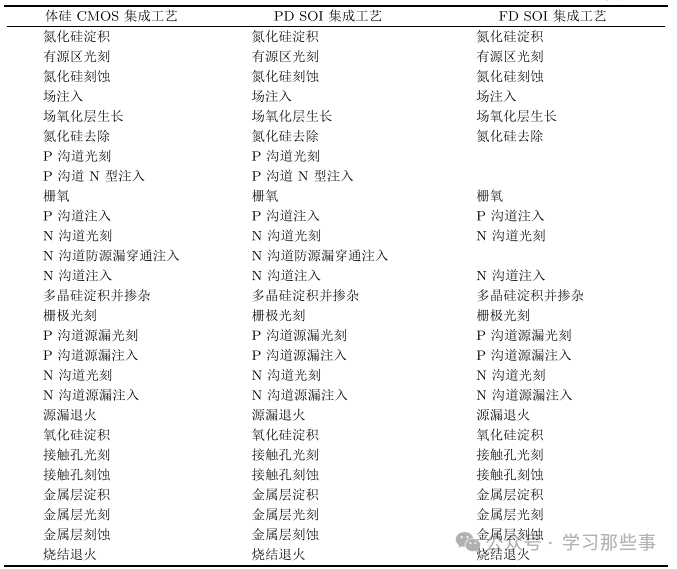

SOI集成电路技术概述2025 本文将介绍特殊的SOI集成电路,从器件类型与工作原理、器件与电路特性优势、衬底材料制备方法及集成制造工艺等维度展开系统阐述。 SOI器件类型和工作原理2025 绝缘体上硅(SOI)属于一类特殊的硅基CMOS集成电路,其核心特征在于硅基沟道与衬底之间存在一层绝缘介质层——这一独特结构为MOS场效应晶体管赋予了诸多差异化的电学特性。不同类型SOI器件的结构及工作原理如图1所示  SOI器件主要分为部分耗尽(PD)与全耗尽(FD)两大类别。其中,部分耗尽SOI(PDSOI)器件的沟道硅膜厚度较厚,其工作机制与传统体硅MOS晶体管更为接近;而全耗尽SOI(FDSOI)器件的沟道硅膜厚度较薄,工作过程中整个沟道会处于全耗尽状态,相较于体硅晶体管及PDSOI器件,具备更丰富的性能优势。 由于SOI器件的沟道通过背部绝缘介质实现隔离,因此存在背栅控制效应。当器件处于反型工作状态时(如沟道电势分布图所示),SOI器件会形成前后两个耗尽区。对于PD SOI器件,其沟道硅膜厚度(TSi)大于两个最大耗尽区宽度(TSi>2Xdmax),因此背沟道对前沟道的作用影响相对较弱;而FDSOI器件的沟道硅膜厚度(TSi)小于两个最大耗尽区宽度(TSi<2Xdmax),进而形成全耗尽沟道,此时前后栅极均会对器件的工作状态产生显著影响。 基于上述结构差异,PD SOI晶体管的阈值电压(以NMOS管的VTN为例)定义与体硅器件相近,可直接沿用体硅器件的相关表达式;而FDSOI晶体管的阈值电压定义则更为复杂——当器件分别工作在耗尽型与积累型两种模式下时,其阈值电压的定义存在明显不同,具体如公式所示:   式中,VTN-inv 为耗尽型 FD SOI 晶体管的阈值;VTN-acc 为积累型 FD SOI 晶体管的阈值;VFb 是平带电压;φb 为费米势;CSi 是 FD SOI 器件中导电沟道的耗尽电容;COx 是栅氧化层电容;Qdep 是沟道中耗尽电荷;NA 是沟道衬底掺杂浓度。这些定义中 VTN 都和整个硅膜中的耗尽电荷有关,受硅膜厚度控制。一般来说,TSi 越小,阈值越大,但是影响范围有限,需要通过其他方法来调节阈值。 SOI器件与电路特性优势2025 凭借独特的器件结构与工作模式,SOI器件具备一系列差异化的电学特性。SOI晶体管的沟道被埋氧层限定并与衬底完全隔离,这一结构带来双重技术优势:一方面能缩小源漏结的结深与面积,从而减轻短沟道效应、降低源漏寄生电容,最终提升电路运行速率;另一方面可通过背栅对器件阈值电压进行动态调节,显著增强低功耗电路设计的灵活性。因此,SOI技术广泛应用于低功耗集成电路制造领域,例如美国AMD公司的中央处理器(CPU),便采用SOI集成电路制造工艺以满足低功耗运行需求。 FDSOI器件拥有超薄沟道且运行于全耗尽模式,如图2所示,其沟道电荷受漏端耗尽电场的干扰显著降低,能有效抑制晶体管在尺寸微缩过程中出现的短沟道效应。与普通体硅器件相比,FDSOI器件的沟道静电势完整因子(EI)优势显著,具体体现为更弱的短沟道阈值滚降(Roll-off)现象及更低的漏致势垒降低(DIBL)漂移程度。  PDSOI器件因沟道通过介质隔离而缺少衬底电极,会导致多数载流子(多子)在沟道内部不断累积,进而造成沟道电势升高,引发“浮体效应”——这一效应会使晶体管输出特性出现电流骤增的Kink现象,需采取针对性措施抑制。而FDSOI器件因沟道始终处于全耗尽状态,多数载流子(多子)难以积累,因此不会产生电流Kink现象。 如图 3 所示,在 CMOS 集成电路中,SOI 器件的埋氧层能够阻断寄生 PNPN 晶体管的耦合反馈放大通路,从根源上抑制了体硅电路中普遍存在的闩锁效应 —— 这一特性对提升 SOI 集成电路的可靠性意义重大,也是 SOI 集成电路相较于常规体硅电路的核心优势之一。  在宇航、军用等特殊场景中,存在大量高能粒子(包括光子、重离子、质子、中子、电子等)辐射,这些辐射会在半导体材料与器件内部造成大量辐射损伤,致使集成电路无法稳定运行,因此需研发专用的抗辐射集成电路。如图 4 所示,当高能离子入射或穿透体硅 MOS 晶体管时,会在衬底材料内部产生大量辐射损伤电荷,这些电荷会严重破坏表面沟道的导电性,并显著影响器件阈值电压;而 SOI 晶体管因埋氧层的存在,能有效隔绝衬底材料中的辐射损伤电荷对表面沟道的作用,从而显著增强了器件与电路的抗辐照性能。此外,SOI 集成电路中,单粒子翻转(SEU)导致电路失效所需的能量传输密度远低于普通体硅集成电路,其优异的抗辐照加固能力使其在宇航与军工领域的集成电路中得到广泛应用。  SOI 衬底材料制备技术2025 与常规硅晶圆相比,SOI 衬底拥有特殊的材料结构,需通过专用工艺制备。当前主流制备工艺可分为外延生长、区熔重结晶、注入埋氧、键合与转移等几大类别。无论采用哪种工艺,其技术复杂度与成本均高于常规硅片,通常同尺寸 SOI 晶圆的成本为普通硅晶圆的 5~8 倍。在众多工艺中,注入埋氧(SIMOX)与智能键合与转移(Smart-cut)是目前制造 SOI 硅片的核心技术。 SIMOX 技术由日本东芝公司在 20 世纪 80 年代研发,是首个实现规模化量产的 SOI 衬底制备方案。其核心工艺流程如图 5(a)所示:向普通硅衬底内部大量注入氧原子,注入剂量需达到 5×10¹⁷cm⁻² 以上,随后进行高温退火处理,形成分布均匀的埋氧层。但由于氧原子注入呈曲线分布,表面硅层与埋氧层之间会形成较宽的过渡区,难以制备出高质量的超薄 FDSOI 晶圆。  Smart-cut 技术由法国 SOITEC 公司开发,其主要制造流程如图 5(b)所示:首先在衬底硅片 A 表面氧化生成隔离层,随后穿透该隔离层向下层硅内部大量注入氢原子,形成断裂层;接着将衬底硅片 A 倒置并与支撑硅片 B 键合,通过加热并施加外力使硅片在断裂层处分离;最后对残留的硅膜进行平坦化处理,即可制得 SOI 硅片。分离后的衬底硅片 A 可重复利用,大幅降低了工艺成本。该技术不仅避免了高剂量注入带来的缺陷,还能形成界面陡峭的过渡层,可用于制备超薄 FDSOI 晶圆,目前已应用于大规模 SOI 集成电路的实际生产中。 SOI 集成电路制造工艺2025 SOI 集成电路的制造工艺如表 1 所,与常规体硅集成工艺相比,两者多数工艺步骤一致。但受器件特殊结构影响,两者在器件隔离方式上差异显著 ——SOI 工艺通常采用台式隔离而非阱隔离来区分不同类型晶体管,因此省去了阱隔离工序。此外,FDSOI 集成电路因阈值电压定义不同,其阈值调控环节也得到了进一步简化。尽管 SOI 衬底成本有所上升,但整体集成工艺相较于常规体硅工艺更为简便,因此在特殊应用场景中具备独特优势。   想了解更多内容,享受更多权益可以加入我们的知识星球,在这里你可以提出问题,我们将竭尽全力为您解决! |