|

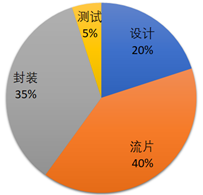

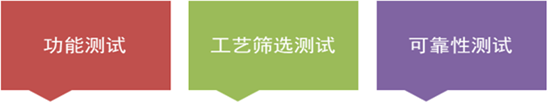

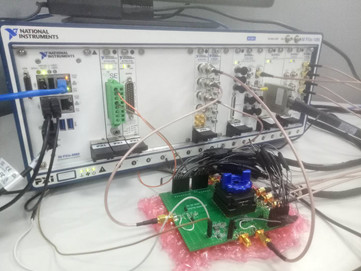

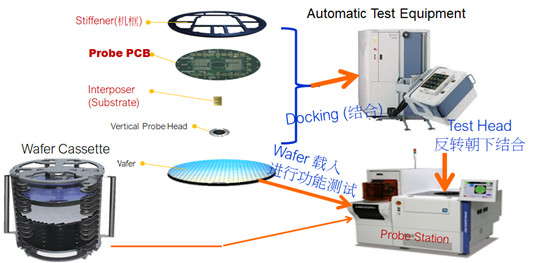

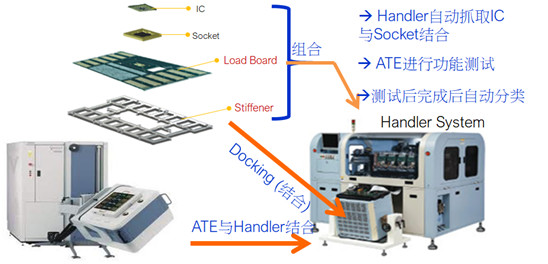

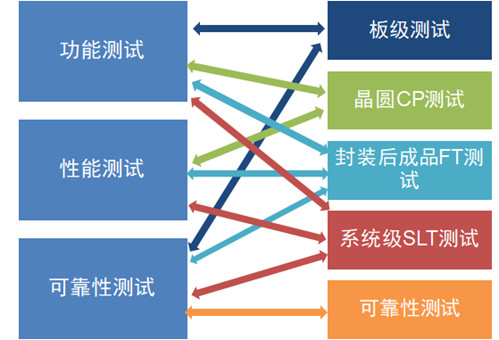

做一款芯片最基本的环节是设计->流片->封装->测试,芯片成本构成一般为人力成本20%,流片40%,封装35%,测试5%【对于先进工艺,流片成本可能超过60%】。  测试其实是芯片各个环节中最“便宜”的一步,在这个每家公司都喊着“Cost Down”的激烈市场中,人力成本逐年攀升,晶圆厂和封装厂都在乙方市场中“叱咤风云”,唯独只有测试显得不那么难啃,Cost Down的算盘落到了测试的头上。 但仔细算算,测试省50%,总成本也只省2.5%,流片或封装省15%,测试就相当于免费了。但测试是产品质量最后一关,若没有良好的测试,产品PPM【百万失效率】过高,退回或者赔偿都远远不是5%的成本能代表的。 芯片需要做哪些测试呢?主要分三大类:芯片功能测试、性能测试、可靠性测试,芯片产品要上市三大测试缺一不可。  功能测试看芯片对不对性能测试看芯片好不好可靠性测试看芯片牢不牢 功能测试,是测试芯片的参数、指标、功能,用人话说就是看你十月怀胎生下来的宝贝是骡子是马拉出来遛遛。 性能测试,由于芯片在生产制造过程中,有无数可能的引入缺陷的步骤,即使是同一批晶圆和封装成品,芯片也各有好坏,所以需要进行筛选,人话说就是鸡蛋里挑石头,把“石头”芯片丢掉。 可靠性测试,芯片通过了功能与性能测试,得到了好的芯片,但是芯片会不会被冬天里最讨厌的静电弄坏,在雷雨天、三伏天、风雪天能否正常工作,以及芯片能用一个月、一年还是十年等等,这些都要通过可靠性测试进行评估。 那要实现这些测试,我们有哪些手段呢?测试方法:板级测试、晶圆CP测试、封装后成品FT测试、系统级SLT测试、可靠性测试,多策并举。  板级测试,主要应用于功能测试,使用PCB板+芯片搭建一个“模拟”的芯片工作环境,把芯片的接口都引出,检测芯片的功能,或者在各种严苛环境下看芯片能否正常工作。需要应用的设备主要是仪器仪表,需要制作的主要是EVB评估板。  晶圆CP测试,常应用于功能测试与性能测试中,了解芯片功能是否正常,以及筛掉芯片晶圆中的故障芯片。CP【Chip Probing】顾名思义就是用探针【Probe】来扎Wafer上的芯片,把各类信号输入进芯片,把芯片输出响应抓取并进行比较和计算,也有一些特殊的场景会用来配置调整芯片【Trim】。需要应用的设备主要是自动测试设备【ATE】+探针台【Prober】+仪器仪表,需要制作的硬件是探针卡【Probe Card】。  封装后成品FT测试,常应用与功能测试、性能测试和可靠性测试中,检查芯片功能是否正常,以及封装过程中是否有缺陷产生,并且帮助在可靠性测试中用来检测经过“火雪雷电”之后的芯片是不是还能工作。需要应用的设备主要是自动测试设备【ATE】+机械臂【Handler】+仪器仪表,需要制作的硬件是测试板【Loadboard】+测试插座【Socket】等。  系统级SLT测试,常应用于功能测试、性能测试和可靠性测试中,常常作为成品FT测试的补充而存在,顾名思义就是在一个系统环境下进行测试,就是把芯片放到它正常工作的环境中运行功能来检测其好坏,缺点是只能覆盖一部分的功能,覆盖率较低所以一般是FT的补充手段。需要应用的设备主要是机械臂【Handler】,需要制作的硬件是系统板【System Board】+测试插座【Socket】。  可靠性测试,主要就是针对芯片施加各种苛刻环境,比如ESD静电,就是模拟人体或者模拟工业体去给芯片加瞬间大电压。再比如老化HTOL【High Temperature Operating Life】,就是在高温下加速芯片老化,然后估算芯片寿命。还有HAST【Highly Accelerated Stress Test】测试芯片封装的耐湿能力,待测产品被置于严苛的温度、湿度及压力下测试,湿气是否会沿者胶体或胶体与导线架之接口渗入封装体从而损坏芯片。当然还有很多很多手段,不一而足,未来专栏讲解。   测试类别与测试手段关系图 测试类别与测试手段关系图总结与展望芯片测试绝不是一个简单的鸡蛋里挑石头,不仅仅是“挑剔”“严苛”就可以,还需要全流程的控制与参与。 从芯片设计开始,就应考虑到如何测试,是否应添加DFT【Design for Test】设计,是否可以通过设计功能自测试【FuncBIST】减少对外围电路和测试设备的依赖。 在芯片开启验证的时候,就应考虑最终出具的测试向量,应把验证的Test Bench按照基于周期【Cycle base】的方式来写,这样生成的向量也更容易转换和避免数据遗漏等等。 在芯片流片Tapout阶段,芯片测试的方案就应制定完毕,ATE测试的程序开发与CP/FT硬件制作同步执行,确保芯片从晶圆产线下来就开启调试,把芯片开发周期极大的缩短。 最终进入量产阶段测试就更重要了,如何去监督控制测试良率,如何应对客诉和PPM低的情况,如何持续的优化测试流程,提升测试程序效率,缩减测试时间,降低测试成本等等等等。 所以说芯片测试不仅仅是成本的问题,其实是质量+效率+成本的平衡艺术!来源:「公众号: 湖杉资本」,谢谢! 拓展EMC知识:抗脉冲群干扰不合格从脉冲群试验的本意来说,主要是进行共模干扰试验,只是干扰脉冲的波形前沿非常陡峭,持续时间非常短暂,因此含有极其丰富的高频成分,这就导致在干扰波形的传输过程中,会有一部分干扰从传输的线缆中逸出,这样设备最终受到的是传导和辐射的复合干扰。针对脉冲群干扰,主要采用滤波(电源线和信号线的滤波)及吸收(用铁氧体磁芯来吸收)。采用铁氧体磁芯吸收的方案非常便宜也非常有效,但要注意做试验时铁氧体磁芯的摆放位置,就是今后要使用铁氧体磁芯的位置,千万不要随意更改,因为我们一再强调脉冲群干扰不仅仅是一个传导干扰,更麻烦的是它还含有辐射的成分,不同的安装位置,辐射干扰的逸出情况各不相同,难以捉摸。一般将铁氧体磁芯用在干扰的源头和设备的入口处为最有效。抗浪涌干扰试验不合格雷击浪涌试验的最大特点是能量特别大,所以采用普通滤波器和铁氧体磁芯来滤波、吸收的方案基本无效,必须使用气体放电管、压敏电阻、硅瞬变压吸收二极管和半导体放电管等专门的浪涌吸收器件才行。雷击浪涌试验有共模和差模两种,因此浪涌吸收器件的使用要考虑到与试验的对应情况。为显现使用效果,浪涌吸收器件要用在进线入口处。由于浪涌吸收过程中的di/dt特别大,在器件附近不能有信号线和电源线经过,以防止因电磁耦合将干扰引入信号和电源线路。此外,浪涌吸收器件的引脚要短;吸收器件的吸收容量要与浪涌电压和电流的试验等级相匹配。最后,采用组合式保护方案将能发挥不同保护器件的各自特点,从而取得最好的保护效果。 由射频场感应所引起的传导干扰抗扰度试验不合格从试验方式看,由射频场感应所引起的传导干扰抗扰度试验是共模试验,在经过前述几项试验(特别是静电放电、射频辐射电磁场和脉冲群试验)后,一般应无大碍,万一有问题, |