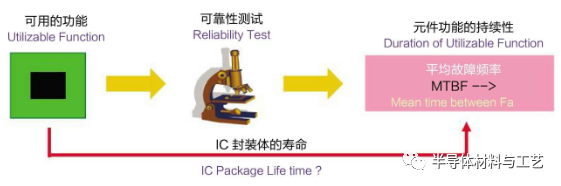

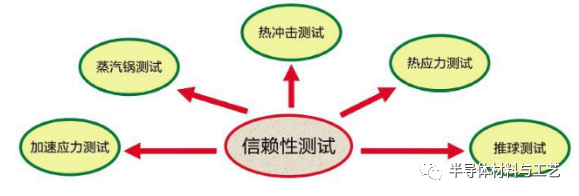

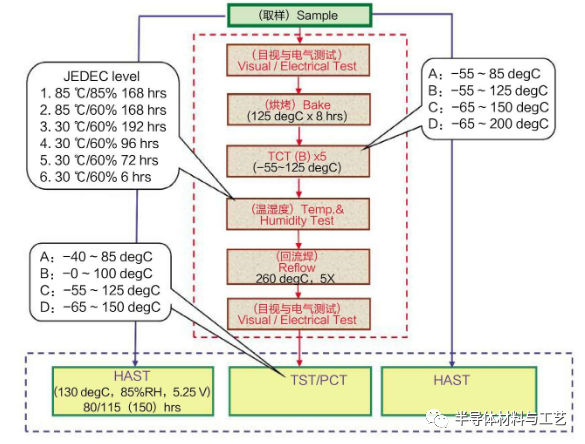

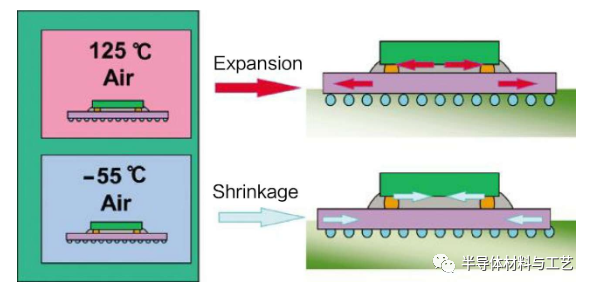

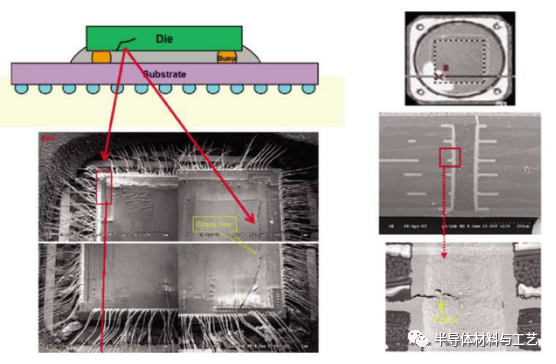

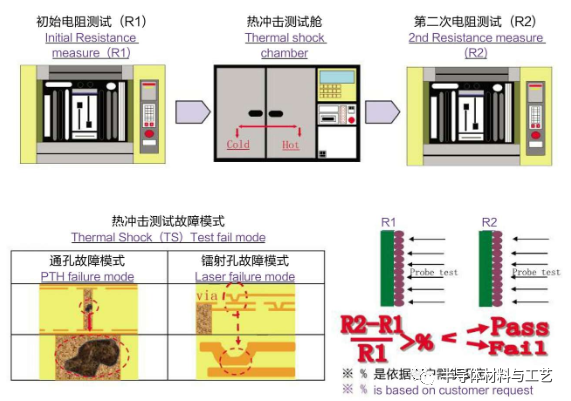

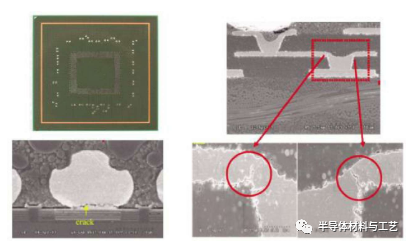

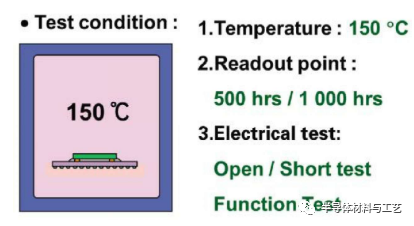

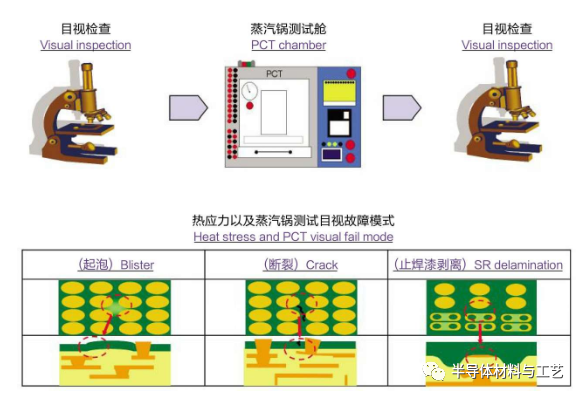

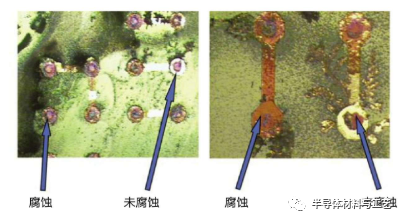

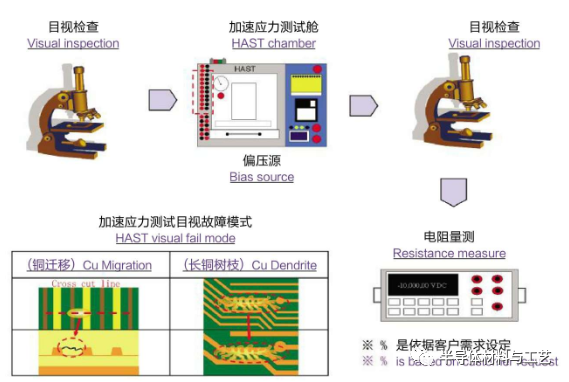

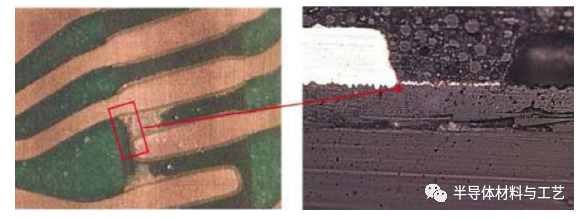

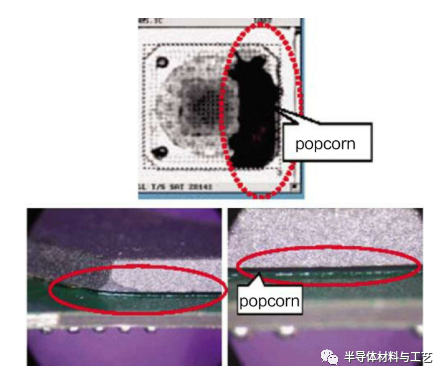

可靠性通常是指芯片封装组件在特定使用环境下以及一定时间内的损坏概率,换言之即表明组件的质量状况,也是电子产品未被商业化量产前与实际上市使用期间,产品性能和价值水平的总认定。所以封装厂必须对芯片封装组件的质量进行监控。如果说功能测试是检测产品目前的状况,那么可靠性测试就是预测产品在出厂后的使用质量。可靠性测试主要是产品在一些特定的状态(特定使用环境与一定时间),对产品寿命影响的评估,确认产品的质量是否稳定,同时进行最佳的修正。通常客户为了以最快、最经济的方式评估芯片的状况,会通过加速测试,即采用比芯片正常工作状况更严苛的条件来进行测试,以此大幅缩短测试时间,快速评估故障发生率。加速测试使用的前提是通过加速测试得到的故障机制必须和正常操作状况得到的故障机制相同,唯一的差别应该只有时间的长短差异,如此执行加速测试才有意义,否则就失去加速测试的初衷。一般常用的可靠性测试项目所选用的加速测试条件都与电压、湿度和温度等环境参数有关。  图1 可靠性测试示意图 芯片的可靠性在一定程度上可以说是芯片的寿命体现,作为一个质量控制和评估产品风险的工具,以及一个生产制造与材料供应的稳定度指标,可靠性成为客户在芯片上市量产前必须关注和研发改进的重要指标。在客户对产品质量有要求的前提下,可靠性测试的具体执行就有三大方向:验证什么,如何验证,到哪里验证。解决了这三个问题,质量和可靠性就有了保证,厂商才可以大量地将产品推向市场,也更容易获得消费者的青睐。 目前芯片载板封装的可靠性测试,大部分都是依照各个封装厂客户所要求的采购规范来执行,同时也会参照其他厂家或某些国际公认的可靠性规范来进行检测。以下是进行可靠性测试最常被采用的组织: (1)国际电工委员会(IEC) (2)美国军规(Milstd) (3)国际电子工业联接协会(IPC) (4)半导体工业标准组织(JEDEC) (5)日本工业标准协会(JIS) 通常芯片封装组件的可靠性测试都是围绕着温度、湿度及电压的影响因子,针对产品整体结构的电学性能和机械强度的检测来展开的。  图2 芯片载板封装常用可靠性测试示意图 各封装厂判断可靠性测试项目的标准不完全相同,以下就对目前市场上常用的芯片封装组件用到的可靠性测试项目作简单的归类及阐述。  图3 芯片封装的可靠性测试条件及流程示意图 通常封装厂对封装完成品要执行的可靠性测试项目会有六项,这六项测试项目有些可以同时进行,有些必须等待前面的项目完成后再执行。每个测试项目依采样方式,随机抽取一定数量产品的可靠性测试结果来判定是否通过测试。由封装厂确定抽样的规定与标准,每一家工厂各不相同,企业规模大的工厂的可靠性测试标准通常会较严苛。 以下分别对各项测试的内容与目的作说明: (1)温度循环测试(Temperature Cycling Test, TCT):是由热气腔和冷气腔组成,通过将封装体暴露在高低温气体转换的环境中,测试封装体抵抗温度差异化的能力。常见的测试标准为测试条件2,往复循环1000次,最终根据测试电路的通断情况判断测试是否通过。(见图4)  图4 温度循环测试示意图 测试目的:评估芯片产品中具有不同热膨胀系数的金属间接口的接触良率。方法是通过相对温度差异大的气体环境,从高温到低温往复变化。 测试条件:条件1: -55℃~125℃;条件2: -65℃~150℃。失效机制:电路的短路和断路、材料的破坏及结构机械变形。(见图5)  图5 TCT后的芯片封装失效缺陷图 (2)热冲击测试(Thermal Shock Test, TST):是通过将封装体暴露于高低温液体的转换环境中,测试封装体抗热冲击的能力。常见的测试标准为测试条件2,往复循环1000次,最终根据测试电路的通断情况判断测试是否通过。(见图6)  图6 热冲击测试流程及规范指标示意图 测试目的:评估芯片产品中具有不同热膨胀系数的金属间接口的接触良率。方法是通过循环流动的液体从高温到低温往复变化。测试条件:条件1: -55℃~125℃;条件2: -65℃~150℃。失效机制:电路的短路和断路、材料的破坏及结构机械变形。(见图7)  图7 TST后的导通线路断裂失效缺陷图 TCT与TST的区别在于TCT偏重于芯片封装的测试,而TST偏重于晶圆的测试。 (3)高温储藏试验(High Temperature Storage Test, HTST):通过将封装体长时间暴露于150℃的高温氮气炉中,测试电路通断路情况。(见图8)  图8 高温储藏试验规范指标示意图 测试的目的:主要在于测试长期高温状况下,例如150℃加热1000小时的情况,封装体中可能因为物质活性增强,物质迁移扩散而影响电路性能。测试的条件:温度:150℃;时间:500hrs/1000hrs;电性能测试:开路/短路测试。失效机制:电路的短路和断路、材料的破坏及结构机械变形。 (4)蒸汽锅测试(Pressure Cooker Test, PCT):俗称高压锅测试,主要测试封装产品抵抗环境湿度的能力,并通过增加压强来缩短测试时间。(见图9)  图9 蒸汽锅测试/热应力测试流程示意图 测试目的:评估芯片产品在高温、高湿、高压条件下对湿度的抵抗能力,加速其性能失效的过程。测试条件:130℃, 85%相对湿度,通电加偏压,锅内压力2个标准大气压。失效机制:化学金属腐蚀,封装塑封异常。(见图10)  图10 PCT后的金属电路失效缺陷图 (5)加速应力测试(High Accelerated Temperature and Humidity Stress Test, HAST):通过在高温高湿以及偏压的环境下,测试封装体抗湿度能力。(见图11)  图11 加速应力测试流程示意图 测试目的:评估芯片产品在偏压及高温、高湿、高气压条件下对湿度的抵抗能力,加速其失能过程。  图12 HAST后的金属电路失效缺陷图 测试条件:130℃,85%相对湿度,1.1伏特,通电加偏压,锅内压力2.3个标准大气压。失效机制:线路腐蚀,封装塑封异常。 (6)Precon测试(Precondition Test):是模拟芯片封装完成后,运输到下游组装厂装配成最终产品的过程中,针对产品会经历的可能环境变化所作的可靠性测试项目。模拟测试整个过程中有类似TCT和THT的测试。测试前先确认封装电器成品性能没有问题,然后开始各项恶劣环境的考验,先是TCT,模拟运输过程中的温度变化,目的在了解电子元器件的吸湿状况,再在恒温环境放置一段时间后(吸湿测试条件分为6个等级,依客户要求选用测试),再模拟后段焊锡加工过程,然后检查元器件的电器特性及内部结构是否失效。(见图13)  图13 Precon测试爆米花分层失效图 在Precon测试中最常见的问题有爆米花效应(Popcorn)跟分层(Delamination)失效等问题,这些问题都是因为封装体在吸湿后遭遇高温,内部水分变为气体,急速膨胀导致封装元器件受损造成的。 综上所述,一个好的电子产品,可以从可靠性的测试数据来预测,芯片封装体必须要具有较强的耐湿、耐热的能力,采用上述6个可靠性测试的验证,有利于反馈并改善封装设计管理,从而提高产品的可靠性。 芯片封装载板生产工艺发展了几十年,逐渐遇到生产制造的瓶颈,苹果公司已开始导入一种称为类载板制造方法(Substrate Like Process, SLP),给硬质载板的生产工艺带来了升级的机会。类载板生产工艺基本上是PCB硬板的一种方法,只是制程上更接近半导体较细线路的制造工艺,这种制造工艺、原材料和设计方案还可以发展出很多变化。类载板制造方法的出现,让高密度互连PCB厂商及现有的载板厂也可以生产,成为封装厂新材料供应商的新选择。 |