芯片失效分析解读

时间:2026-05-08 20:13来源: yiyi16833 芯侃 作者:ictest8_edit 点击:

次

芯片失效分析(Chip Failure Analysis, Chip FA)是针对半导体集成电路(IC)失效的系统性排查过程,旨在通过多维度检测与逻辑推理,定位失效位置、揭示失效机理(如电迁移、栅氧击穿、ESD损伤),并最终明确根因(如设计缺陷、工艺偏差、材料问题)。由于芯片结构微小(纳米级)、多层互连复杂(金属层/介质层堆叠),其分析流程需兼顾非破坏性优先、微观定位与机理验证,以下是针对芯片的典型失效分析流程与关键步骤:

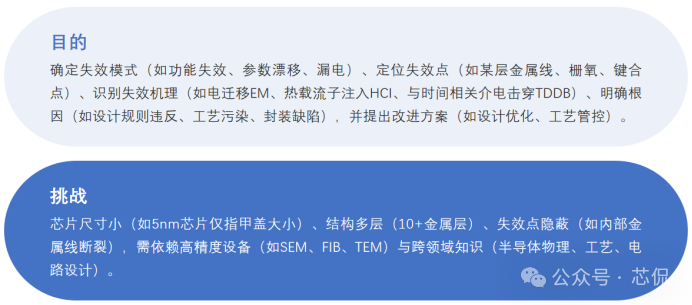

一、芯片失效分析的目的与挑战

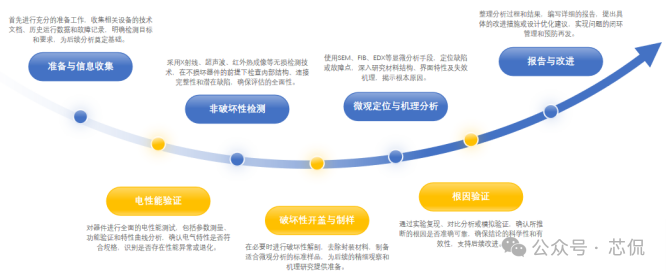

二、芯片失效分析的流程与步骤

芯片FA通常分为如下七大阶段,各阶段需紧密衔接,避免破坏关键证据。

1. 准备与信息收集:明确失效背景

此阶段需还原芯片失效的“场景画像”,避免盲目分析。

样品信息确认:芯片型号、批次(Lot)、晶圆编号(Wafer ID)、封装形式(如Flip Chip、Wire Bond)、生产日期等。

失效状态:失效是在测试中(如CP测试、FT测试)发现,还是客户端使用中(如高温、高压)出现?是否伴随异常(如冒烟、发热)?

失效现象描述:

功能失效:完全无输出、部分功能异常(如寄存器读写错误)、通信协议失败(如I2C无响应)。

电参数异常:静态电流(IDDQ)激增、输出电压偏移、漏电流(Ileak)超标、时序违规(如建立/保持时间不满足)。

关联数据收集:

同批次良率(Yield)、失效分布(如仅某一步光刻后失效)、测试日志(如ATE测试向量、失效引脚位置)。

客户端使用条件:供电电压(VDD)、环境温度(TA)、负载电流(IOUT)、是否经历ESD/浪涌事件。

工具与团队:组建跨部门团队(设计、工艺、测试、FA工程师),准备设备(如探针台、示波器、X-Ray、SEM),制定分析优先级(批量失效>单一样品)。

2. 电性能验证:确认失效可复现性

通过电测试锁定失效的具体表现,排除测试误差或偶发干扰。

功能复现测试:

使用ATE(自动测试设备)或手动探针台(Probe Station)连接芯片引脚,运行测试向量(Test Pattern),确认失效是否稳定复现(如同一测试项每次必败)。

示例:若芯片在“地址译码测试”中失败,需记录具体失效地址(如0x1234单元读取值错误)。

参数特性分析:

用半导体参数分析仪测量关键参数:

静态电流(IDDQ):若IDDQ远高于正常值(如μA级→mA级),提示存在漏电路径(如栅氧击穿、PN结反向漏电)。

栅氧完整性(GOI):施加斜坡电压(Ramp Voltage)测试栅氧击穿电压(VBD),若VBD低于规格(如5V→3V),可能为栅氧缺陷。

接触电阻(Rc):测量金属与硅的接触孔(Contact)电阻,异常升高可能因工艺污染(如金属沾污)或刻蚀过度。

IV曲线的测试:对失效PIN对地与电源进行测试,与好品进行对比。

失效定位(PFA, Physical Failure Analysis)前置:通过电测试缩小失效区域(如锁定某功能模块、某组I/O引脚),为后续微观分析提供方向。

3. 非破坏性检测:无损观察芯片结构与缺陷

优先采用非破坏性手段,保留芯片完整性,定位宏观或浅层失效点。

外观与X-Ray检测:

光学显微镜(OM):观察封装表面(如Wire Bond是否有断线、焊球脱落;Flip Chip是否有基板裂纹、锡膏空洞)。

X-Ray透视:检测内部结构(如Wire Bond线的弧度异常、Flip Chip焊球的空洞率(Void%)与开裂、芯片与基板间的分层(Delamination))。

示例:X-Ray发现某Wire Bond线根部断裂,可能原因为键合压力不足或金线污染。

红外热像(IR Thermography):

通电状态下扫描芯片表面,捕捉异常发热点(热点)。漏电或短路区域因焦耳热(I²R)会显示高温(如比周围高20℃以上)。

示例:热像图显示芯片左上角异常发热,提示该区域存在漏电通路(如金属线间短路)。

OBIRCH(光致阻变热成像):

对芯片表面扫描激光,通过检测电阻变化引起的温度变化定位微小漏电点(灵敏度达μA级)。适用于浅层(如顶层金属)缺陷定位。

示例:OBIRCH显示某金属线边缘有热点,可能为电迁移导致的局部变薄。

4. 破坏性开盖与制样:暴露芯片核心结构

若非破坏性检测无法定位深层失效(如内部金属线、栅氧),需通过开盖(Decap)去除封装,暴露芯片裸片(Die)。

开盖方法:

化学开盖:用浓硝酸(HNO₃)或硫酸(H₂SO₄)溶解环氧树脂封装(适用于塑料封装);氢氟酸(HF)溶解陶瓷封装(需严格控制时间与温度,避免损伤芯片表面)。

激光开盖:高精度激光(如UV激光)逐层剥离封装,减少对芯片的热损伤(适用于先进封装)。

注意事项:开盖前标记芯片方向(如划片道位置),避免混淆失效点与正常区域;开盖后清洁芯片表面(如用去离子水冲洗),去除残留酸液。

5. 微观定位与机理分析:从现象到本质

通过高精度设备观察芯片微观结构,结合半导体物理理论推导失效机理。

光学与电子束定位:

光学显微镜(OM)/扫描电子显微镜(SEM):观察芯片表面(如金属层、钝化层)的缺陷(如划伤、针孔、金属残留)。

示例:SEM观察到某金属线表面有“火山口”状凹坑,可能为电迁移导致的金属原子流失。

截面制样与分析:

聚焦离子束(FIB):通过离子束切割芯片,制备目标区域的截面(如金属线交叉处、栅氧层),精度可达纳米级。

透射电子显微镜(TEM):对FIB截面进行高分辨率观察(原子级),分析晶格缺陷(如位错、空洞)、界面质量(如金属-介质层间分层)。

示例:TEM显示栅氧层中存在纳米级针孔,导致栅氧击穿(TDDB机理)。

成分与缺陷分析:

能量色散X射线谱(EDS):配合SEM/TEM,检测微区元素成分(如Cl⁻污染提示腐蚀,Cu原子扩散提示电迁移)。

二次离子质谱(SIMS):分析元素纵向分布(如硼(B)扩散过深提示离子注入剂量异常)。

原子力显微镜(AFM):测量表面粗糙度(如化学机械抛光(CMP)后介质层不平整导致金属线桥接)。

6. 失效机理与根因验证

基于微观分析结果,结合工艺知识与实验验证,明确失效的根本驱动因素。

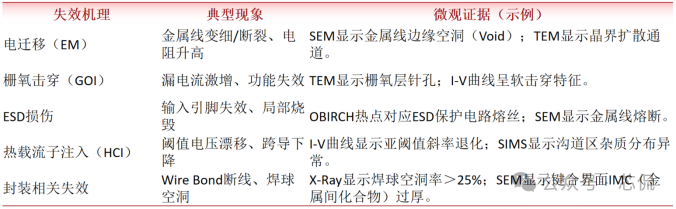

常见失效机理与对应证据:

根因验证实验:

设计验证:通过TCAD仿真模拟电迁移/栅氧击穿,验证设计规则(如金属线宽/间距是否符合电流密度要求)。

工艺验证:对比失效批次与良品的工艺参数(如光刻对准精度、刻蚀速率、退火温度),确认是否存在偏差(如某层光刻胶残留导致金属线桥接)。

材料验证:分析晶圆/封装材料的成分(如高K介质层的纯度),排除杂质污染(如Na⁺离子导致栅氧可靠性下降)。

7. 报告与改进:闭环预防

失效分析报告:包含失效背景、分析过程、关键证据(如SEM/TEM照片、EDS数据)、失效机理结论(如“芯片失效根因为顶层金属线电迁移,由设计电流密度超标(5mA/μm>规范3mA/μm)导致”)。

纠正与预防措施(CAPA):

设计端:优化金属线宽/间距(如加宽高电流路径)、增强ESD保护电路(如增加钳位二极管)。

工艺端:加强光刻对准监控(如使用Overlay测量)、控制刻蚀均匀性(如优化等离子体参数)。

材料端:升级封装材料(如使用低空洞率焊膏)、增加进料检验(如金属靶材纯度检测)。

三、芯片FA的主要设备与技术

定位类:探针台(Probe Station)、OBIRCH、红外热像仪、X-Ray。

观察类:光学显微镜(OM)、扫描电子显微镜(SEM)、透射电子显微镜(TEM)、原子力显微镜(AFM)。

制样类:聚焦离子束(FIB)、离子研磨(Ion Milling)、化学机械抛光(CMP)。

分析类:EDS(成分)、SIMS(深度剖面)、TEM(微观结构)、TCAD仿真(机理验证)。

总结

芯片失效分析是“现象→定位→机理→根因”的逆向推理过程,需结合电性能测试、非破坏性检测、微观分析与工艺知识。随着芯片制程缩小(如3nm),失效机理更复杂(如量子隧穿、原子级缺陷),FA需依赖更先进的设备(如高分辨率TEM、AI辅助图像分析)与跨学科协作,最终实现“一次分析,彻底解决”的可靠性目标。

|

------分隔线----------------------------