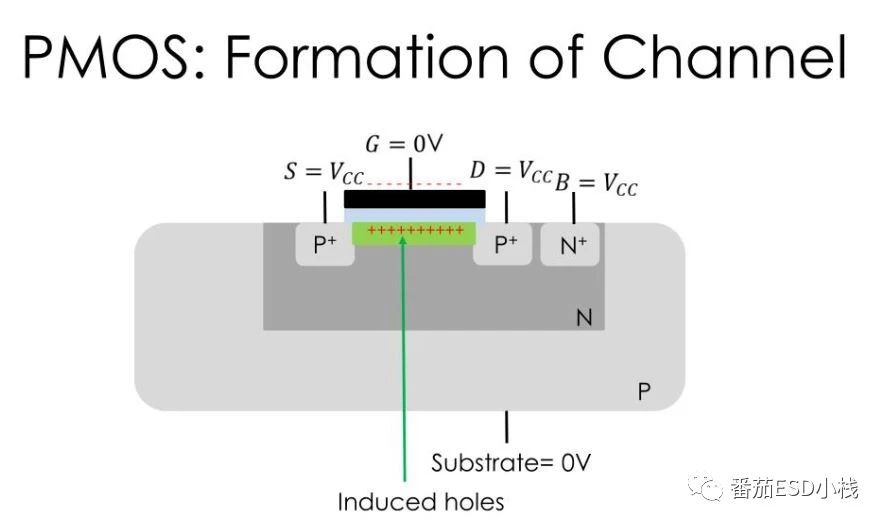

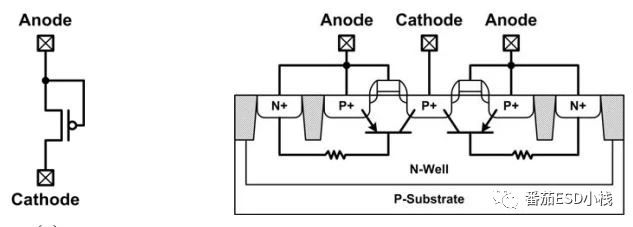

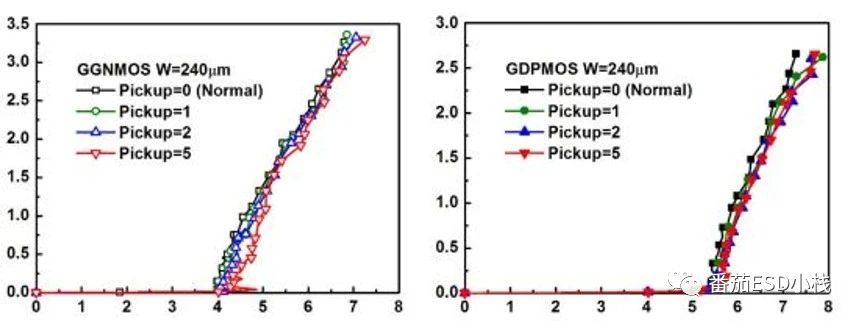

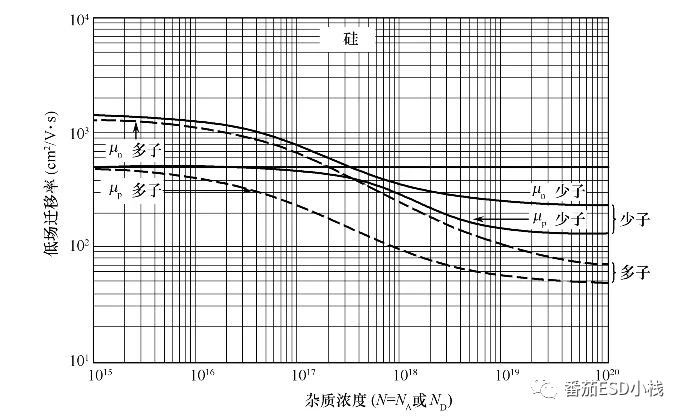

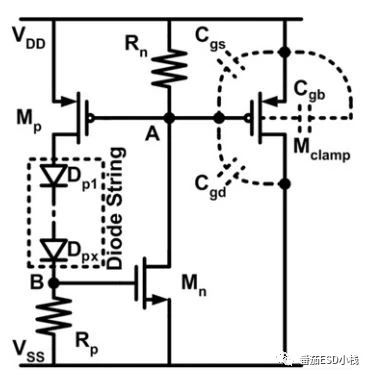

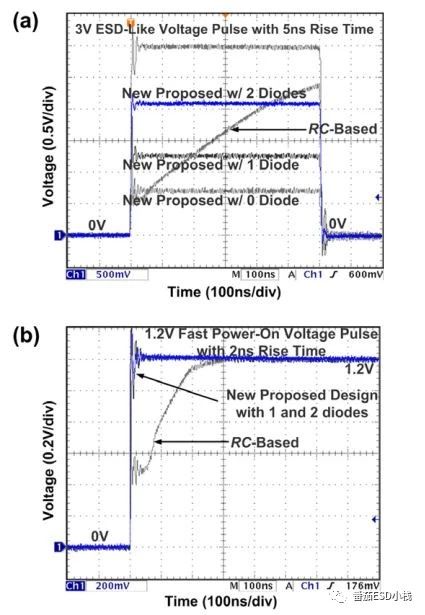

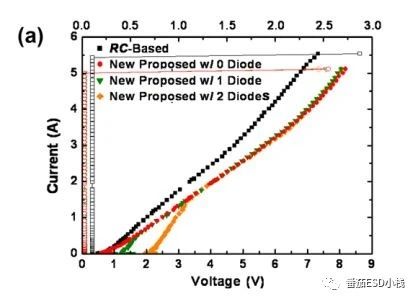

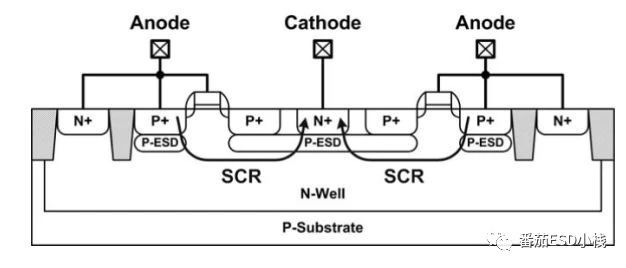

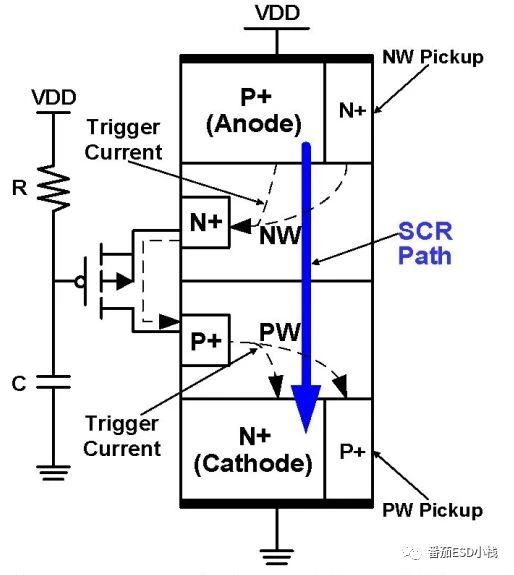

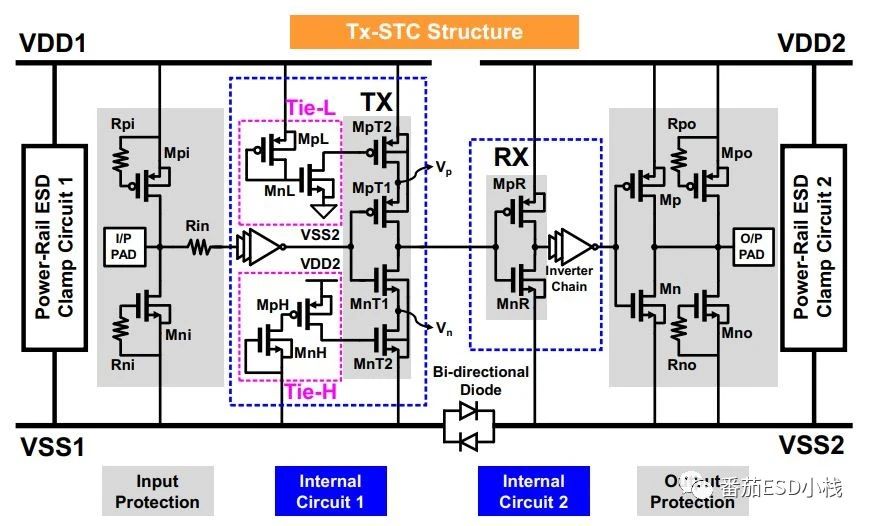

PMOS也是ESD防护中常见的有源器件,其工作原理与NMOS类似,且PMOS内部也有寄生三极管/二极管。这期就讲一下PMOS在ESD中的应用。一.PMOS在ESD防护中的机理。 图一所示为PMOS结构示意图,PMOS的正常工作机理这里就不赘述,只说一下其在ESD防护中的作用机理。  图一.PMOS结构图 PMOS作为ESD防护器件,按工作机理可以大体上分为两类: 1.依靠内部寄生三极管进行泄放,最典型的是GDPMOS(Gate VDD PMOS),如图二所示。  图二.GDPMOS示意图。 GDPMOS中P+/N-WeLL/P+构成一个寄生三极管,ESD电流击穿N-WeLL/P+界面后,该三极管导通,实现对ESD电流的泄放。其机理与GGNMOS类似,但是因为PMOS的特质,相较GGNMOS其Snap-Back会弱很多,如图三所示。而GDPMOS面对反向ESD脉冲时也是依靠内部寄生二极管泄放,Drain P+/N-WeLL。(有些GDPMOS会在栅极连一个电阻,其原理与GGNMOS栅连电阻大同小异,就是利用一部分栅耦效应,降低Trigger Voltage)。  图三.GDPMOS与GGNMOS TLP曲线对比。 2,依靠沟道实现ESD泄放,GCPMOS(Gate Couple PMOS)这种结构的机理与GCNMOS基本一致,通过ESD detector电路对ESD电流进行检测并产生感应电压,然后开启PMOS的沟道。需要注意是PMOS的开启电压是低电平。 二.PMOS与NMOS在ESD防护中的优劣势。 因为PMOS中的载流子是空穴(空穴是为了便于描述而虚构的概念),而空穴是位于价带之中,其有效质量远大于电子,所以NMOS与PMOS的载流子迁移率也有较大差距,如图四所示。  图四.NMOS与PMOS的载流子迁移率对比。 这就导致了PMOS的泄放能力远低于NMOS,若想二者达到相同的泄放能力,就需要PMOS的面积更大,但是又会引入开启不均匀的问题。也因为该特质,PMOS中寄生P-N-P三极管也比NMOS中寄生N-P-N更难开启,PMOS的Trigger Voltage要高于NMOS。 但是PMOS也有其独到优势,正是因为载流子迁移率低,PMOS的漏电流要小于NMOS,尤其是ESD器件普遍尺寸较大,在某些应用场景下不得不考虑ESD防护电路所带来的漏电问题。PMOS的Snap-Back较弱,虽然会造成ESD鲁棒性较差,但是会提升Latch-up的鲁棒性,其IV曲线不会进入Latch-up区内。而且GDPMOS的寄生电容要优于GGNMOS,对信号完整性更为友好。 三.PMOS在ESD防护中的应用。 PMOS最简单的ESD应用便是GDPMOS和GCPMOS了,但是随着应用场合的多元化,ESD设计要求也愈发复杂,传统结构已经难以满足现阶段的设计需求,很多改进型器件/电路也应运而生。图五为一种新型Power Clamp结构,其采用PMOS作为BigFET进行ESD泄放。  图五.新型Power Clamp结构。 该结构与传统RC相比,面积更小、更难误触发、开启电压可控。正常上电时,结点A为VDD,结点B为GND,该电路整体关断。当ESD发生时,Rn与Cgs+Cgd+Cgb发生耦合,拉低A点电压,Mp略微导通,从而B点电压会抬升一点。略微开启Mn,Mn又会拉低A电压,Mn与Mp构成正反馈,直到A点电位为低,B点电位为高,Mn与Mp完全开启,此时Mclamp的沟道也会完全开启,实现ESD泄放。如图六所示,因为舍弃了电容,面积上自然小很多。  图六.传统RC与新型结构面积对比。 因为靠的是寄生电容产生感应,所以RC时间常数很小,快速上电时,感应电压相较VDD微不足道,无法对系统造成扰动。如图七所示,新结构面对电源脉冲还是快速上电时,都能与电源保持一致,而传统RC结构因为误触发会造成VDD产生迟滞。  图七.快速脉冲与误触发对比。 如图八所示,通过调整二极管个数可以控制开启电压。二极管数目越多,就需要Mn与Mp的开启程度越大,Mclamp的开启时间与电压都要大一些。  图八.新结构TLP曲线。 除此之外,PMOS还经常作为辅助触发单元。如图九所示,PMOS内嵌套一个N+构建寄生SCR,利用PMOS协助触发SCR,既能降低Trigger Voltage又能提高ESD鲁棒性和开启时间,还能降低寄生电容和漏电流。  图九.嵌套N+的新型PMOS结构。 如图十所示,也可通过外部PMOS协助触发SCR。PMOS先开启,然后再开启SCR。  图十.独立PMOS协助触发SCR。 还有一种是之前提到过的Soft Tie结构,通过PMOS协助触发NMOS的新型结构。  图十一.Soft Tie 结构。 这些结构都是看中了PMOS低寄生,弱Snap-Back的特性,利用PMOS协助触发其它高鲁棒性ESD器件。通过将PMOS与其他器件结合到一起,取长补短,实现优异的ESD性能。 NMOS,LDMOS,Diode,Bipolar,SCR,PMOS等常见ESD器件笔者已经差不多介绍完毕了,这些器件是ESD设计中的基本单元,而如何使用,怎么使用等技术细节都是要根据实际情况进行设计。正所谓文无定法,只要能满足要求的ESD设计便是好的ESD设计。 |