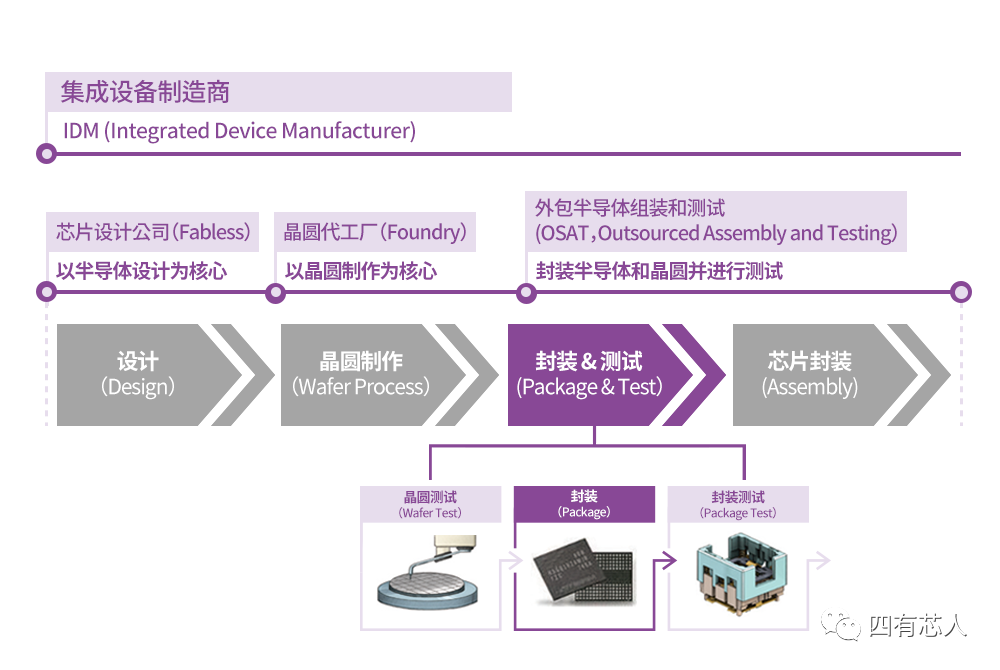

半导体制作工艺可分为前端和后端:前端主要是晶圆制作和光刻(在晶圆上绘制电路);后端主要是芯片的封装。随着前端工艺微细化技术逐渐达到极限,后端工艺的重要性愈发突显。作为可以创造新附加价值的核心突破点,其技术正备受瞩目。此系列文章将以《提高半导体附加价值的封装与测试》一书内容为基础,详细讲解后端工艺。 #1 半导体后端工艺制作半导体产品的第一步,就是根据所需功能设计芯片(Chip)。然后,再将芯片制作成晶圆(Wafer)。由于晶圆由芯片反复排列而成,当我们细看已完成的晶圆时,可以看到上面有很多小格子状的结构,其中一个小格子就相当于一个芯片。芯片体积越大,每个晶圆可产出的芯片数量就越少,反之亦然。半导体设计不属于制程工序,半导体产品的制程工序大体可分为晶圆制作、封装和测试。其中,晶圆制作属于前端(Front End)工艺;封装和测试属于后端(Back End)工艺。晶圆的制作工艺中也会细分前端和后端,通常是CMOS制程工序属于前端,而其后的金属布线工序属于后端。  ▲ 图1:半导体制作流程与半导体行业划分(ⓒHANOL出版社/photograph.SENSATA) 图1展示了半导体制程工艺及其行业的划分。只从事半导体设计的产业运作模式被称作芯片设计公司(Fabless),该模式的典型代表有高通(Qualcomm)、苹果(Apple)等。负责晶圆制作的制造商被称为晶圆代工厂(Foundry),他们根据Fabless公司的设计制作晶圆,其中最典型的代表要台积电(TSMC)了,DB HiTek、Magnachip等韩企也采用这一模式。经Fabless设计和Foundry制造的晶圆还需经过封装和测试,专门负责这两道工艺的企业就是外包半导体组装和测试(OSAT,Outsourced Assembly and Testing),其典型代表有ASE、JCET、星科金朋(Stats Chippac)、安靠(Amkor)等。此外,还有像SK海力士这样集半导体设计、晶圆制造、封装和测试等多个产业链环节于一身的集成设备制造商(IDM,Integrated Device Manufacturer)。 如图1所示,封装和测试工艺的第一步就是晶圆测试。封装后,再对封装进行测试。 半导体测试的主要目的之一就是防止不良产品出厂。一旦向客户提供不良产品,客户对我们的信任就会大打折扣,进而导致公司销售业绩的下降,还会引发赔偿等资金上的损失。因此,我们必须在产品出厂前对其进行细致的全面检测。半导体测试须根据产品的各种特性,对其各参数进行测试,以确保产品的品质和可靠度。当然,这需要时间、设备和劳动力上的投入,产品的制造成本也会随之增加。因此,众多测试工程师正致力于减少测试时间和测试参数。

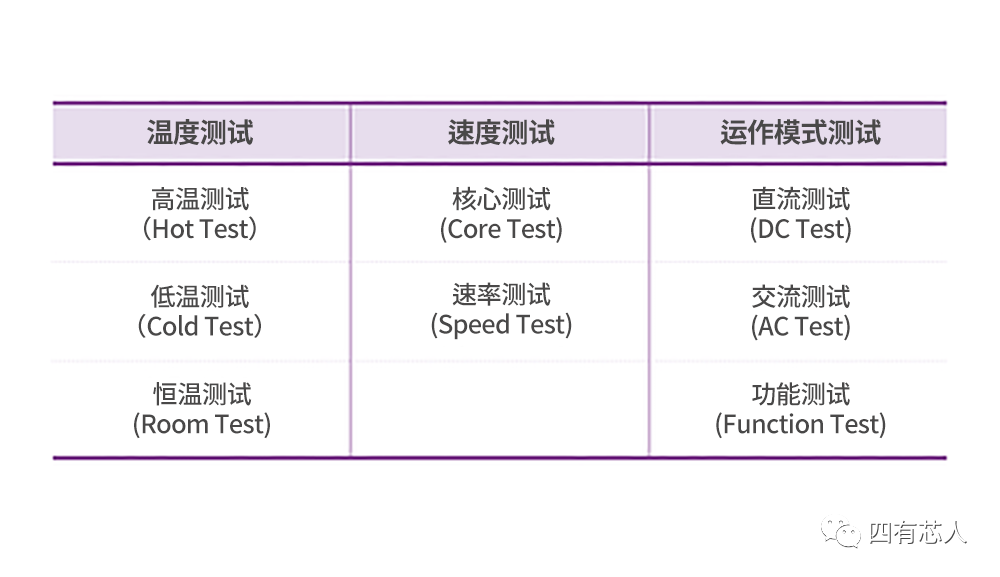

#2 测试的种类

▲ 表1: 测试分类(ⓒ HANOL出版社) |