闩锁(Latch-up)

闩锁就是指CMOS器件所固有的寄生可控硅(SCR)被触发导通,在电源与地之间形成低阻抗大电流通路的现象。这种寄生SCR结构存在于CMOS器件内的各个部分,包括输入端、输出端、内部反相器等。当在电源端、输入端或输出端有较强的浪涌冲击时,就可能触发这些可控硅,产生闩锁。当闩锁电流达到一定强度持续一段时间,就可能造成器件的永久性损坏。

闩锁产生机理

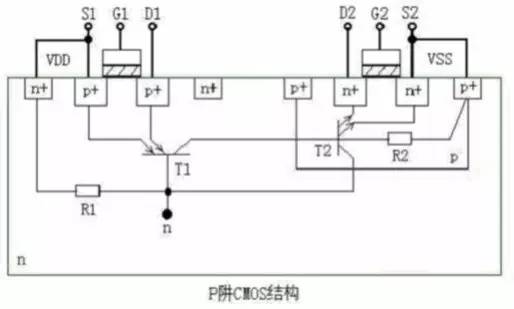

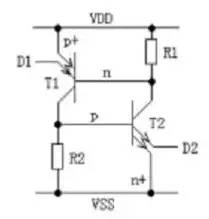

图1表示一个简单的P阱CMOS结构,很显然,这种结构存在寄生的NPN和PNP晶体管,寄生NPN晶体管是纵向结构,其发射区是n+扩散区,基区是p阱,集电区是n型衬底。寄生PNP晶体管是横向结构,其发射区是p+扩散区,基区是n型衬底,集电区是p阱。图2是寄生双极晶体管构成的等效电路,n型衬底和p阱本身存在体电阻,分别以R1和R2表示。R1跨接在VDD与PNP管的基极之间,R2则跨接在NPN管的基极与VSS之间。在正常工作状态下,这种寄生的PNPN四层结构处于截止状态,不会产生异常电流。但是在某种外部条件的触发下,例如图2中的D1端的正尖峰电压高于VDD或者D2端的负尖峰电压低于VSS,这种PNPN四层正反馈结构就可能产生类似于可控硅的触发导通。此时,即使外部触发条件消失,导通电流仍然会维持,这种现象就是所谓有闩锁效应,也称为寄生可控硅效应。

由图可知,减小R1与R2可以提高CMOS电路的抗闩锁能力。因此在很多CMOS工艺中在P阱四周加上接VSS的p+扩散保护环,在PMOS管的四周加上接VDD的n+扩散保护环,如图1所示,并且在保护环上尽可能多开些金属引线孔,用金属互连线将保护环短接,以减小R1与R2,这样即可有效地防止闩锁效应。

图1:P阱CMOS结构

图2:P阱CMOS PNPN四层结构等效电路

闩锁(Latch-up)的触发条件

触发条件为CMOS电路的输入输出脚或电源地脚上出现一定的电流VLU或电压VLU。很多CMOS器件的Datasheet里都标明允许施加在输入端的电压在VDD+0.3V与VSS-0.3V之间,超过这个值就可能会引发闩锁。另外CMOS器件对于输出端的拉电流和灌电流也有相应的限值规定,超过规定的电流,就不能保证器件应用的可靠,或可能引发闩锁。

另外,当器件的电源电压超过其最大允许电压时,可能引发n衬底与P阱之间的雪崩击穿而闩锁。少数情况下,电源上的尖峰电压,也可能引发闩锁。

如何防止闩锁

从闩锁产生机理可知,防止闩锁就是要防止闩锁的触发条件产生。

下面介绍防止闩锁的一些具体措施:

1.带电插拔时,要求连接顺序为:GND、低电压电源、高电压电源、I/O。其中电压以绝对值计。相同幅值的正负电源同时上电,可使两者的影响相互抵消。

2.做好电源去耦,避免上电时或工作中,电源电压上冲或下冲导致的闩锁。

3.电源串电阻,限流,消除闩锁导致器件的损坏。

4.继电器等感性负载,加反接二极管吸收浪涌电流。

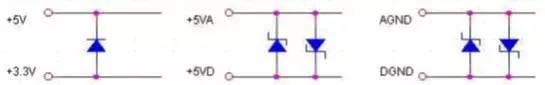

5.高低电压电源之间接二极管,避免在上下电时,低电压电源端电压超过高电压电源端过多,起箝位作用。

6.同电压的不同电源之间加两个相互反接的肖特基二极管。

7. AGND与DGND之间加两个相互反接的肖特基二极管。

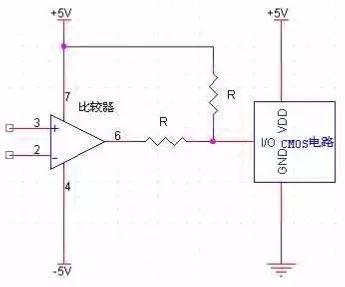

图3:电源与地的防止闩锁电路

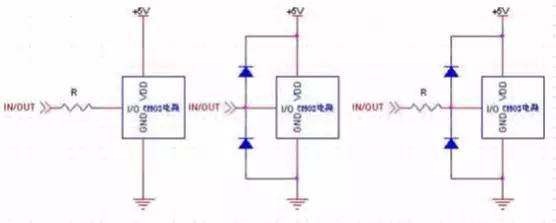

图4:CMOS I/O口的保护电路

8.驱动长线负载时,做好匹配,以减小过冲、下冲,允许的条件下,可在CMOS器件端口处加两个二极管,一个接地,一个接电源。

9.系统具有用户可操作的I/O,在I/O串接一个电阻限流,并可在端口处加两个二极管,一个接地,一个接电源。

10. 数字电路与模拟电路相接时,如下图,通过电阻分压比用二极管箝位效果要好。

图5:模拟电路与数字电路连接时的保护电路

器件的闩锁测试

器件的闩锁测试,就是模拟浪涌信号加在器件的电源、输入、输出端,看是否出现闩锁,即是否出现工作电流受浪涌冲击后迅速增大并超过一定的范围。测试包括:电源端的过电压冲击测试和输入输出端的过电流冲击测试。

热插拔介绍:

热插拔的英文翻译为Hotsocketing,或Hot swapping,或Hotplug-in。、指机框在上电状态下,将电路板插入机框或从机框中拔下电路板。

在电信设备的测试、维护过程中,由于系统不能中断,电路板的带电插拔情况普遍存在。为了保证器件不受损害和信号完整性,电路板必须有针对性的设计,特别是高速数字系统。带电插拔系统需要特别考虑的是确保系统运行中信号的完整性。此外,快速改变的电压和破坏性电流对设备的不利影响也是需要考虑的。保护性电路、元件和特殊的软件控制可以消除热插拔相关的不利影响。

按照电路带电插拔时对器件和信号的影响程度,把带电插拔的防护设计分为四个等级。介绍如下。但该四个等级是根据普通逻辑器件(如驱动器等)的电路结构来定义的,FPGA、CPLD等大逻辑器件的端口结构与普通逻辑器件有较大的区别,结构更加复杂,但仍可以等效为普通逻辑器件的热插拔等级。

1)0级防护

具有0级防护设计的电路板应在先关断主电源的情况下才能安全的带电插拔。它没有对瞬变电流或突变电压的抑制保护,插拔过程中插入电路板接口也不能进入高阻状态。如果插入电路板在系统没有断电情况下就进行带电插拔,板上的接口器件或其他元件很可能受到损坏。只能达到0级防护设计的电路板不能带电插拔。

2)1级防护(Partial Power Down)

具有1级防护设计的电路板在断电时能限制带电总线和插入电路板接口之间的电流,从而防止插入电路板受到损坏。这种瞬态电流限制就能保证在不打断主电源情况下带电插拔电路板,但是在带电插拔期间,主系统必须暂停信号传输。这种防护设计需要使用IOFF电路。

3)2级防护(Hot Insertion)

具有2级防护设计的电路板具有带电插拔性能,它能防止插入电路板插拔时的驱动冲突。2级防护设计除了具有1级防护设计的能力外,信号端还能在电源电压上升到指定值之前保持高阻状态,在电源电压超过这个指定值后会按照设置状态输出。电路板断电时,在电源电压下降到预定电压值之前输出保持为驱动逻辑电平,然后变成高阻状态。按照2级防护设计的要求,电路板带电插拔期间总线上的数据传输可能会被打断。2级防护设计既需要1级防护设计中的IOFF电路,也需要上电3态电路(PU3S)。

4)3级防护(Live Insertion)

具有3级防护设计的电路板在带电插拔时对系统电源和信号没有其他的限制、约束和要求。带电插拔和数据交换可同步进行,即在任何情况下进行插、拔操作都不会破坏数据,当然更不会损坏器件。为了达到这些要求,3级防护设计同时需要IOFF、PU3S和预充电I/O。

ALTERA对热插拔的定义

ALTERA对热插拔的定义如下。

热插拔的英文翻译为Hotsocketing,或Hot swapping,或Hotplug-in。热插拔特性是指在一个正在运行的系统中插入或者移出电路板时不会对系统或电路板造成破坏或损伤的能力。

具备热插拔特性的可编程逻辑器件必须有如下的特性:

驱动未上电的器件时不会对该器件造成损伤;

在器件未上电或上电的过程中,该器件没有向外驱动;

外部向器件I/O管脚的输入信号不会通过器件内部电路向器件的Vccio, Vccpd或者Vccint充电。

依据以上的定义,ALTERA具有热插拔特性的器件的热插拔等级相当于2级插拔等级以上。

ALTERA认为互联网、无线通讯和存储业的增长推动实时数据通讯呈指数倍的增长。在实时数据通讯业务中,运营商不能完全关闭系统进行维修、维护和升级,因为系统提供的业务或服务不能中断。

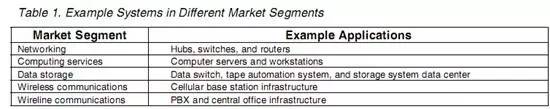

热插拔特性对于需要高可用性的系统和有冗余备份的系统至关重要,表1中列出了不同市场中的一些例子。

表1 不同市场对热插拔的需求

热插拔和上电顺序保护因为半导体制造技术的进步变得更加重要。随着半导体节点的不断缩小,要求功率IC提供更低的电压。同时,不同的I/O标准需要不同的电压。今天的PCB往往需要集成多种电压等级的器件,如5.0, 3.3, 2.5, 1.8和1.2V,要保证正确的上电顺序更加困难。

没有热插拔需求的多电压系统仍能从热插拔和上电顺序保护特性中受益。在一个多电压系统中,不同的电压往往由电压调节器提供。电压调节器的使用使得系统的上电顺序变得不容易预测。需要特定上电顺序的器件可能工作不正常,从而造成系统故障。