|

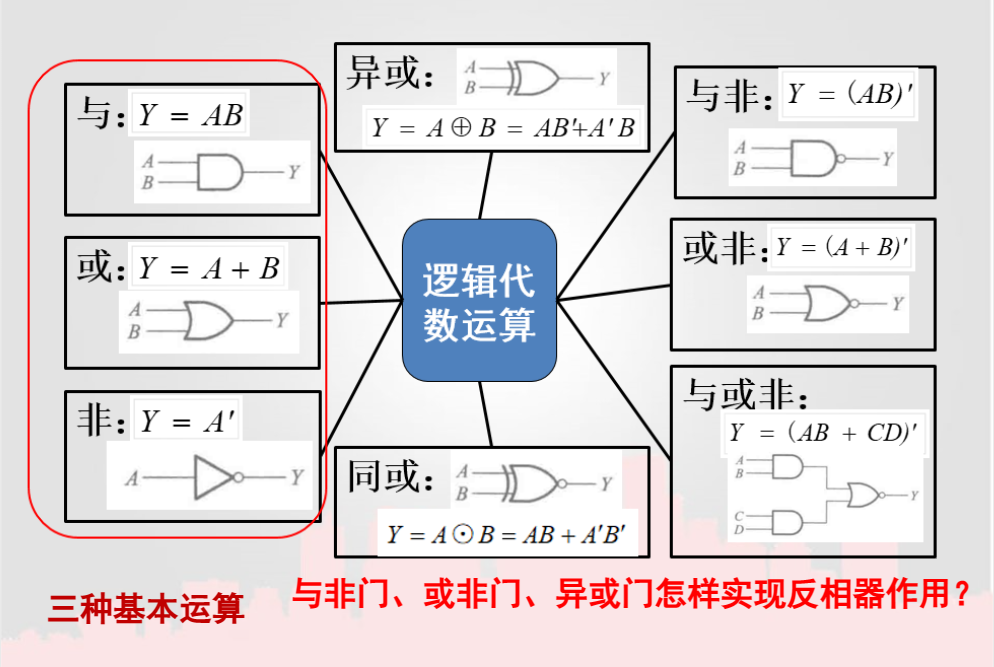

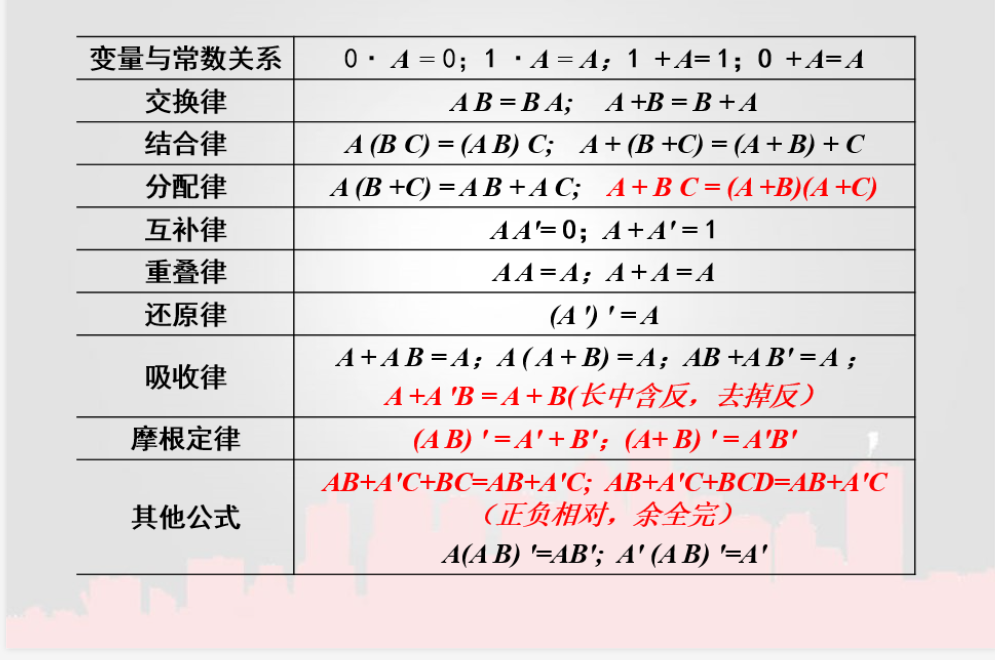

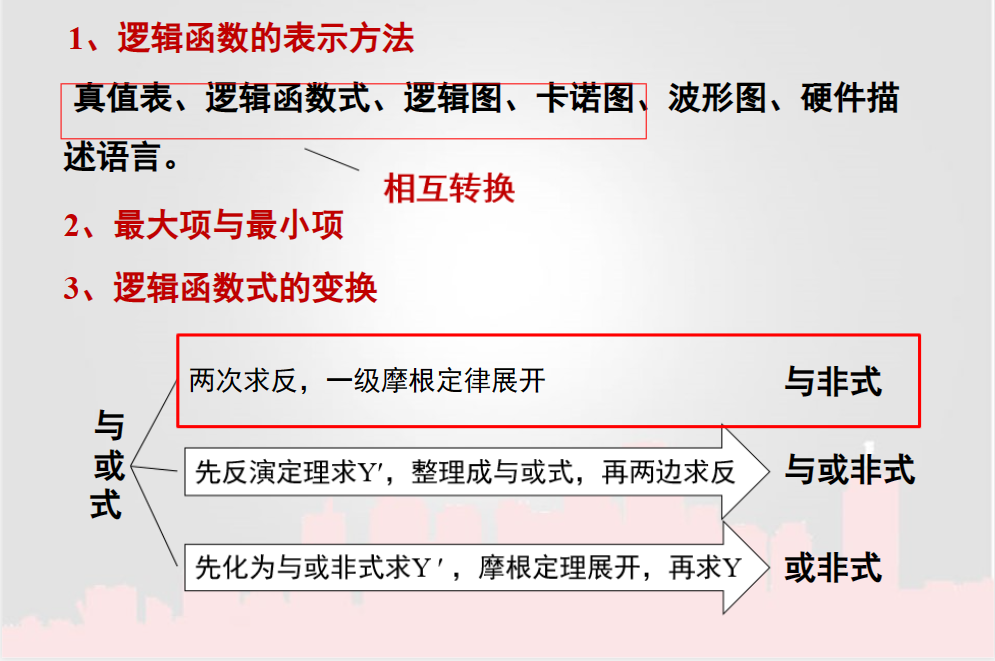

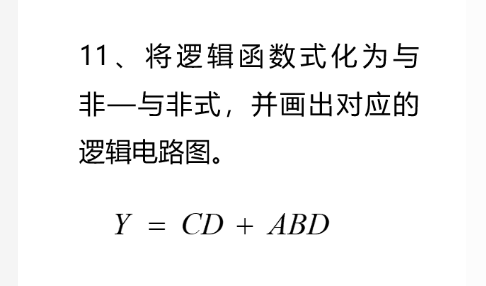

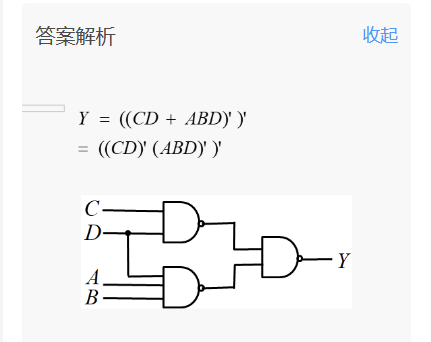

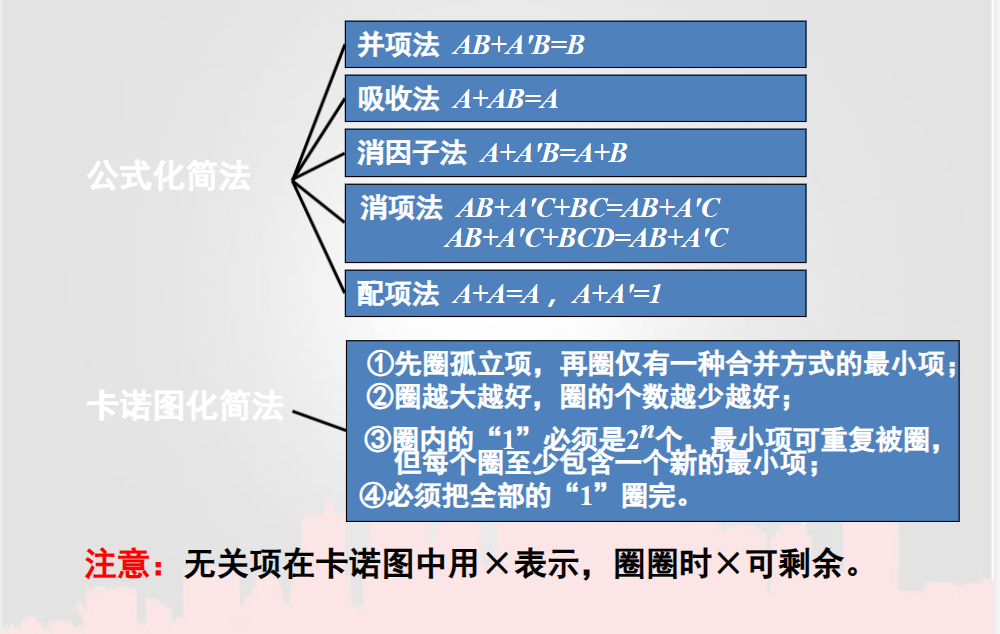

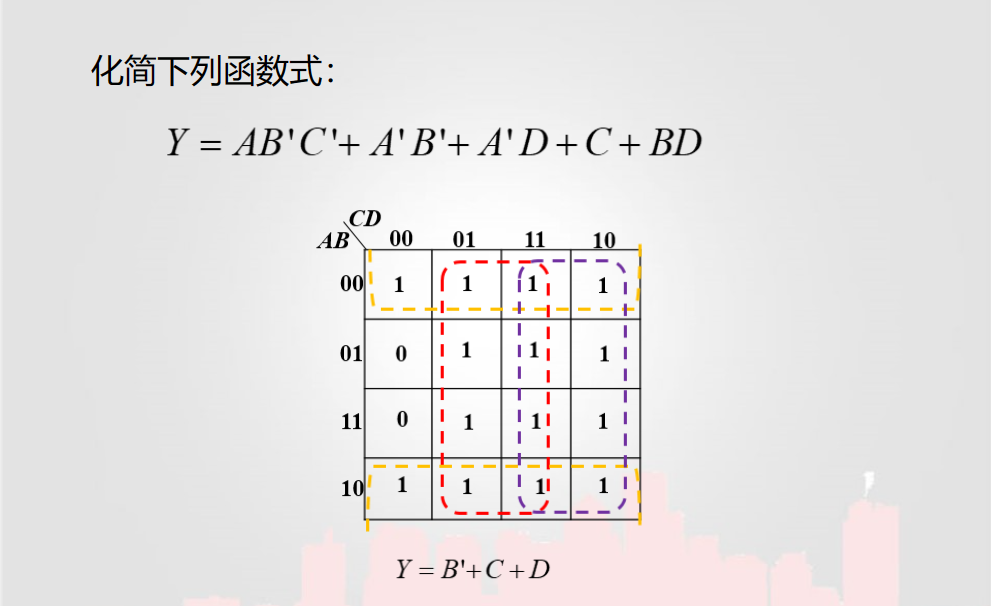

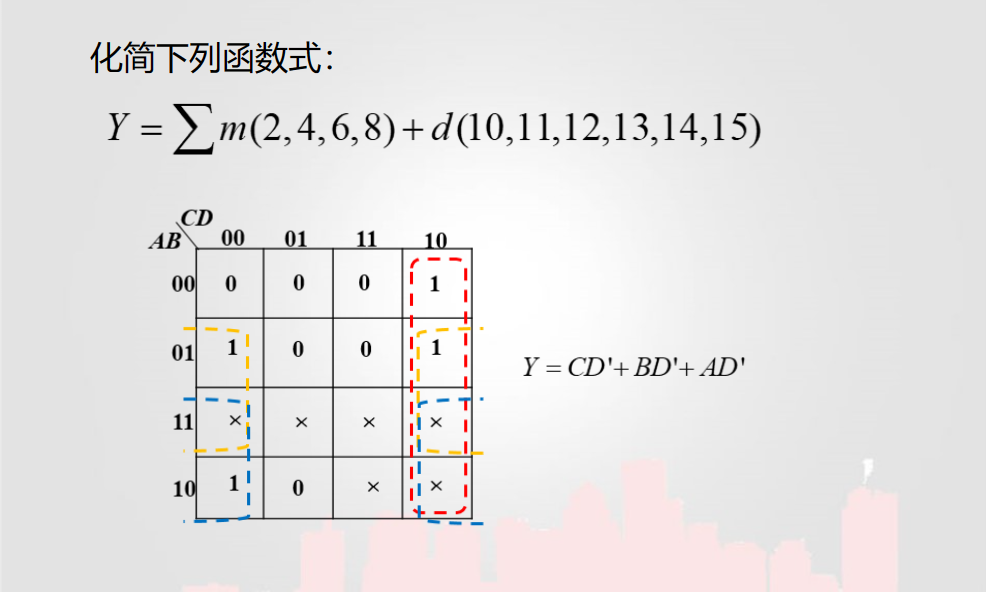

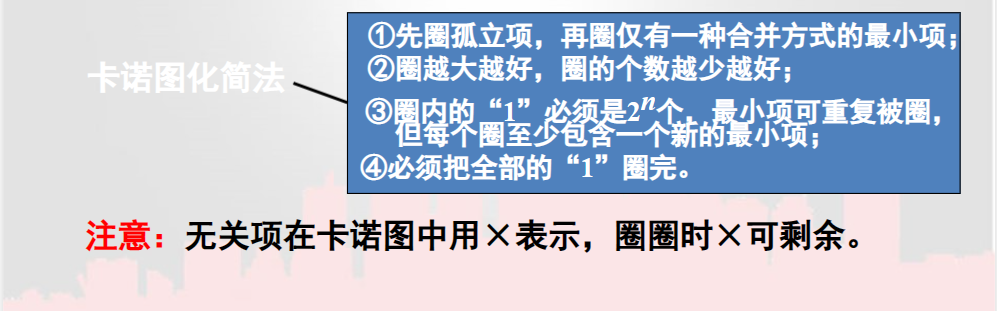

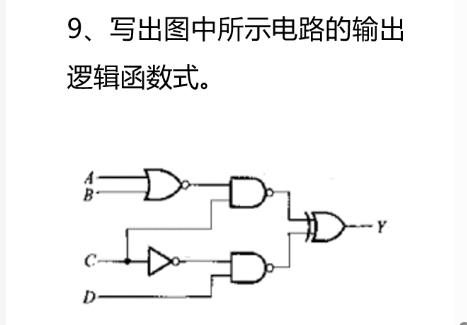

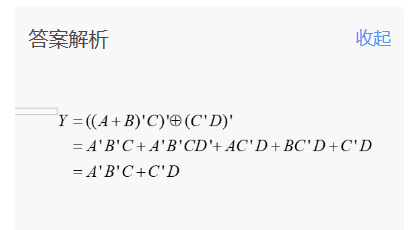

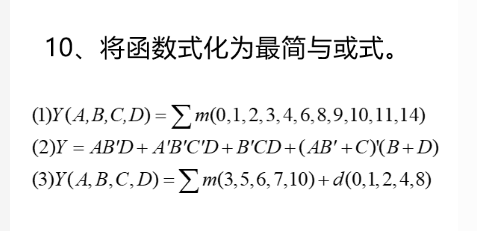

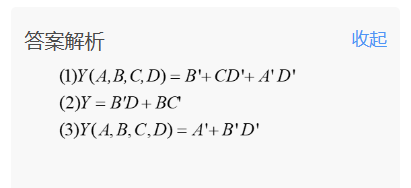

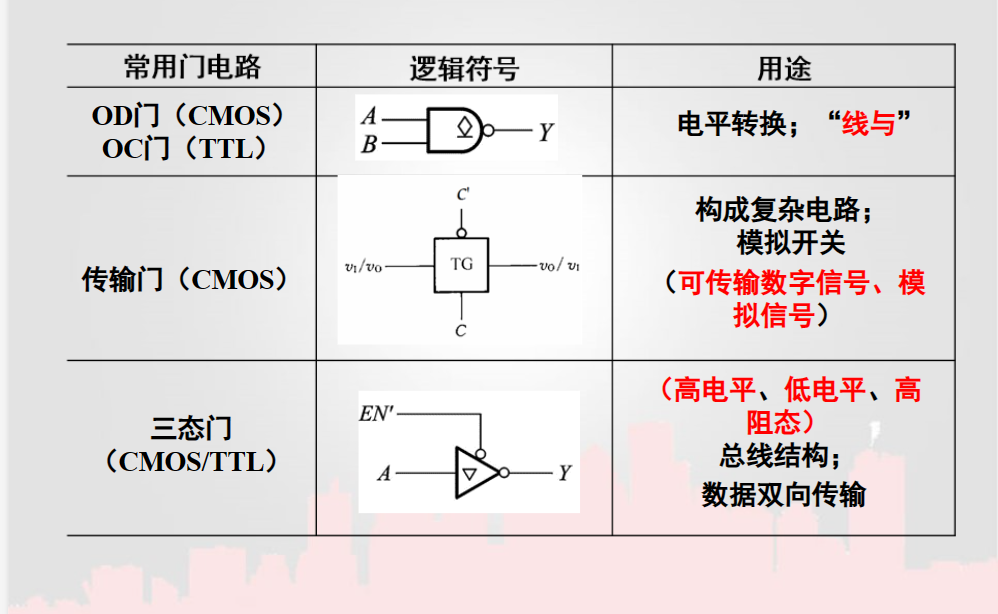

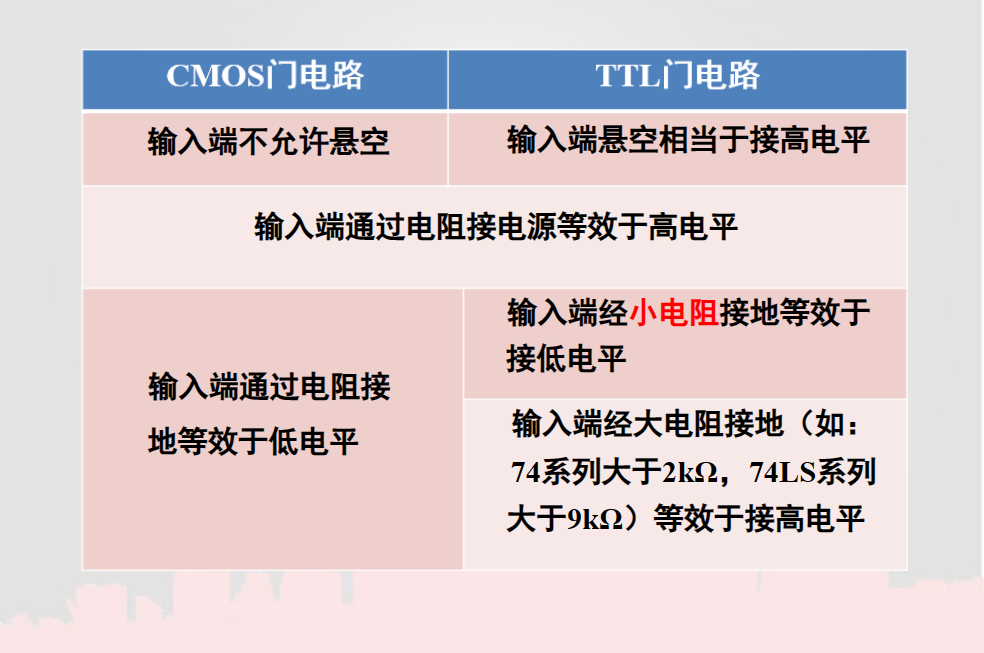

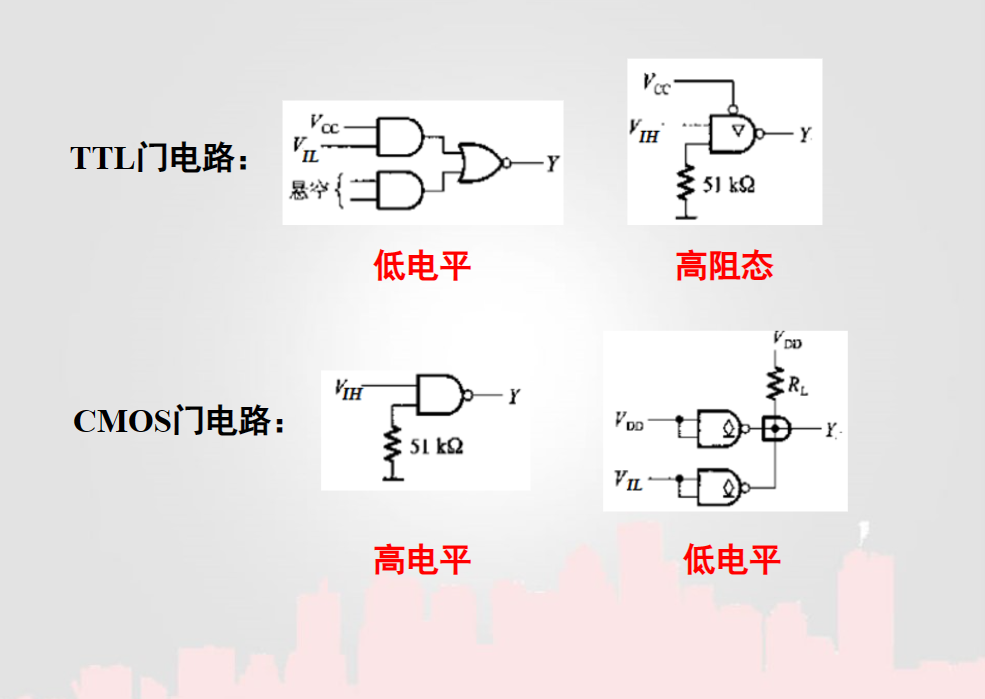

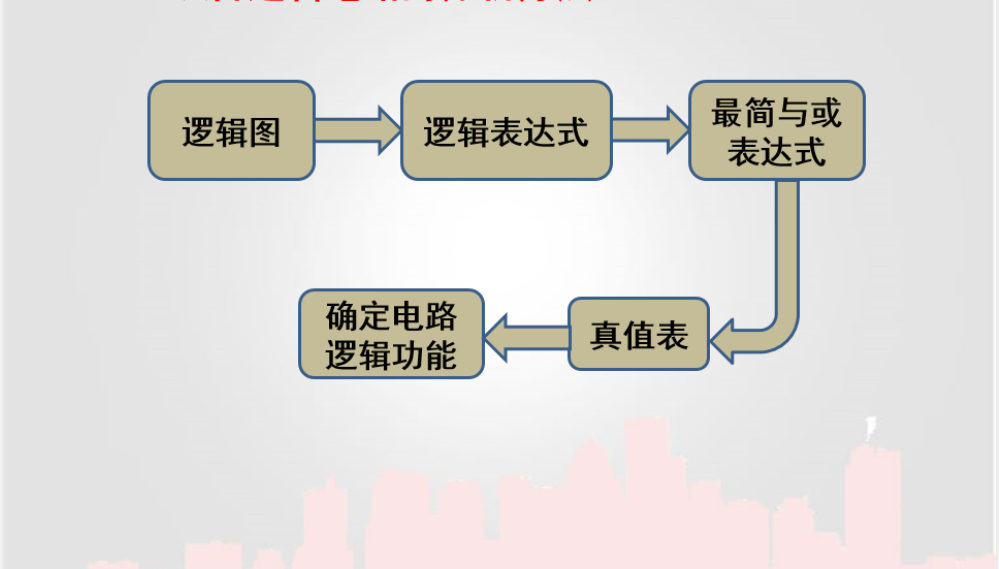

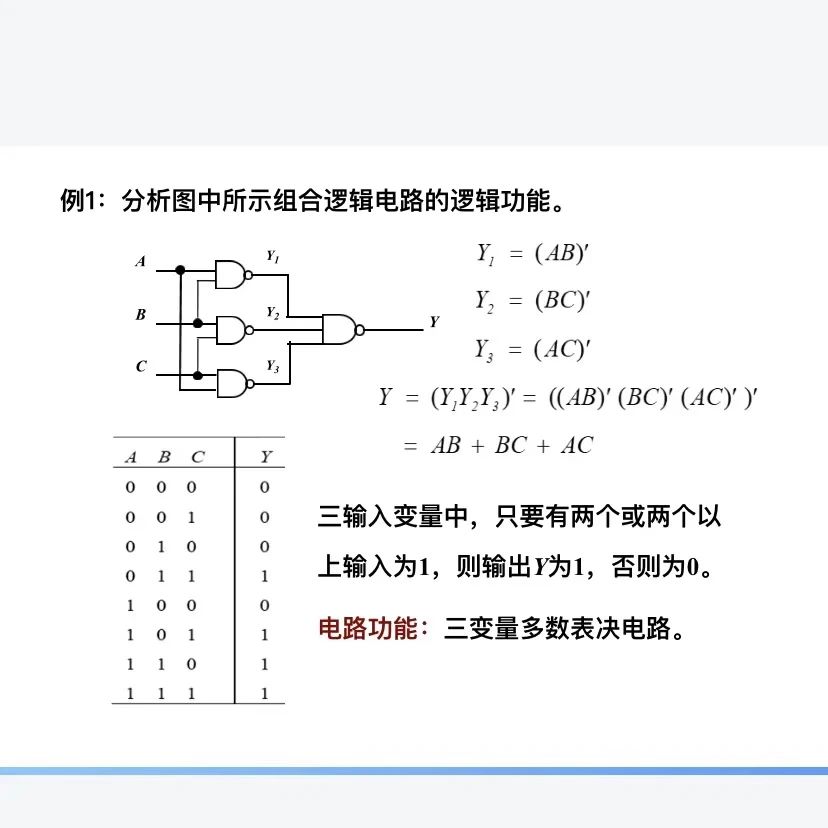

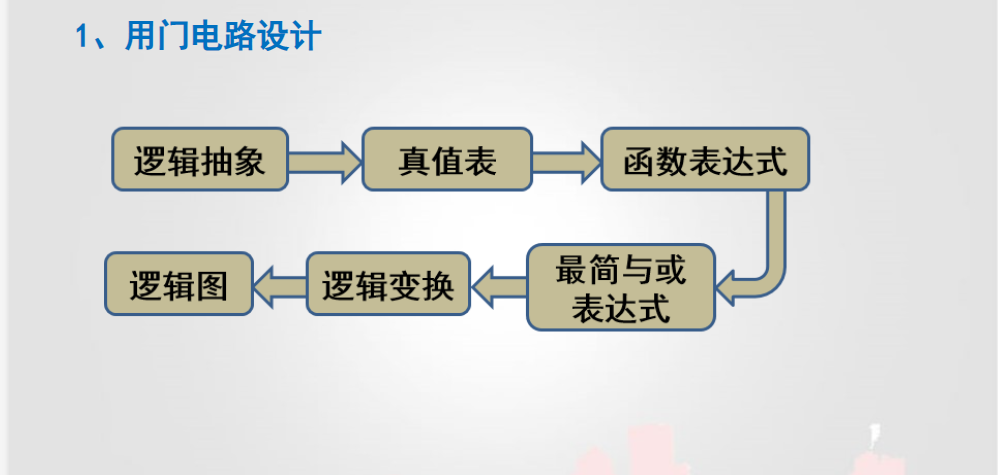

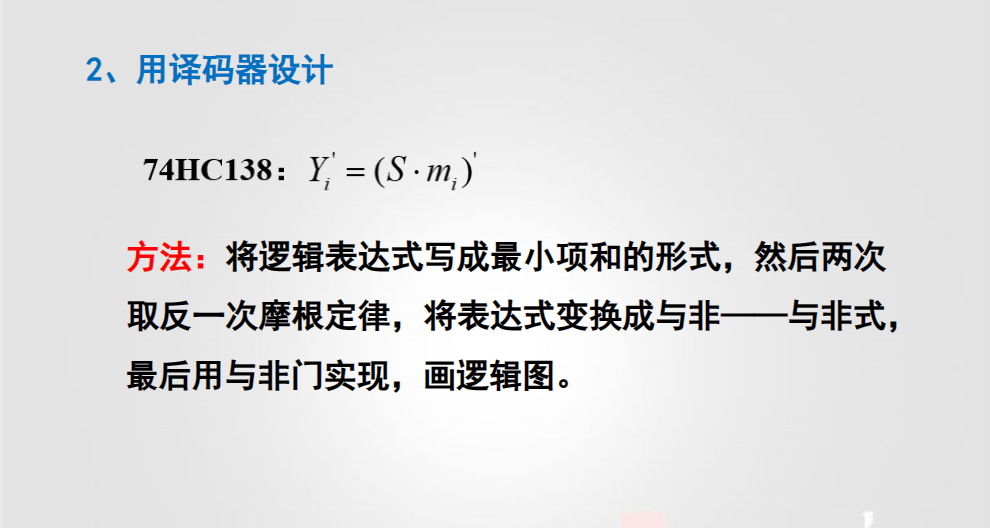

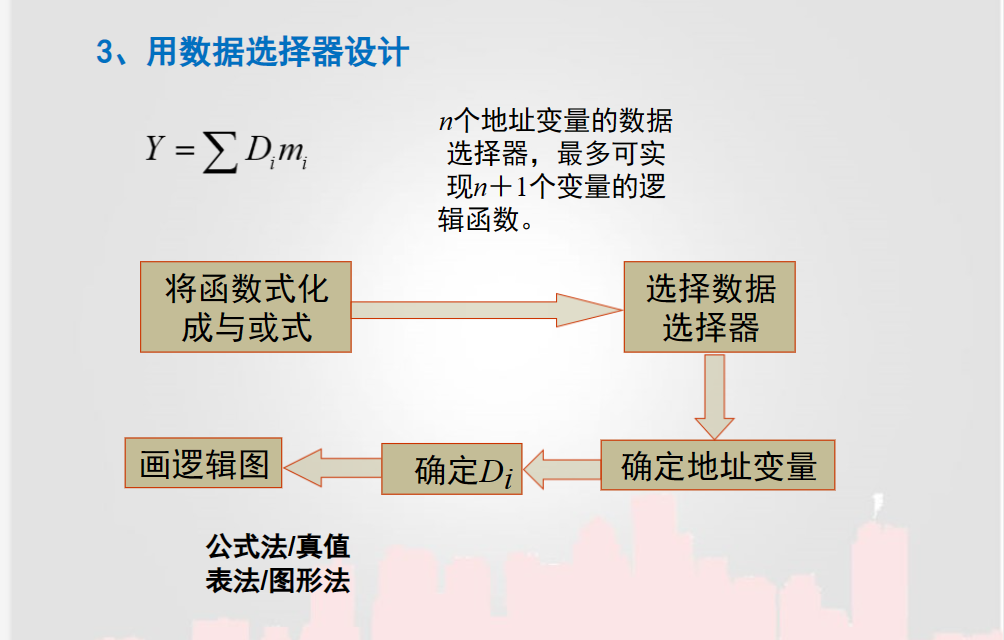

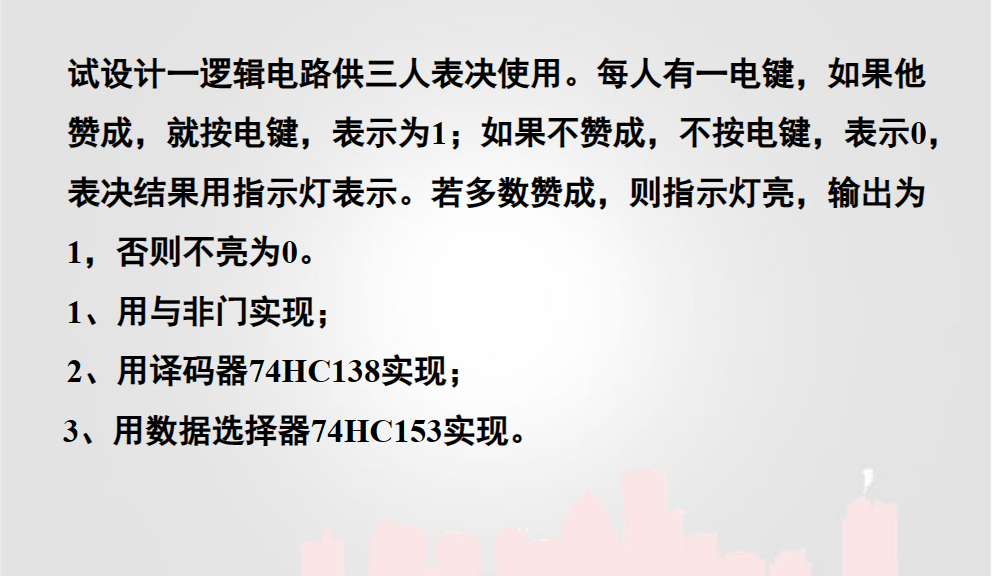

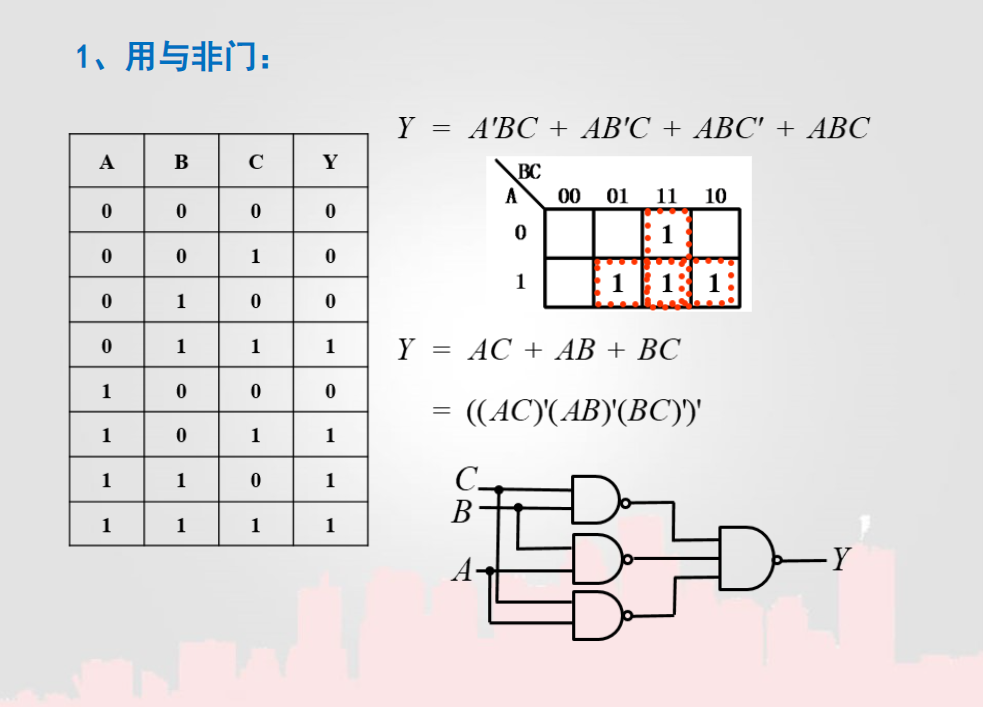

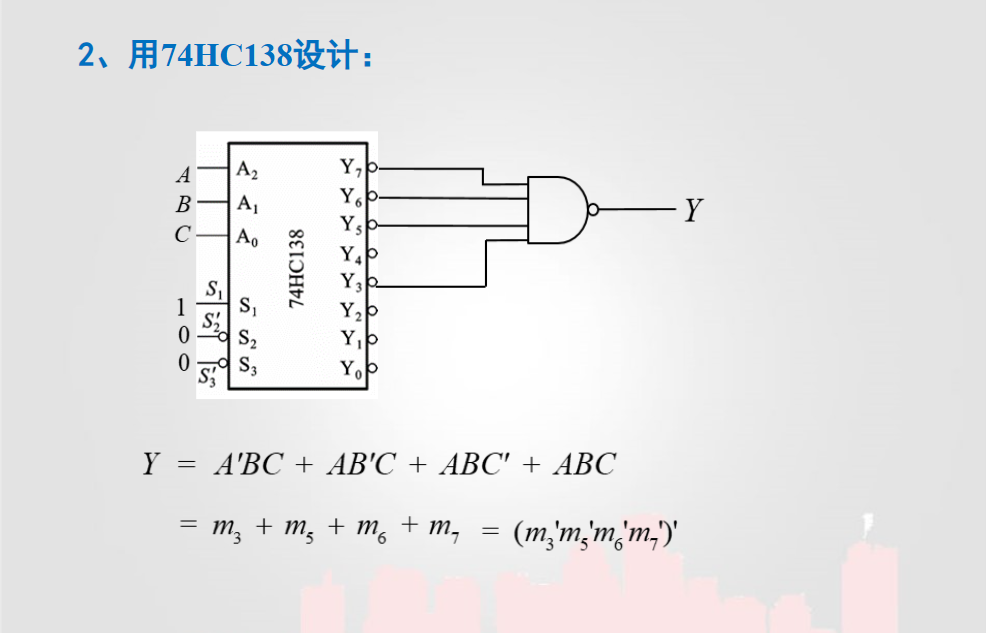

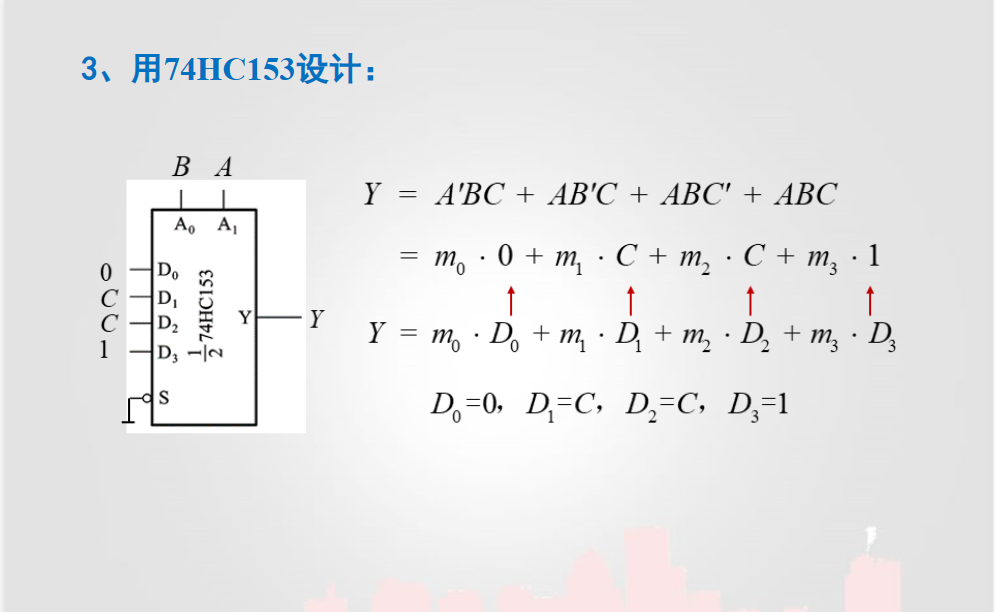

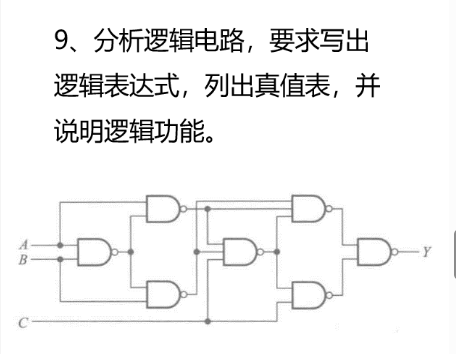

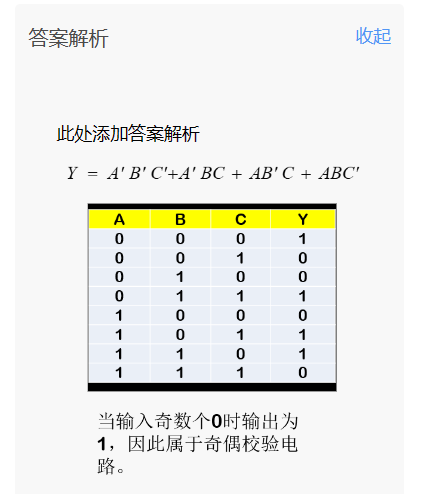

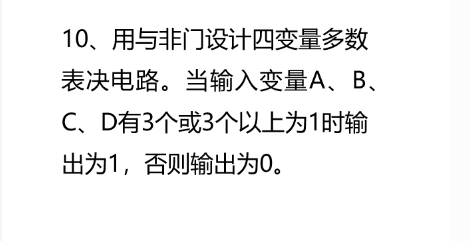

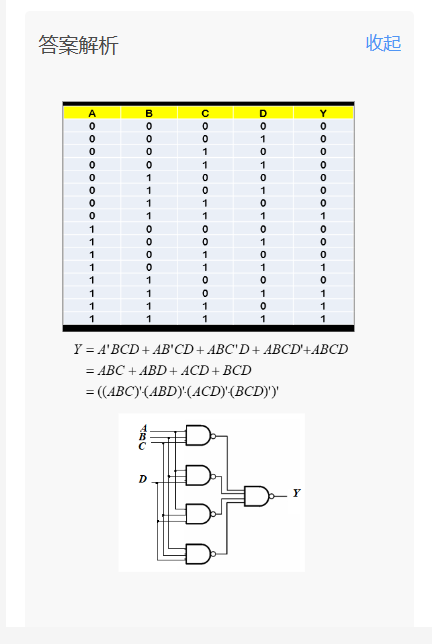

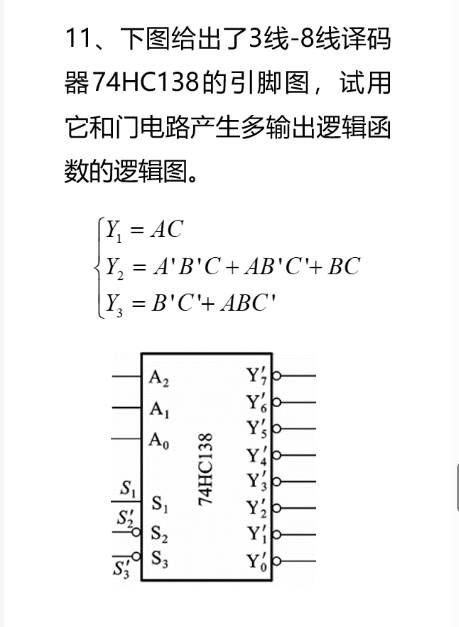

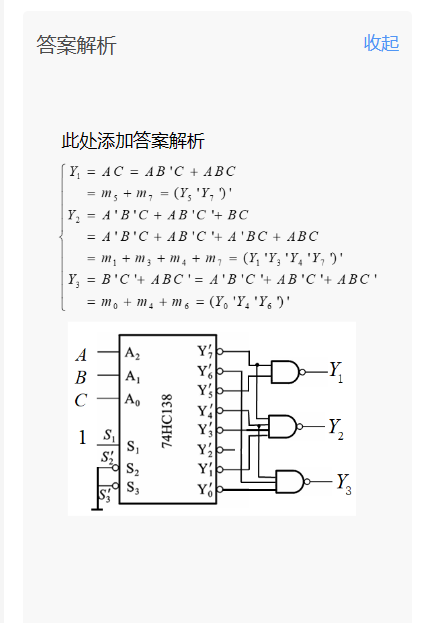

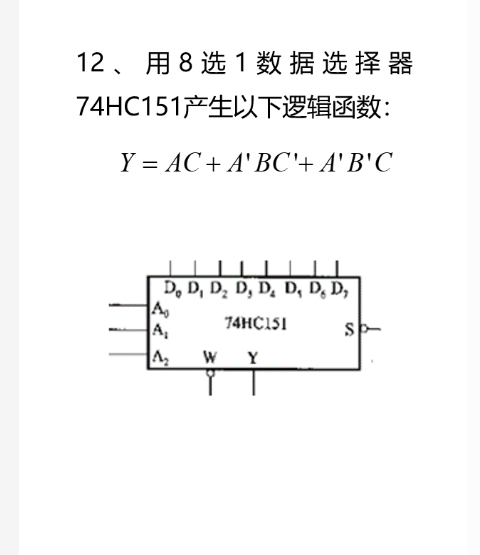

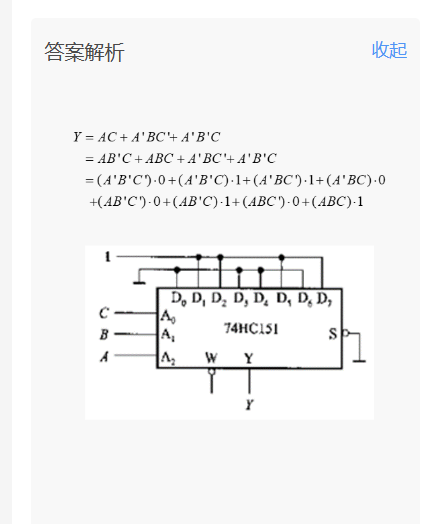

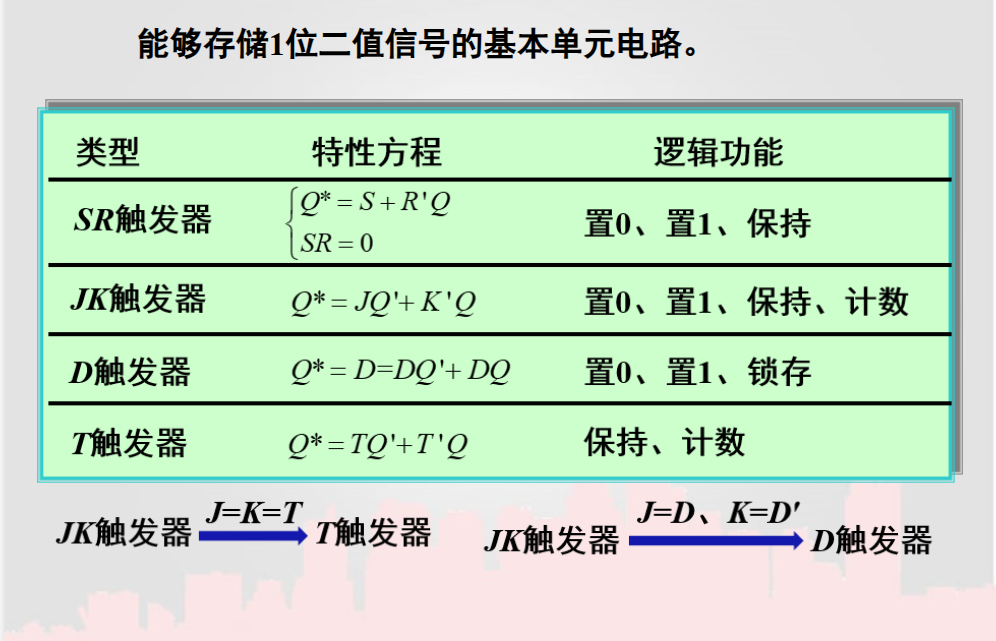

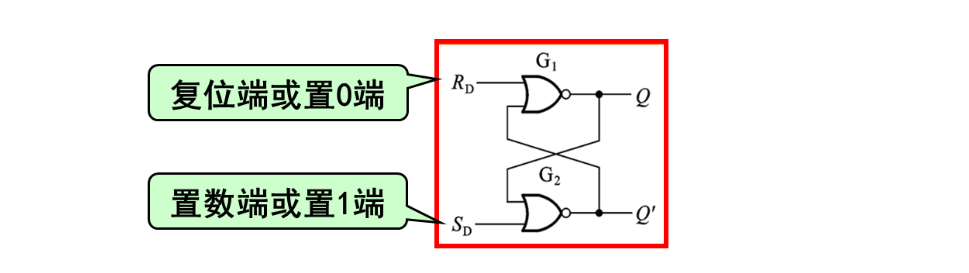

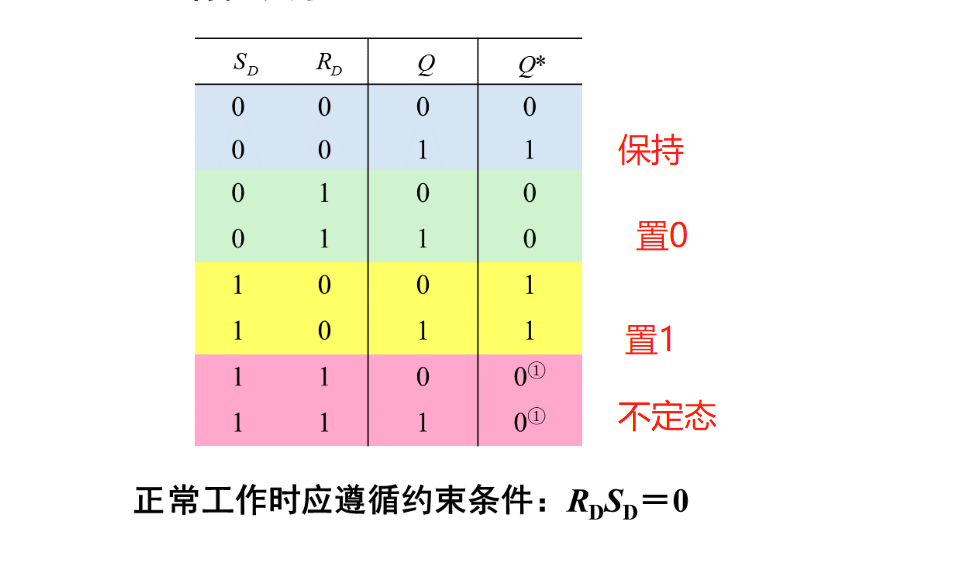

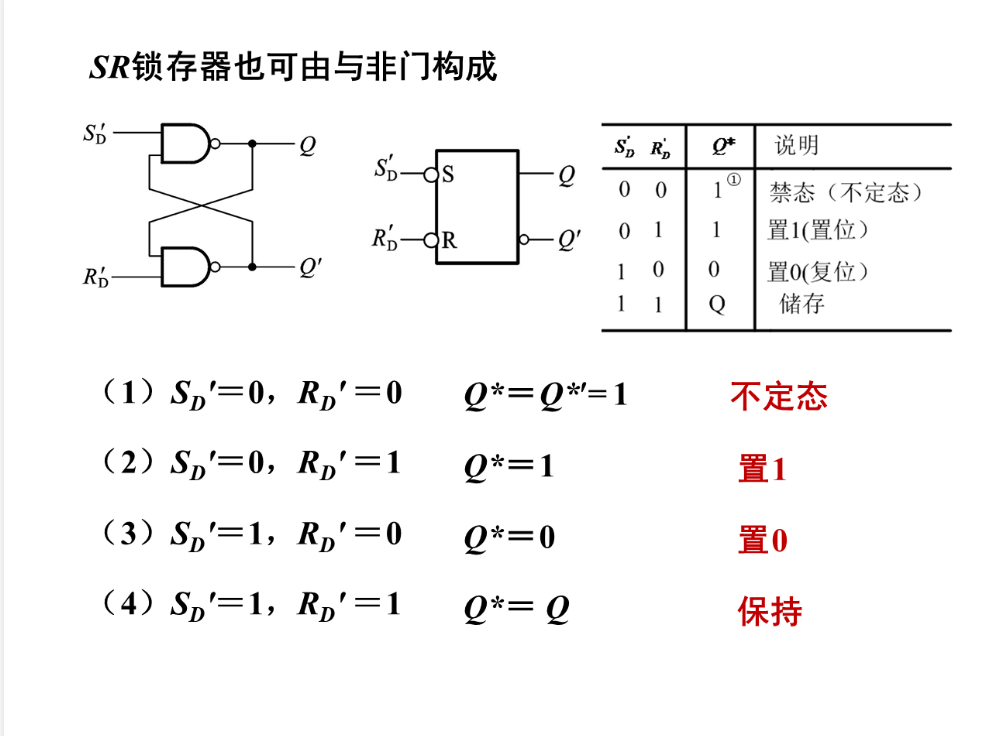

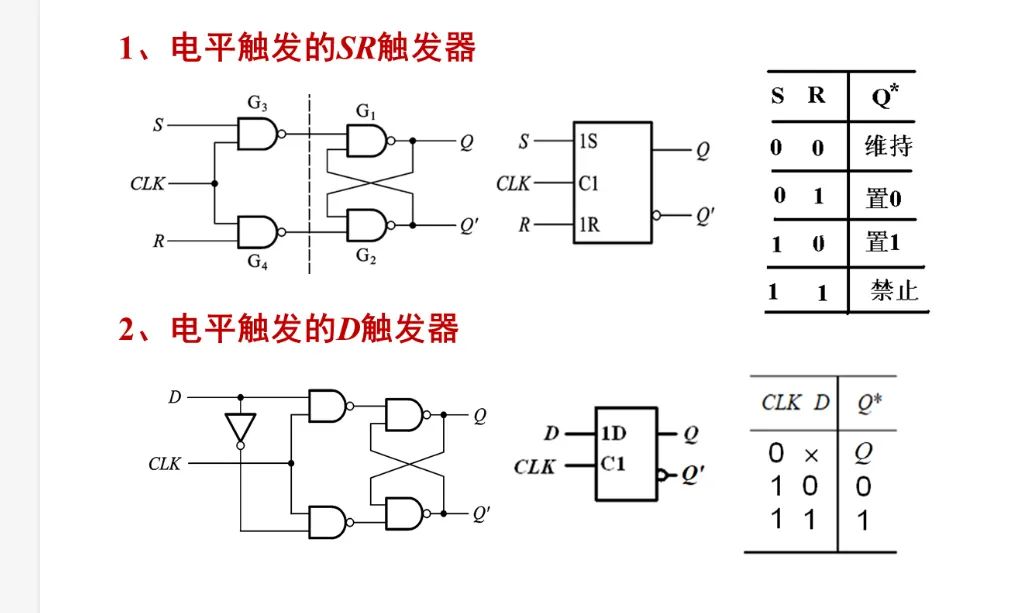

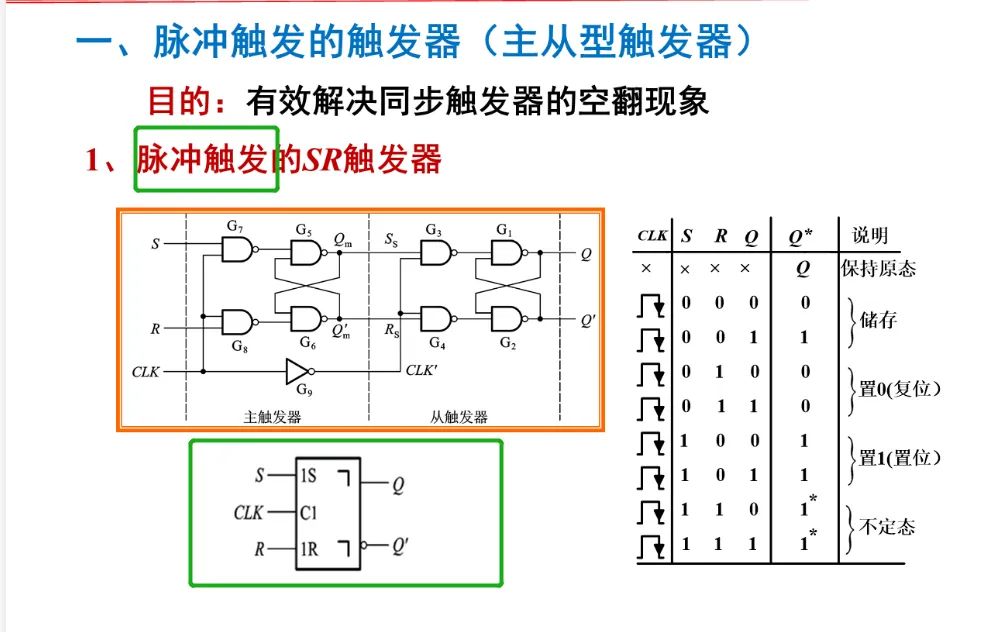

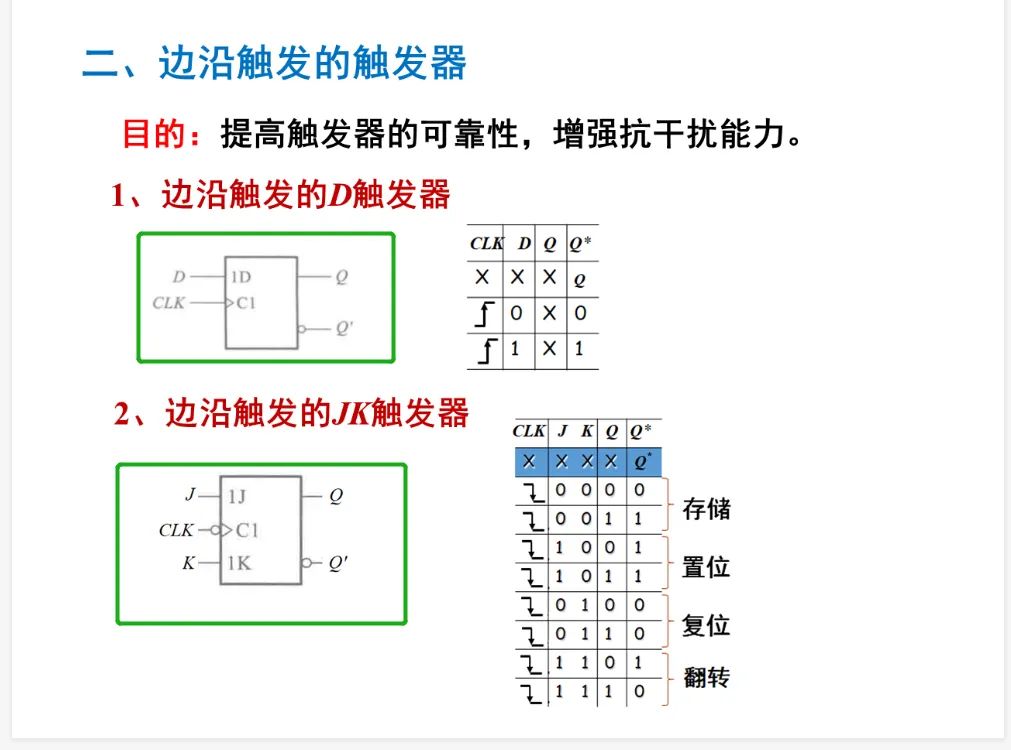

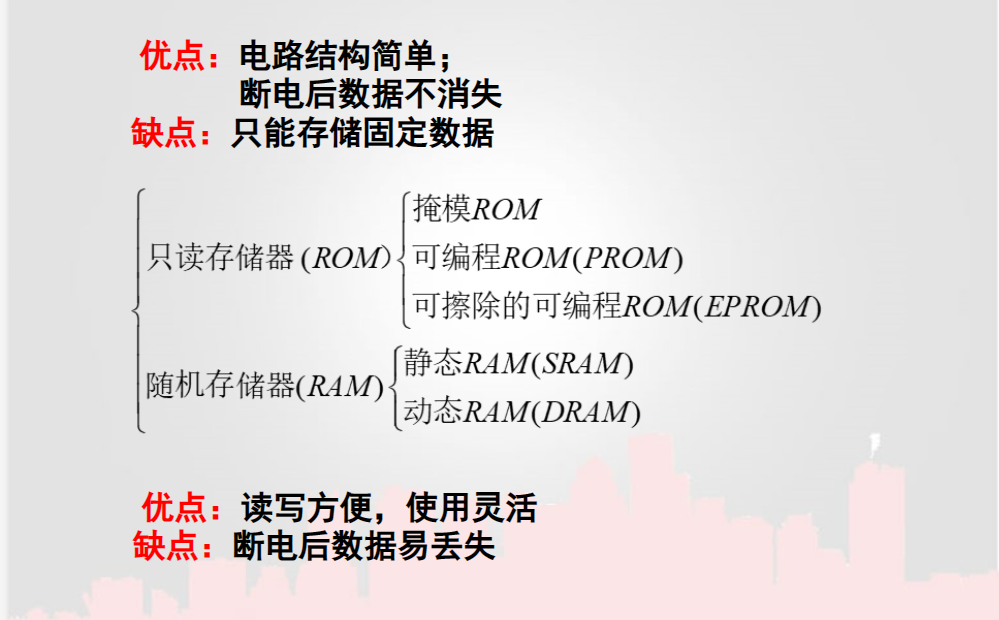

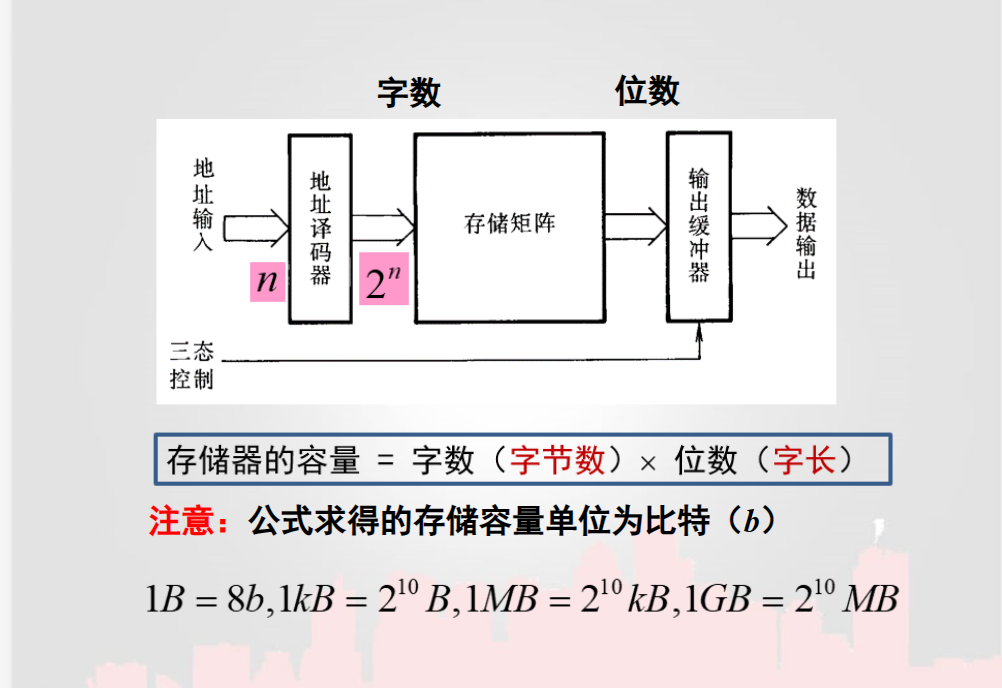

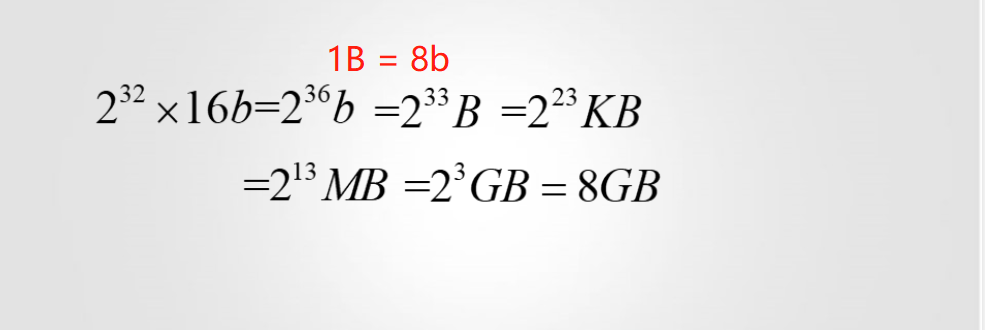

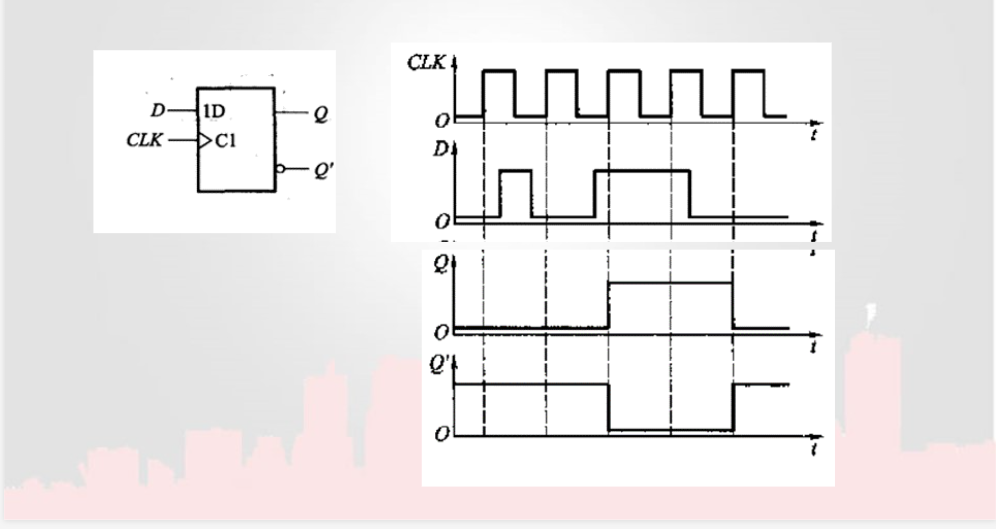

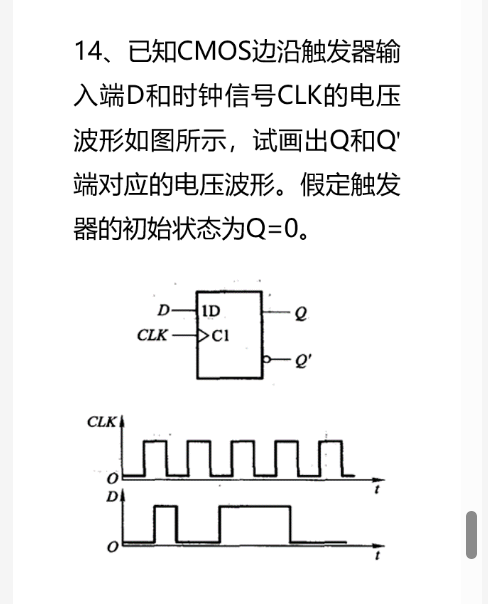

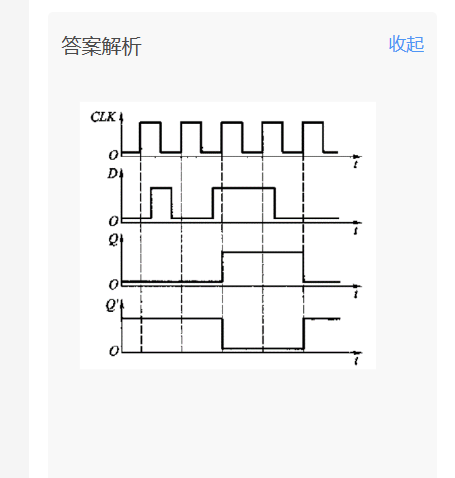

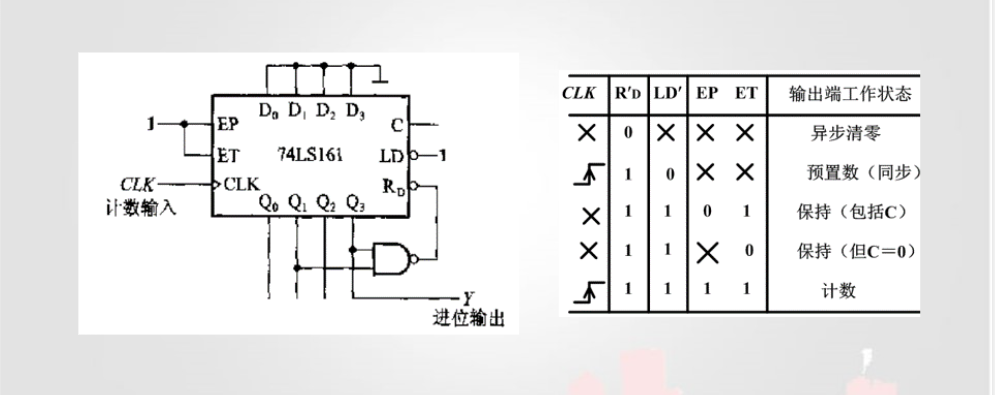

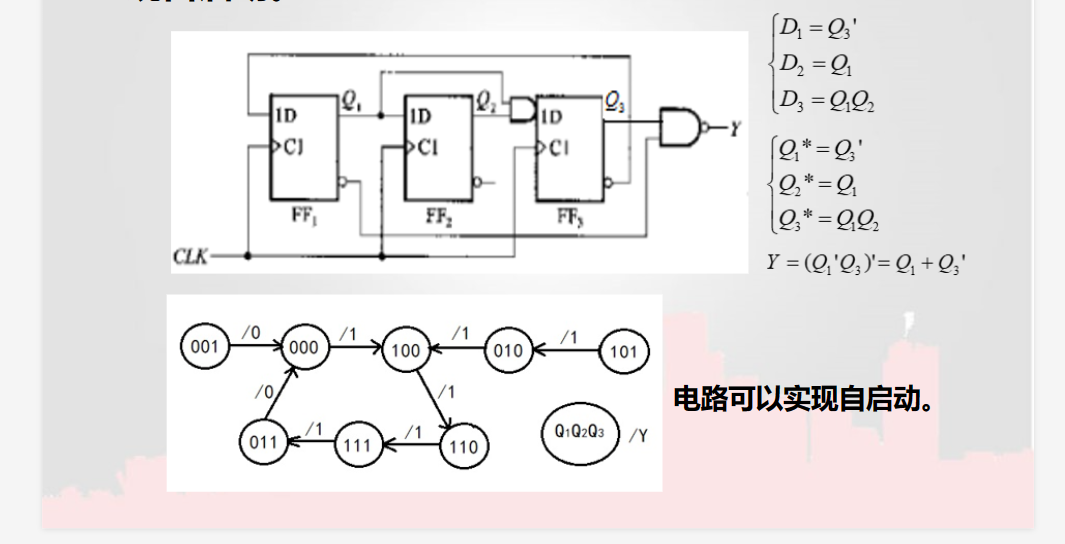

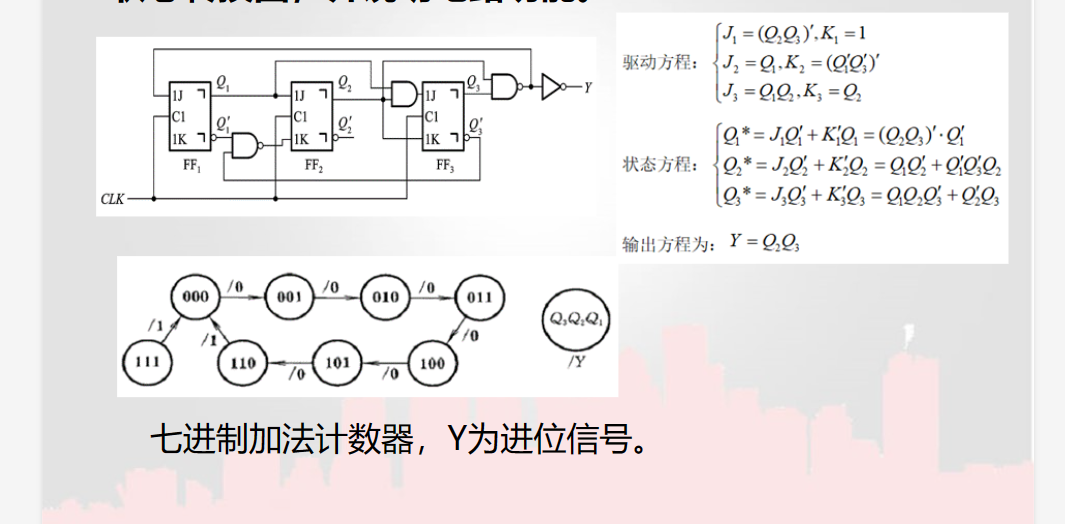

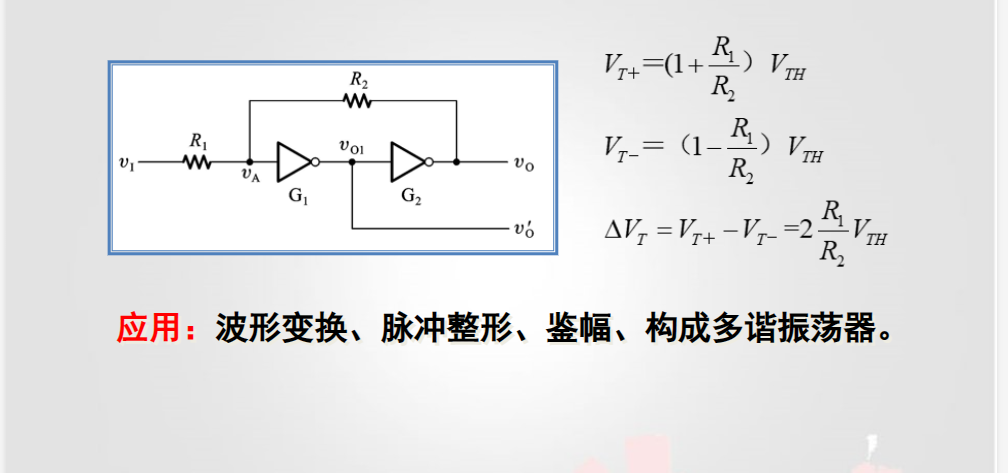

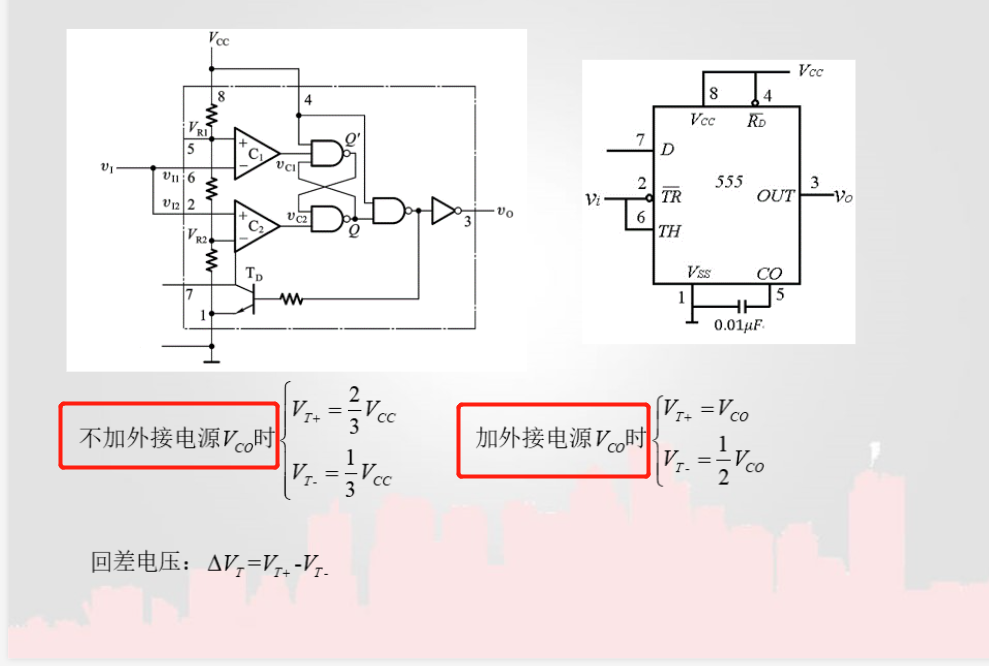

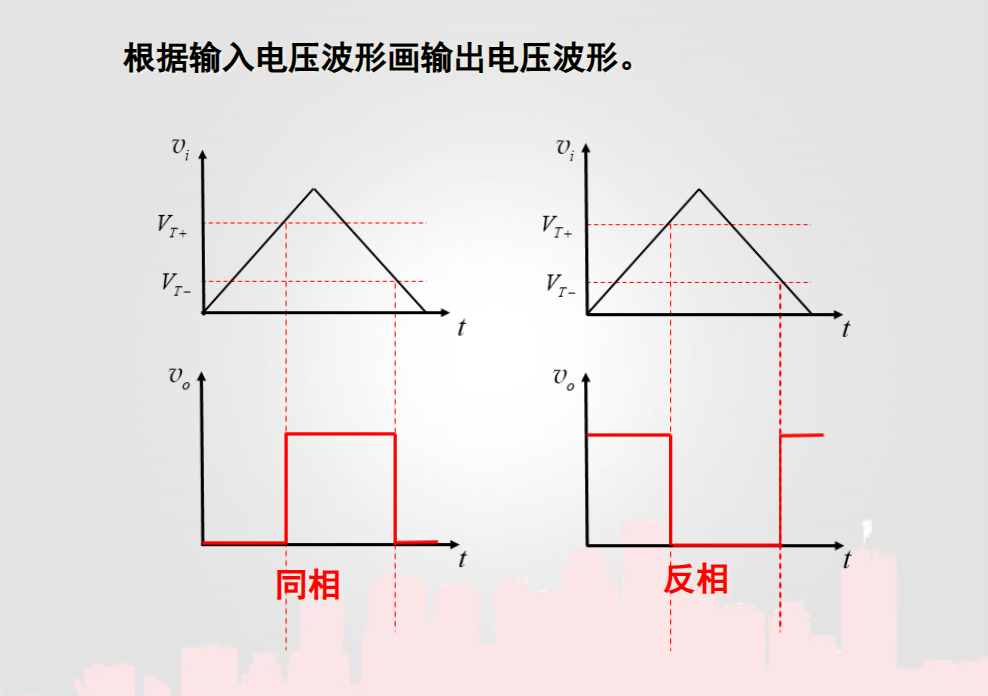

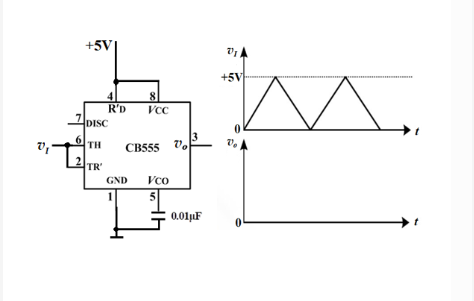

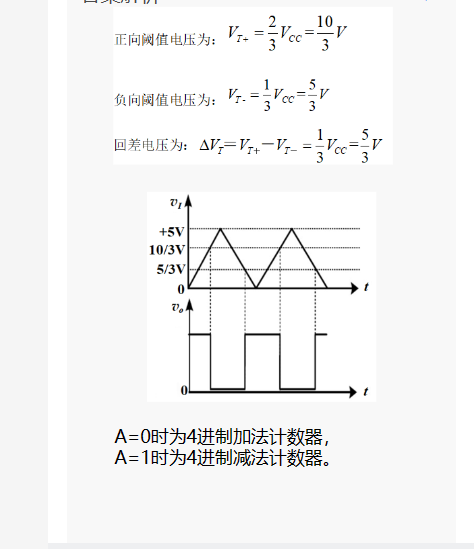

综合题 (5*10`) 1.进制转换 2.函数式化简 3.组合逻辑电路的设计 4.时序逻辑电路的分析 5.555定时器 *一 进制转换 (10010.1101)2 = ([填空1])8 = ( [填空2] )16 十进制数86.25对应的二进制数是 [填空3] 对应的八进制数是 [填空4] 带符号二进制数110011的补码为 [填空5] 十进制数+56对应的二进制补码是 [填空6] 答案:22.64 12.D 1010110.01 126.2 101101 0111000 *二 逻辑代数的运算     两次求反 一次摩根定律  反演定理: 用于求出逻辑函数反函数的定理 对于任意一个逻辑式Y 若将其中所有的“与”换成“或” “或”换成“与” 0换成1 1换成0 原变量变成反变量 反变量变成原变量 则得到一个新的逻辑式即为逻辑式Y的非 这个规律称为反演定理  计算机中在进行二进制算术运算时 若计算结果超出了有效位数所能表示数的最大值则会产生计算错误 此称为[溢出] *函数式化简 (若无方法限定 尽量使用卡诺图化简)    习题:     三 门电路 1.几种门电路及其功能  2.门电路的使用规则  TTL与非门多余端不用时 下列哪种处理方式有误 ( ) A 接地 B 悬空 C 与有用输入端连接在一起 D 接电源 具有数据双向传输功能的门电路是[三态门] 其输出状态除了高点平 低电平以外 还有[高阻态]  *四 组合逻辑电路(分析 设计) 1.组合逻辑电路的分析方法   2.组合逻辑电路的设计方法    主观题     习题:          3.常用组合逻辑电路  五 半导体存储电路 1.各类触发器  对JK触发器 J=0 K=0时触发器状态[保持] J=0 K=1时触发器状态[置0] J=1 K=0时触发器状态[置1] J=K=1时触发器状态[翻转] 对T触发器 T=0 保持 T=1 翻转 SR锁存器 由或非门构成的SR锁存器       2.半导体存储器   某台计算机的内存设置为32位地址线 16位并行数据输入/输出 则其最大存储容量 ( 8 ) GB  容量为 4Kx8位 RAM 存储器芯片 有( 12条地址输入线)( 8 条数据输出位线) 1K = 1024b 已知CMOS边沿触发器输入端D和时钟信号CLK的电压波形如图所示 试画出Q和Q'端对应的电压波形假定触发器的初始状态为Q=0    *六 时序逻辑电路(分析) 1.时序逻辑电路的分析  2.常用的时序逻辑电路  如图所示计数器电路 则该电路实现的是(十)进制计数器 74LS161的功能表已经给出  *分析下列时序逻辑电路 写出驱动方程、状态方程、输出方程、画出状态转换图 并说明电路能否实现自启动  *已知图中FF1、FF2、FF3均为主从结构的TTL触发器 要求写出驱动方程、状态方程和输出方程 画出状态转换图 并说明电路功能  *七 脉冲波形的产生和整形 1.施密特触发电路的原理和应用 *Vo`和V1反相 Vo和V1同相  2.555定时器构成的施密特触发电路 *Vo和V1反相   *用555定时器构成的施密特触发电路及输入波形如图所示 求正向阈值电压 负向阈值电压和回差电压 并试着画出对应的输出波形  答案解析:  |