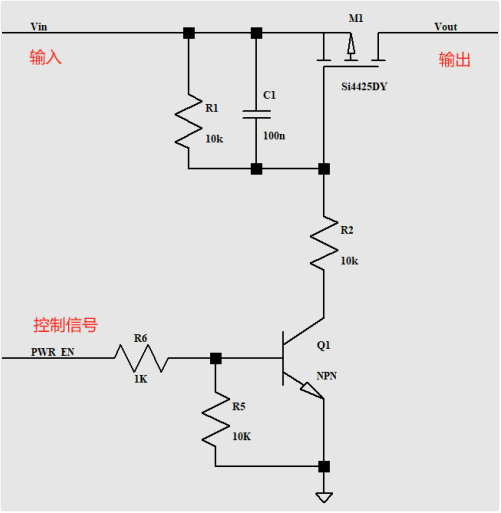

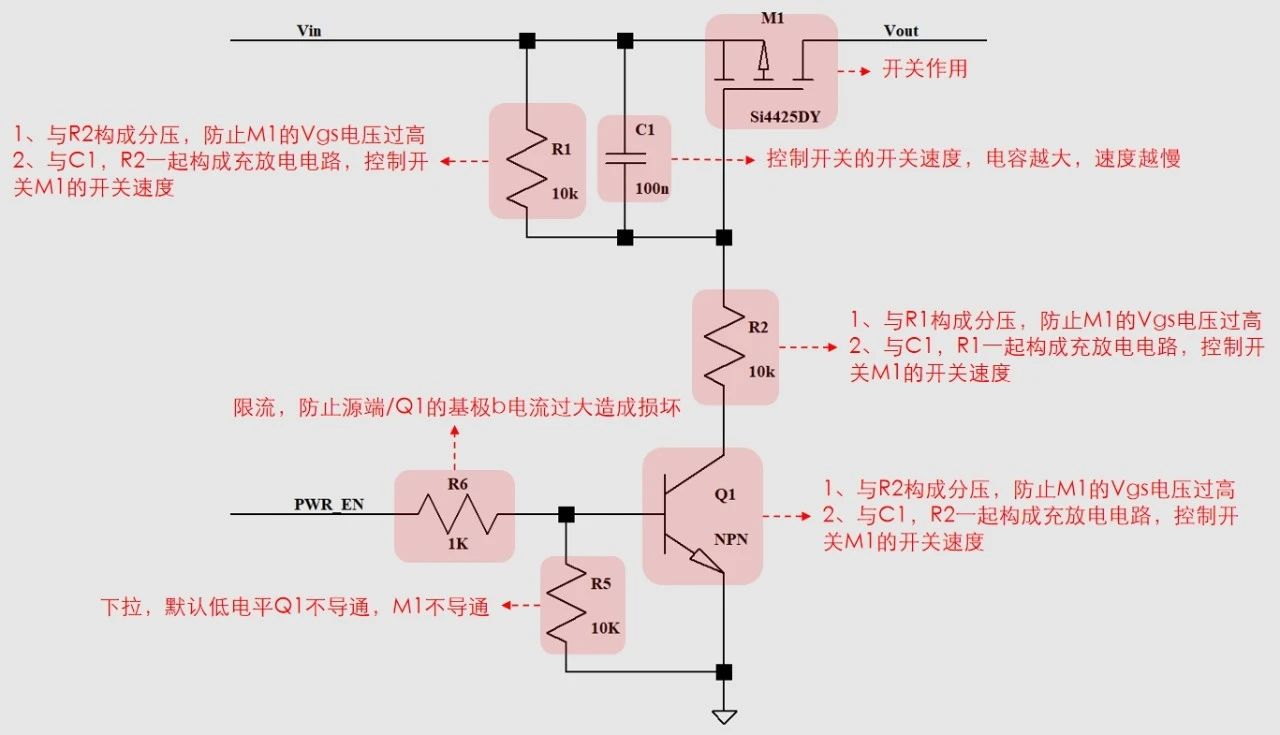

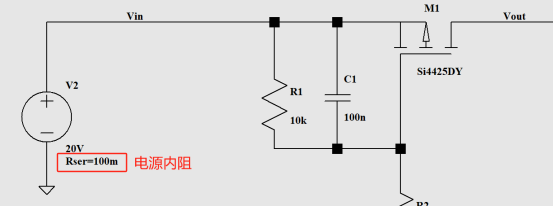

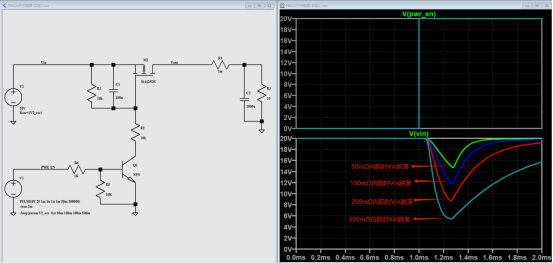

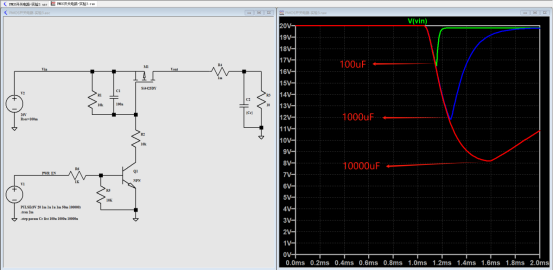

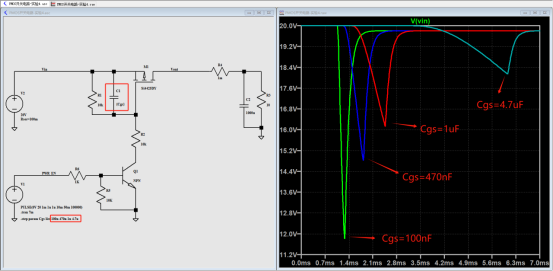

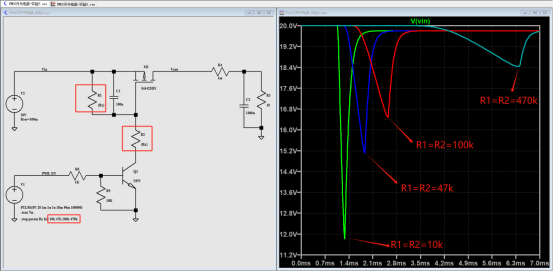

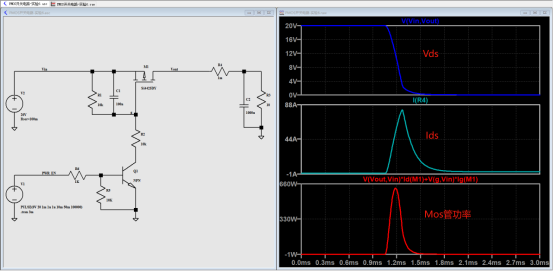

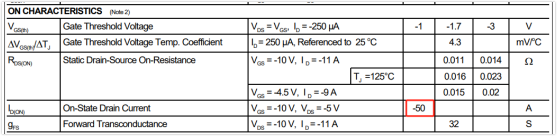

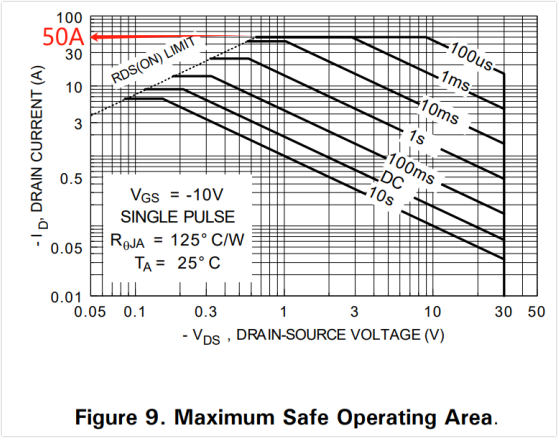

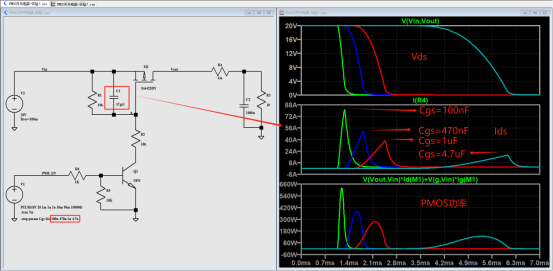

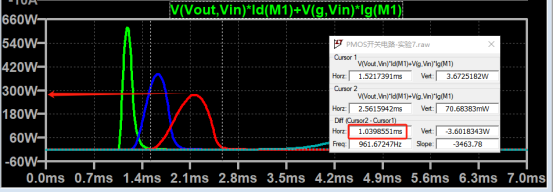

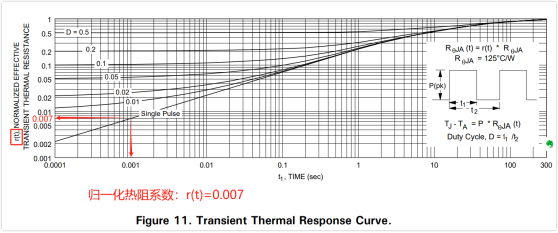

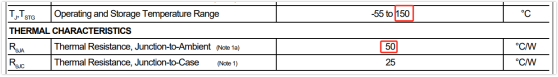

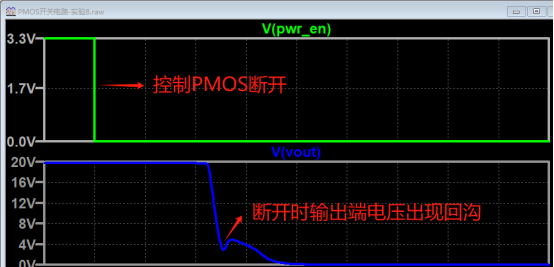

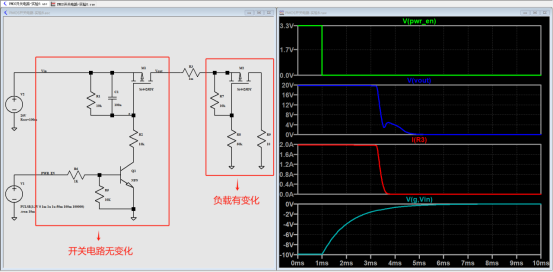

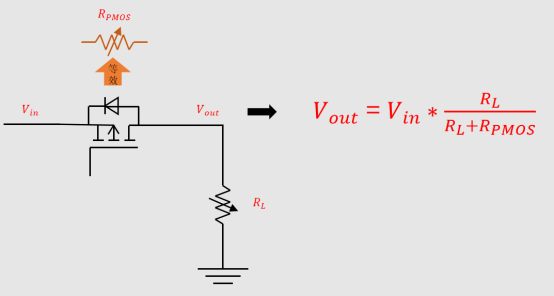

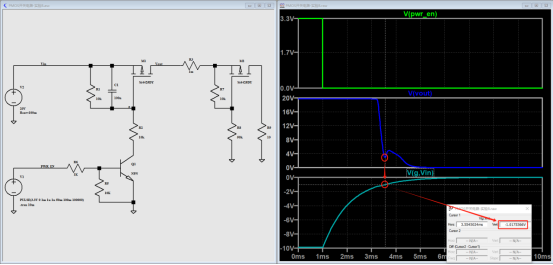

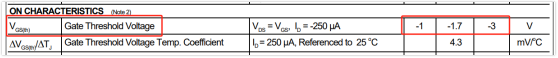

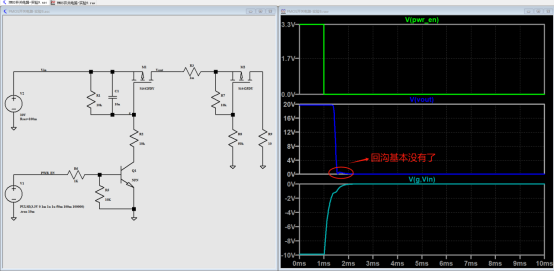

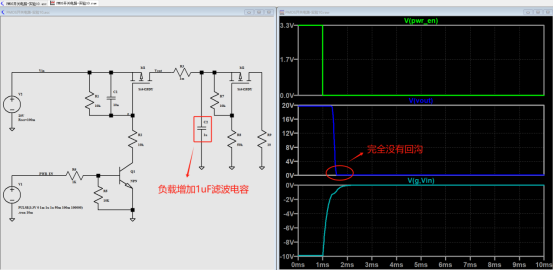

作为硬件工程师,不管做什么产品,一般都会用类似下面的PMOS开关电路,而且一般用做电源控制。 这个电路看着比较简单,但是呢,在实际应用中,稍不注意的话,可能会出现下面的几个问题: 1、PMOS开关开启的一瞬间,前级电源电压跌落,或者直接被拉死 2、PMOS开关开启的一瞬间,MOS管冲击电流太大,MOS管损坏 3、PMOS开关由开启变为断开时,输出端Vout电压先降低,后上升,然后再下降,即下电波形出现回沟  下面就来说明下这些问题是如何产生的,以及如何解决。 电路基本原理 为了照顾下刚入门的同学,还是先来解释下电路的工作原理,以及各个器件的作用 先说工作原理 1、当控制信号PWR_EN为高时,三极管Q1导通,R2下端等于接GND。由于R1和R2的分压作用,MOS管M1的Vgs会有压差Vgs=-Vin*R1/(R 1+R2),即M1最终会导通。 2、当控制信号PWR_EN为低时,三极管Q1不导通,那么R2下端相当于悬空。那么MOS管M1的栅极会被R1拉到和输入电压Vin一样,即Vgs=0,那么M1最终状态会是不导通。 所以说,我们通过控制PWR_EN的高低,就能够控制PMOS M1的导通和关断,这也就是这个电路的基本原理。 再来看下每个器件的作用。  如上图所示,各个器件的作用应该都说清楚了吧,我们继续看前面提到的实际应用中,我们可能会遇到的几个问题。 几个问题的解释及解决办法 1、PMOS开关开启的一瞬间,前级电源电压跌落,或者直接被拉死 我们把这个电路做一个仿真,加上输入20V电压,电源内阻100mΩ,负载10Ω,负载滤波电容1000uF,PMOS开通的瞬间Vin波形如下图(实验1):  可以看到,输入端Vin电源20V,在PMOS开启的时候,瞬间被拉到了11.8V。 那么为什么会如此呢? 道理其实很简单,Vout网络接了一个很大的电容1000uF,开关打开的时候,输出电压Vout从0V要上涨到20V,这个电容有就要从0V被充电到20V。如果开关的时间比较短,充电的电流就会比较大。 这一点也比较容易理解,电容从0V到20V,被充入的电荷量Q=C*U,如果开关的时间是t,那么平均充电电流就是I=Q/t=C*U/t,电容量C是已知的,为1000uF,电压U=20V,所以说这个充电电流 I=1000uF*20V/t就反比于开关的开通时间。 那充电电流大为啥输入电压就会跌落呢?我们要知道这个充电电流来源于源端,也就是电压源V2,我们联想下,工作中实际的电路,源端电源肯定不是理想的电源,总会有内阻,或者说线路上总会有阻抗,电流一大,必然会有压降,这个压降就会造成电压跌落。 需要注意,我仿真的时候,给电压源V2的内阻就是100mΩ,这也是为了模拟真实的场景,同时呢,也只有这样才能看到电源Vin有跌落的情况。如果不设定内阻,电源源V2是理想电压源,那么肯定是看不到电源跌落的。 很容易想到,如果我们把这个内阻设得大些,那么跌落得肯定更多。  我们试一下,将内阻Rser从50mΩ,100mΩ,200mΩ,500mΩ做一个对比,一起看看跌落的情况。如下图(实验2),可以看到,50mΩ时,电压Vin只跌落到了15V左右,没有像100mΩ是跌到了11.8V这么多,而500mΩ时电压已经跌落到了6V左右。  前面说到,电容平均充电电流是I=Q/t=C*U/t,C是负载的电容量,也就是说C越大,那么平均充电电流越大,源端内阻上的压降也越大,即电压跌落也会越大。 我们也可以仿真来验证下,我们设定V2的内阻为100mΩ不变,负载端电容分别是100uF,1000uF,10000uF,结果如下图(实验3)  可以看到,确实与我们的分析是一致的,100uF的时候,电压只跌落到了16.5V,相对于1000uF的11.8V,还是要小不少的。 由以上可以知道,负载端电容量越大,是越容易发生电源跌落的情况的。但是呢?有时候我们的负载就是需要那么大的电容,那怎么办呢? 其实我们还可以调整开关的速度,我们可以通过调整R1,R2,C1的大小,来调整PMOS开关开通的时间。 根据前面的公式,I=Q/t=C*U/t,如果负载电容C固定了,电压U也确定了,我们可以通过调整电路,增大开关的开通时间t,也能降低充电电流的大小,最终也可以让电源跌落更小。 还是来仿真下,我们保持电源内阻为100mΩ,滤波电容为1000uF不变,R1,R2保持10K不变。然后让开关MOS的gs之间的跨接电容分别为100nF,470nF,1uF,4.7uF,对比波形如下图(实验4)  可以看到,100nF时跌落最多,跌到了11.8V,而4.7uF的时候,跌落是最小的,另外一方面,我们也可以看到下冲的宽度,100nF时,宽度是最小的,说明此时开通速度最快。 我们保持电源内阻为100mΩ,滤波电容为1000uF不变,gs跨接电容为100nF不变,单独调整下R1和R2,让其分别等于10K,47K,100k,470k,看下效果,仿真如下图(实验5)  可以看到,效果和调节gs之间的电容差不多,在电阻调整到470k之后,输入端电压跌落已经比较小了。 好了,相信到这里,你应该已经知道了为什么PMOS开启的时候,输入电压有跌落了,以及出现这种情况之后,我们只需要调整R1,R2,Cgs就好了。 需要注意的是,以上只是为了简单说明道理,实际电路应用过程中要更为复杂。比如说我仿真内阻都是用的100mΩ,实际电路中电路不仅仅有内阻,还有电感,这些都会造成输入端有压降,但是另外一方面,输入端也会有电容,开通瞬间,输入端的电容也会给负载电容提供电流,最终跌落可能也不明显。有时呢,输入源端可能有限流保护,如果开通瞬间拉取电流过大,那么会造成前级过流保护,导致电源被拉死,这些都需要具体情况具体分析。 好了,关于这个跌落的问题就说到这里了,下面继续其他问题。 2、PMOS开关开启的一瞬间,PMOS烧毁 提到MOS烧毁,一般来说,就是其非工作在SOA区(安全工作区,Safe operating area)。 显然,在这个场景,容易出现的就是MOS管过流了。我们还是以上面的仿真电路为例子,看下导通时MOS管的电流情况。 仿真条件:PMOS型号为SI4425,电压源V2=20V,内阻=100mΩ,负载电容1000uF,R1=R2=10k,gs端跨接电容100nF。 波形如下图(实验6)  可以看到,MOS管瞬间最大电流已经达到了80A+,这个电流太大了,MOS管有风险,为什么这么说呢?我们可以看下使用PMOS管SI4425的手册,可以看到,其最大允许的电流是50A。  这一点,我们也可以从其SOA曲线上看出来。  此时,这个PMOS超规格使用了,并没有工作在SOA区间,是可能会损坏的。 那怎么办呢?选更高电流的PMOS吗?当然,这是一个可选的方案,不过呢,电流更高的PMOS价格肯定会更高的。此时我们可以调节下外围电阻或是电容,让PMOS更慢开通,这样可以将电流降下来。 按照前面说的,我们可以调整R1,R2,C2(gs间跨接电容)达到这个目的。我们将gs间跨接电容分别调至470nF,1uF,4.7uF,对比看看电流的情况,如下图(实验7)。  可以看到,在Cgs=1uF的时候,此时Ids最大只有40A,而PMOS SI4425最大瞬间电流可以过50A,仅从电流Ids来考虑,是OK的,并且满足80%的降额(50A*0.8=40A)。 假如我们选定Cgs=1uF,我们还需要看下此时的功率是否有超标(结合SOA曲线看),从曲线上看,MOS管开通时间约为1ms,这期间最大功率约为280W,如下图。  假设这个PMOS应用场景是单脉冲(即非周期性开通,只是偶尔开通一次),从手册看到其1ms时归一化热阻系数r(t)=0.007。  芯片正常热阻是Rja=50℃/W,最高结温是150℃,假设环境温度是25℃,那么其1ms能抗的瞬间功率是:Pmax={(150℃-25℃)/Rja}/r(t)= 357W  即PMOS SI4425在1ms瞬间能扛的功率是357W,而将Cgs电容调整到了1uF之后,实际功率是280W,因此并没有超过PMOS的功率限制,也即是说其工作在了SOA区,是OK的。 综上所述,在Cgs是100nF的时候,PMOS没有工作在SOA区,而我们调整Cgs电容到1uF之后,PMOS就能工作在SOA区,因此就不会出现损坏的问题了。 以上是从仿真的角度看PMOS有没有损坏的风险。实际在我们电路应用中,对于这种功率PMOS做开关,我们一般也是要去测量PMOS开通时的电压和电流曲线,以此来判断是否是安全的。 再来说一个我曾经遇到过的奇特现象,也就是第3个问题。 3、PMOS开关由开启变为断开后,输出端Vout电压先降低,后上升,然后再下降,即下电波形出现回沟 先看下这是个什么现象,如下图,在PMOS断开的时候,输出电压Vout出现回沟  这个波形是用下面这个电路仿真出来的(实验8)  相对于前面的PMOS开关仿真电路,其实没有差异,仅仅是我将负载换成了一个开关电路而已,那为什么改变了负载之后,Vout的下电波形就不正常了呢?遇到这种情况我们该如何调整呢? 原因其实也不难理解,就是PMOS从导通到关断,总有一个过程,PMOS的阻抗会从接近于0(导通)到电阻无穷大(断开),也就是说存在一段时间,PMOS的会有一定的阻值,而负载也非恒定电阻。在Vout下电过程中,负载获得的电压下降到一定程度,负载电路可能因为欠压突然停止工作,其所需电流急剧减小,即其等效电阻突然变大,那么会导致其获得的分压变大,这个时候就会出现上面的情况,Vout电压又涨上去了。 上面的过程简单画个示意图如下所示:Vout的电压等于Vin在PMOS和负载上面的分压,如果负载RL突然变大,那么就有可能出现Vout突然上涨的情况。  经过上面的分析,应该很容易想到,出现回沟的地方,应该就是PMOS从导通到关断切换的时刻,也就是PMOS的Vgs电压等于其Vgsth的时候,关于这一点,我们也可以从仿真波形中看出,如下图所示。  回沟出现的地方,就是PMOS的Vgs=-1V的时候,我们可以从SI4425手册中看到,该PMOS的Vgsth就是-1V~-3V,印证我们前面的分析没毛病。  那么问题又来了,我们如何解决这个回沟的问题呢? 很多时候,我们让这个PMOS更快的关闭就能解决了,比如我们将PMOS的g和s跨接的电容从100nF调整到10nF,可以看到回沟基本没有了(只有500mV左右,实际电路一般不影响使用),如下图所示(实验9)  我们也可以在输出端加一个滤波电容,这样可以避免负载等效RL突然变大。 这个原理是这样的:加了滤波电容后,等效负载就变成了原本的RL和新加的电容阻抗的并联,所以哪怕原本的RL突然变得很大,因为有电容阻抗的存在,总的负载阻抗也不会变得很大(不会超过电容的阻抗)。我们现在讨论的是pmos关断的瞬间,这个过程是短暂的,信号可以看成是交流,因此电容不可看成是开路,它也构成了总的阻抗的一部分。所以,只要电容值合理,是可以解决电容回沟的问题的。 印证下,我们在上面的电路的负载端加一个1uF的滤波电容,仿真如下(实验10)  可以看到,Vout此时完全没有回沟了,下电波形非常好。 小结 本期内容就写到这里了,可以看到,小小的PMOS电路,其门道也是不少的,毕竟我们都没有办法固定一个电路去适应所有的应用场景。一个电路,可能用在这个场景没问题,用在其他场景就出问题了。当然,这也并不可怕,我们只需要理解问题的原因是什么,结合测试,根据波形,不断分析优化,也就能设计出安全可靠的电路了。 |