|

本文详细介绍了半导体制造过程中良率的提高分析,运用大量实例说明如何提高良率,作为测试工程师在CP测试中遇到低良率情况时,可以参考此资料,以分析测试及wafer各方面问题,另外本资料也特别适合wafer制造工程师在遇到客户投诉低良率情况下,对wafer为何出现低良的分析,主要内容如下:

CONTENT

Overview

Methodology Introduction

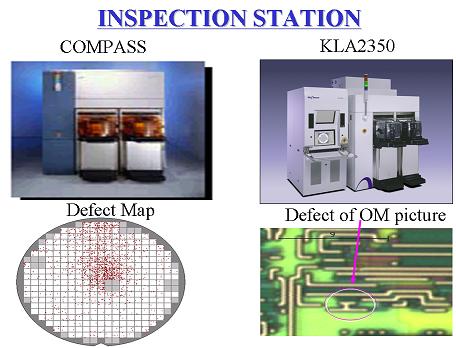

Basic YE Tools & Its Inspection Theories

Problem Description

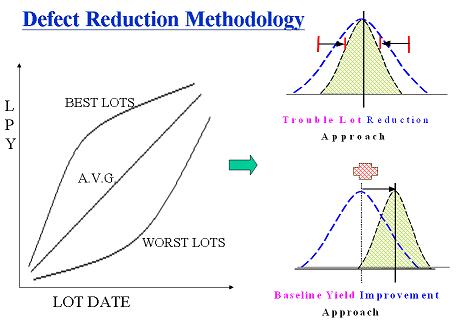

Particle / Defect Reduction Strategy

In-line Monitor General Flow

Trouble Shooting Methodology

Defect Library

Yield Management System /Modeling

Contamination control practice

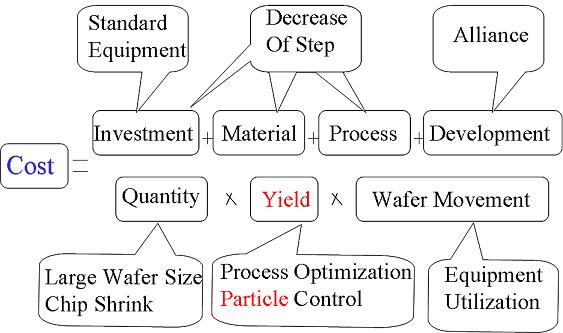

Low Cost Manufacturing

Yield (良率) Definition

Typical Value

FAB Yield : > 96%

WAT(Wafer Acceptance Test) Yield : > 99%

CP(Chip Probe) Yield : > 80%

Package / Assembly Yield : > 99.5%

Room Temp Test Yield : > 95%

Burn-in Test Yield : > 92%

Final Test Yield : > 95%

Total Yield : 62.8%

@What is YE

YE stand for Yield Enhancement

@缺陷改善工程(Defect Reduction Engineering)

当IC制程持续往轻,薄,短,小及高密度方向发展时,对任何缺陷容忍度将自然相对降低,也即其灵敏度讲大幅提高,所以,想得到良率之提升就必须设法降低缺陷之密度.

How SAMSUNG Increase Device Yield

High Quality Clean Room

Quick and Flexible response to Problems

Ultra Clean Utilities

Well Trained Operators

Excellent Engineering Resources

Quality Maintenance

Customized Equipment

Tight Process Control

Design Optimization for Each Production Line

Data Automation

………………

………………

具体请下载参考:

training material of Yield Enhancement.part01

training material of Yield Enhancement.part02

training material of Yield Enhancement.part03

training material of Yield Enhancement.part04

training material of Yield Enhancement.part05

training material of Yield Enhancement.part06

training material of Yield Enhancement.part07

training material of Yield Enhancement.part08

training material of Yield Enhancement.part09

training material of Yield Enhancement.part10

|