师爷之前讲过关于集成电路设计、晶圆代工、封装等,但对于芯片测试这一块较少涉及,今天就来给大家科普下吧!

为什么要进行芯片测试?

芯片测试是一个比较大的问题,直接贯穿整个芯片设计与量产的过程中。

首先芯片fail可以是下面几个方面:

功能fail,某个功能点点没有实现,这往往是设计上导致的,通常是在设计阶段前仿真来对功能进行验证来保证,所以通常设计一块芯片,仿真验证会占用大约80%的时间。

性能fail,某个性能指标要求没有过关,比如2G的cpu只能跑到1.5G,数模转换器在要求的转换速度和带宽的条件下有效位数enob要达到12位,却只有10位,以及lna的noise figure指标不达标等等。这种问题通常是由两方面的问题导致的,一个是前期在设计系统时就没做足余量,一个就是物理实现版图太烂。这类问题通常是用后仿真来进行验证的。

生产导致的fail。这个问题出现的原因就要提到单晶硅的生产了。学过半导体物理的都知道单晶硅是规整的面心立方结构,它有好几个晶向,通常我们生长单晶是是按照111晶向进行提拉生长。但是由于各种外界因素,比如温度,提拉速度,以及量子力学的各种随机性,导致生长过程中会出现错位,这个就称为缺陷。

缺陷产生还有一个原因就是离子注入导致的,即使退火也未能校正过来的非规整结构。这些存在于半导体中的问题,会导致器件的失效,进而影响整个芯片。所以为了在生产后能够揪出失效或者半失效的芯片,就会在设计时加入专门的测试电路,比如模拟里面的testmux,数字里面的scan chain(测逻辑),mbist(测存储),boundry scan(测io及binding),来保证交付到客户手上的都是ok的芯片。而那些失效或半失效的产品要么废弃,要么进行阉割后以低端产品卖出。

这些芯片fail要被检测出来,就必须要进行芯片测试了。

芯片测试在什么环节进行?

现在芯片面积越来越大,测试相当具有挑战性。所以如何测试其实是一门很深的学问。由于信号过多,不可能把每个信号都引出来测试,所以肯定在设计的时候就要做可测性实际,就是DFT。

DFT简而言之,DFT就是通过某种方法间接观察内部信号的情况,例如scan chain之类。然后通过特定的测试仪器来测试——这种仪器不是简单的示波器,它要能产生各种测试波形并检测输出,所以一套平台大概要上百万。而且这些DFT比较适合于小芯片,大芯片像CPU之类的还会使用内建自测试(built-in self test),让芯片自己在上电后可以执行测试,这样就大大减小了测试人员的工作量。

DFT测试通过之后,就到正式的芯片测试环节了。

一般是从测试的对象上分为WAT、CP、FT三个阶段,简单的说, 因为封装也是有cost的, 为了尽可能的节约成本, 可能会在芯片封装前, 先进行一部分的测试, 以排除掉一些坏掉的芯片. 而为了保证出厂的芯片都是没问题的, final test也即FT测试是最后的一道拦截, 也是必须的环节.

WAT: Wafer Acceptance Test,是晶圆出厂前对testkey的测试。采用标准制程制作的晶圆,在芯片之间的划片道上会放上预先一些特殊的用于专门测试的图形叫testkey。这跟芯片本身的功能是没有关系的,它的作用是Fab检测其工艺上有无波动。因为代工厂只负责他自己的工作是无误的,芯片本身性能如何那是设计公司的事儿。只要晶圆的WAT测试是满足规格的,晶圆厂基本上就没有责任。如果有失效,那就是制造过程出现了问题。

WAT的测试结果多用这样的图表示:

CP:Circuit Probe,是封装前晶圆级别对芯片测试。这里就涉及到测试芯片的基本功能了。不同项目的失效,会分别以不同颜色表示出来。失效的项目反映的是芯片设计的问题。

通过了这两项后, 晶圆会被切割. 切割后的芯片按照之前的结果分类. 只有好的芯片会被送去封装厂封装. 封装的地点一般就在晶圆厂附近, 这是因为未封装的芯片无法长距离运输. 封装的类型看客户的需要, 有的需要球形BGA, 有的需要针脚, 总之这一步很简单, 故障也较少. 由于封装的成功率远大于芯片的生产良品率, 因此封装后不会测试.

FT:Final test,封装完成后的测试,也是最接近实际使用情况的测试,会测到比CP更多的项目,处理器的不同频率也是在这里分出来的。这里的失效反应封装工艺上产生的问题,比如芯片打线不好导致的开短路。

FT是工厂的重点,需要大量的机械和自动化设备。它的目的是把芯片严格分类。以Intel的处理器来举例,在FinalTest中可能出现这些现象:

虽然通过了WAT,但是芯片仍然是坏的。

封装损坏。

芯片部分损坏。比如CPU有2个核心损坏,或者GPU损坏,或者显示接口损坏等。

芯片是好的,没有故障。

这时,工程师需要和市场部一起决定,该如何将这些芯片分类。打比方说,GPU坏了的,可以当做无显示核心的'赛扬'系列处理器。如果CPU坏了2个的,可以当'酷睿i3'系列处理器。芯片工作正常,但是工作频率不高的,可以当'酷睿i5'系列处理器。一点问题都没有的,可以当'酷睿i7'处理器。

那这里的FinalTest该怎样做?

以处理器举例,FinalTest可以分成两个步骤:

自动测试设备(ATE)

系统级别测试(SLT)

2是必要项,1一般小公司用不起。

ATE的测试一般需要几秒,而SLT需要几个小时,ATE的存在大大的减少了芯片测试时间。

ATE负责的项目非常之多,而且有很强的逻辑关联性。测试必须按顺序进行,针对前列的测试结果,后列的测试项目可能会被跳过。这些项目的内容属于公司机密,比如电源检测,管脚DC检测,测试逻辑(一般是JTAG)检测,burn-in,物理连接PHY检测,IP内部检测(包括Scan,BIST,Function等),IP的IO检测(比如DDR,SATA,PLL,PCIE,Display等),辅助功能检测(比如热力学特性,熔断等)。

这些测试项都会给出Pass/Fail,根据这些Pass/Fail来分析芯片的体质,是测试工程师的工作。

SLT在逻辑上则简单一些,把芯片安装到主板上,配置好内存,外设,启动一个操作系统,然后用软件烤机测试,记录结果并比较。另外还要检测BIOS相关项等。

图片是测试厂房的布置

而所有的这些工作,都需要芯片设计工程师在流片之前都设计好。测试工作在芯片内是由专属电路负责的,这部分电路的搭建由DFT工程师来做,在流片后,DFT工程师还要生成配套输入矢量,一般会生成几万个。这些矢量是否能够正常的检测芯片的功能,需要产品开发工程师来保证。此外还需要测试工程师,产品工程师,和助手来一同保证每天能够完成几万片芯片的生产任务不会因为测试逻辑bug而延迟。

考虑到每一次测试版本迭代都是几十万行的代码,保证代码不能出错。需要涉及上百人的测试工程师协同工作,这还不算流水线技工,因此测试是费时费力的工作。实际上,很多大公司芯片的测试成本已经接近研发成本。

WAT与FT比较

WAT需要标注出测试未通过的裸片(die),只需要封装测试通过的die。

FT是测试已经封装好的芯片(chip),不合格品检出。

WAT和FT很多项目是重复的,FT多一些功能性测试。

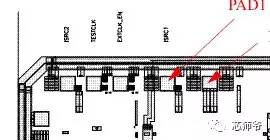

WAT需要探针接触测试点(pad)。测试的项目大体有:

开短路测试(Continuity Test)

漏电流测试(Stress Current Test)

数字引脚测试(输入电流电压、输出电流电压)

交流测试(scan test)功能性测试

所以如果有什么大问题,设计阶段就解决了(或者比较惨的情况下放弃产品,重新设计)。如果生产过程有大的问题,从圆片测试开始也层层筛选掉了。所以剩下的芯片都是精英中的精英,一眼看过去都是完美的成品。

接着主要由探针测试来检验良率,具体是通过专业的探针上电,做DFT扫描链测试。这些扫描链是开始设计时就放好的,根据设计的配置,测试机简单的读取一下电信号就之后这块芯片是不是外强中干的次品。

其实好的、成熟的产品,到这一步良品率已经很高了(98%左右),所以更多时候抽检一下看看这个批次没出大篓子就行了。

具体芯片测试项目流程如下

接到客户的芯片资料,通常是正在开发的芯片,资料严格保密,有时候芯片还在design阶段就会开始联系合作的测试公司开始准备测试项目,以缩短整个开发周期;

根据芯片资料设计测试方案(test plan),这个过程经常会有芯片功能或者逻辑不明确的地方,所以需要与设计工程师反复沟通review。

根据测试方案需要设计硬件接口电路板(DIB:Device Interface Board)。

根据测试方案开发软件程序,如果项目巨大会分成多个module由多名工程师合作完成。3和4一般会同步进行。

第3和4步准备好后,就开始在tester上进行调试,一般是在测试公司的demo room进行。Bin1后release到工厂开始产线调试。

以上各步骤偶尔会出现错误,就需要不断调整返回到出现错误的地方更正。我经历的最严重的错误是发现芯片设计有问题,项目推倒重来。

final release

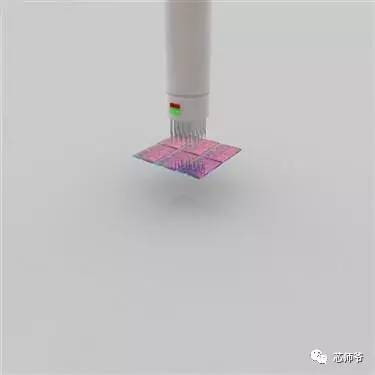

上几张测试照片给大家一个感性认识

以上是WAP测试

以上是CP测试

以上是FT测试

当然具体是研发过程更为复杂和折腾,这里就不一一展开了。

最后说一下,测试非常辛苦,芯片可测性设计以及测试方法论是非常重要也非常深刻的话题。欢迎各位芯粉留言讨论。

|

|