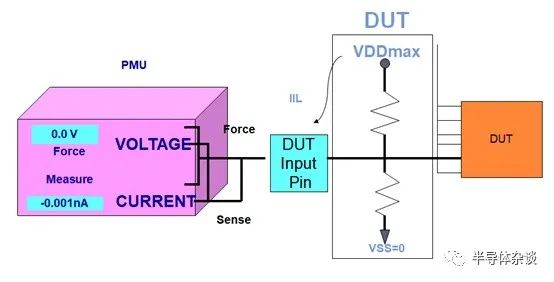

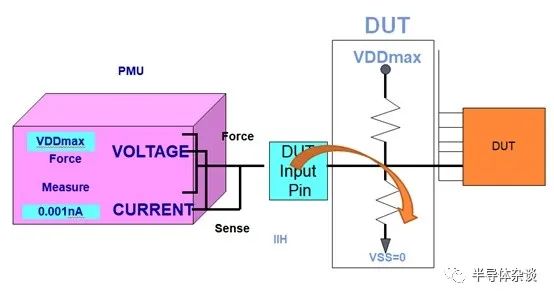

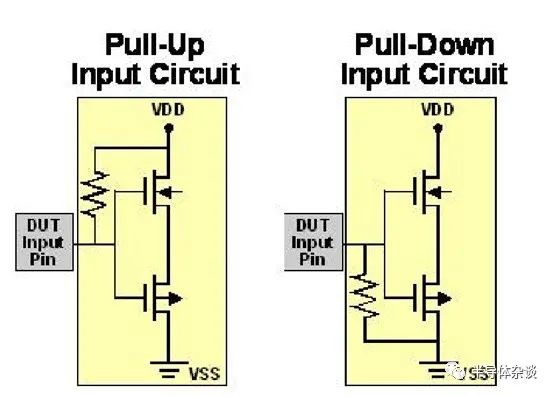

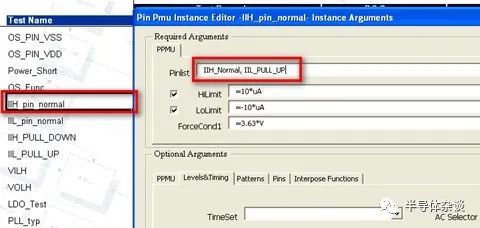

Leakage的含义是漏电,测试的对象是input pin,即测量输入管脚在输入时是否存在漏电,以及漏电的大小是否在设计要求之内。有两点问题需要注意下,一是确定测试对象,二是有没有上下拉电阻。针对问题一,测试对象是input pin,此时需要注意input pin可直接进行测量,但如果是IO pin,需要配置到input状态(这个问客户)。问题二是否存在上下拉电阻,问客户或者根据实际测量结果去判断,limit的制定询问客户。下面就介绍下leakage的测试原理,首先是IIL测试,如下图所示。 执行如下步骤: 1:VDD施加VDDmax电压 2:Run pattern将IO pin配置到input状态(if needed) 3:PPMU force 0V to leakage pins 4:量测leakage pins的电流 5:根据limit判断结果(客户给spec或者更据golden制定) 备注:IIL电流正常情况下是负的,测的是DUT到电源端的漏电(思考下原理原因),这里还是涉及串行并行的问题,因为pin与pin short前面已经通过os_func测试了,这里并行测试就不用再管pin to pin short。 IIH测试如下图:  执行如下步骤: 1:VDD施加VDDmax电压 2:Run pattern将IO pin配置到input状态(if needed) 3:PPMU force VDDmax to leakage pins 4:量测leakage pins的电流 5:根据limit判断结果(客户给spec或者更据golden制定) 备注:IIH电流正常情况下是正的,测的是DUT端到VSS的漏电(思考下原理原因) 以上测试是没有上下拉电阻存在的情况,如果存在上下拉电阻,那么就要根据电阻值的大小去计算了。这里介绍一个概念,芯片管脚上的上下拉电阻。上拉电阻(pull_up )是指一端接电源端,下拉电阻(pull_down)是指一端接VSS端。其中上下拉电阻的作用百度可查,这里不做介绍。因为有上下拉电阻的存在,这些pin要单独分出来进行测试。电流的理论值为I=V/R  这里还有一个隐藏问题,测试IIL_Normal pin时要把pull_down pin一起加入测试,测量IIH_normal pin时要把pull_up pin加入一起测试。(想下为什么)  |