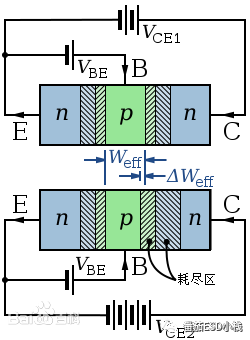

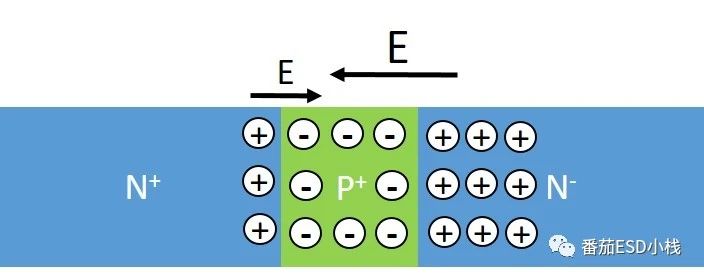

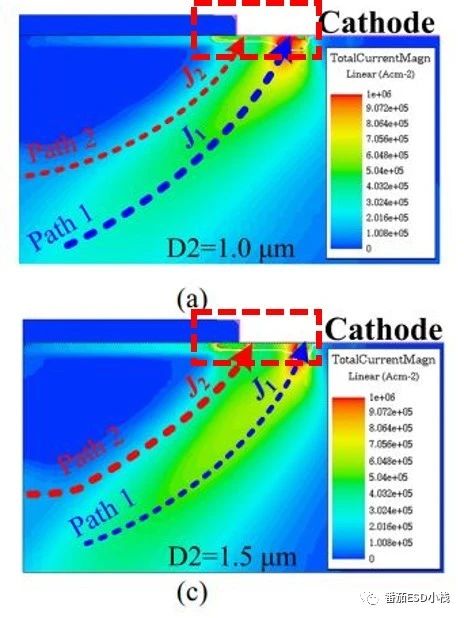

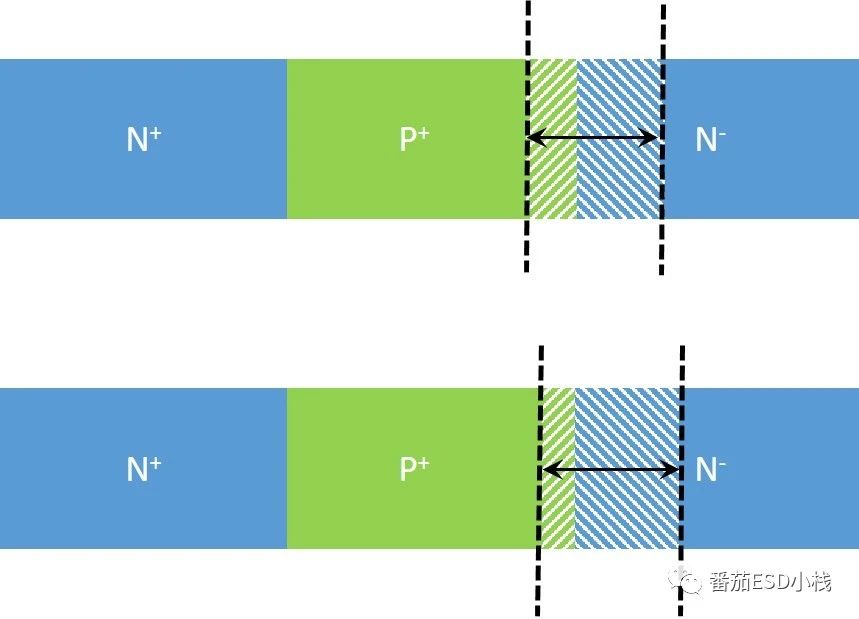

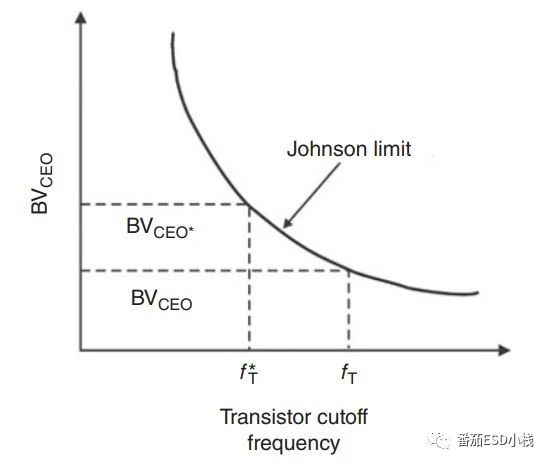

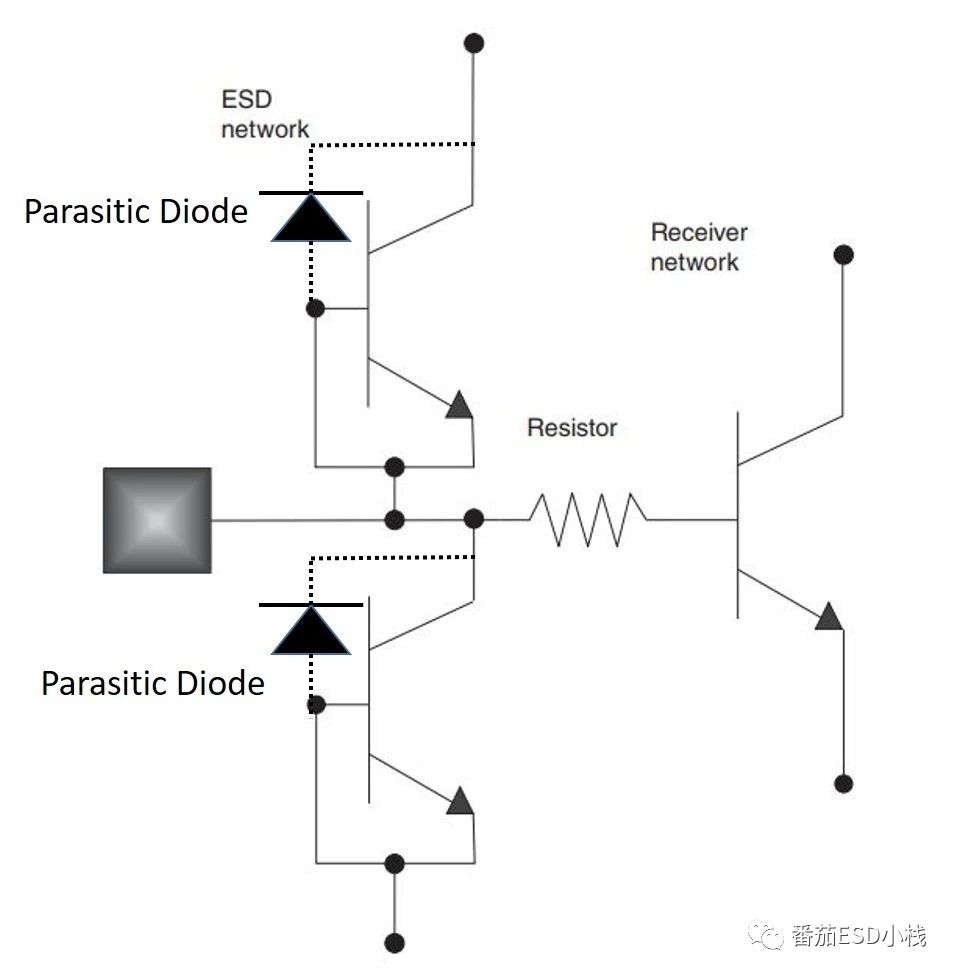

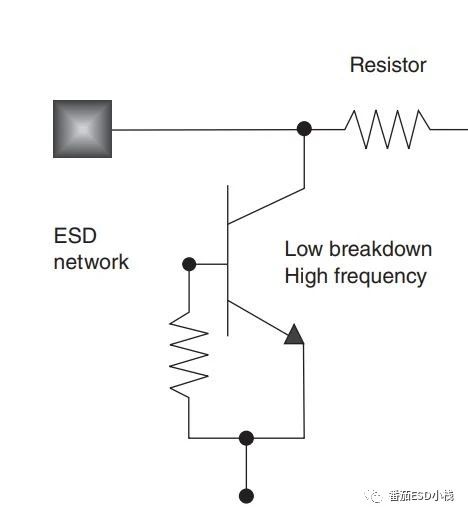

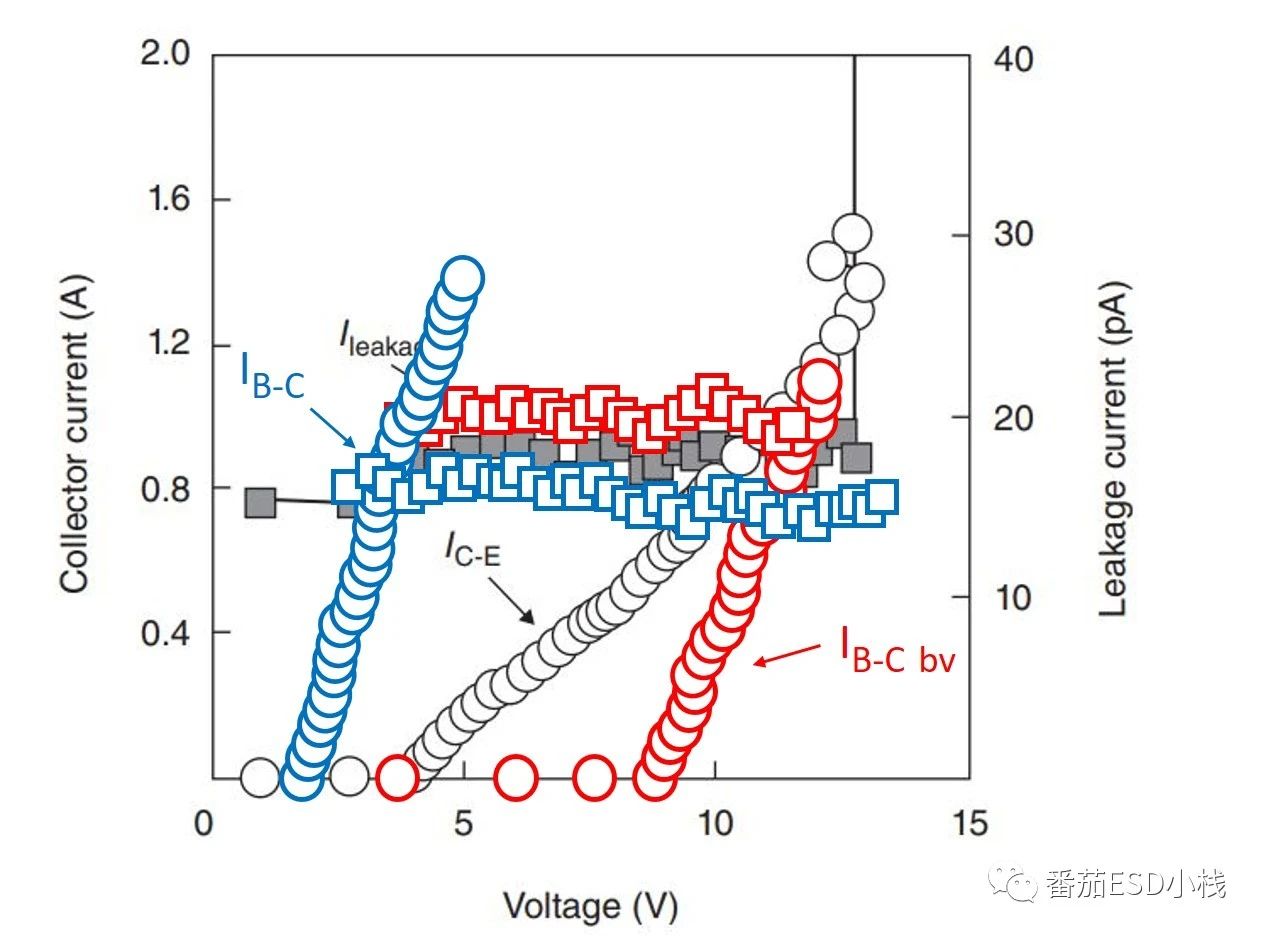

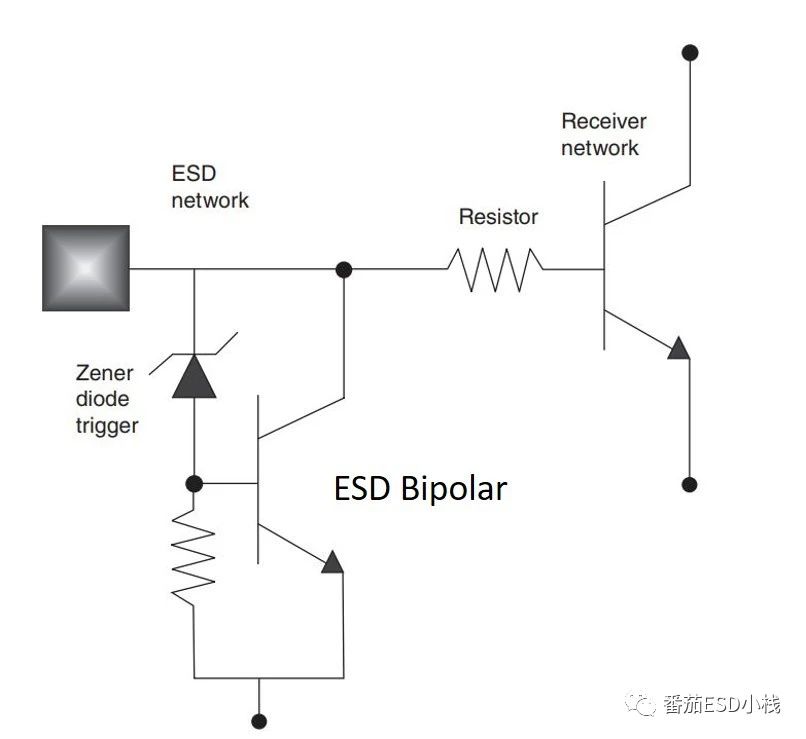

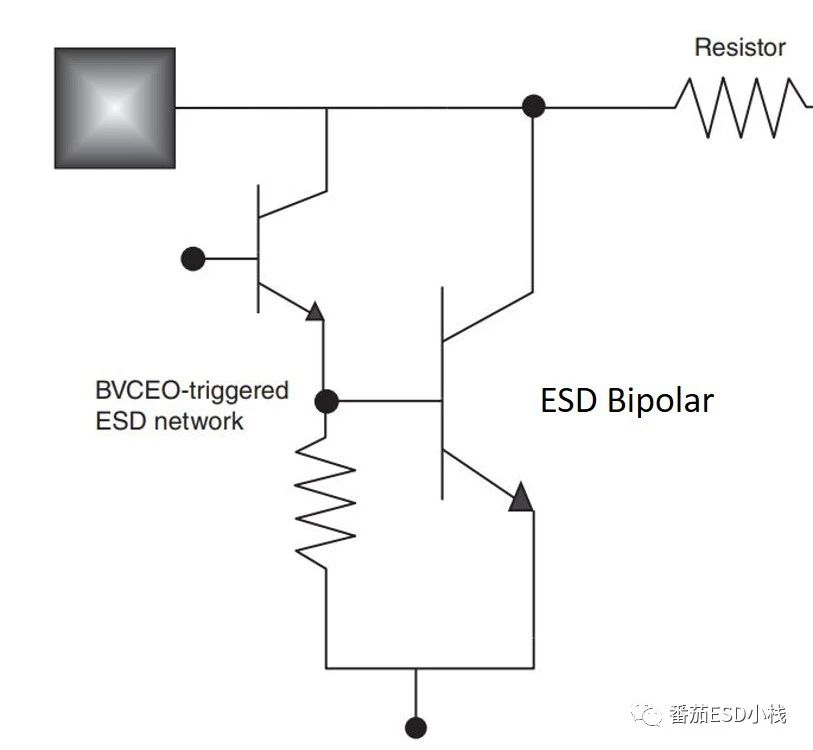

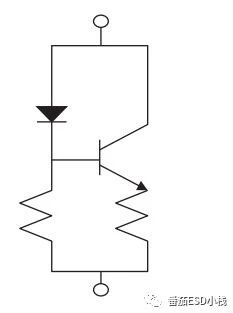

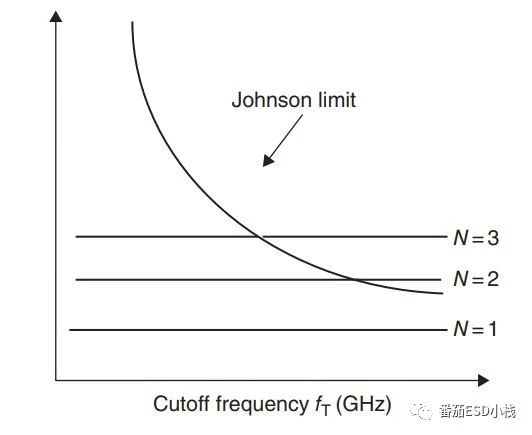

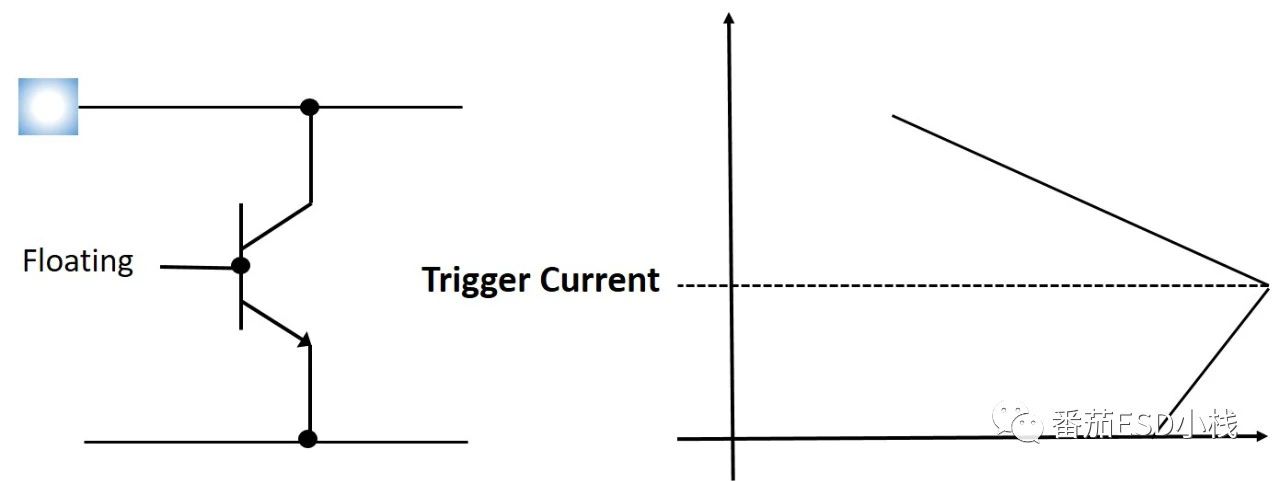

从最早的TTL工艺,到现阶段的BCD工艺,再到三代半导体工艺,Bipolar作为有源器件之一,同样具有优异的ESD防护潜力而本文主要聚焦于TTL/BCD工艺和部分CMOS工艺的片内ESD防护设计,片外/板级ESD独立防护器件这里就暂且不论。一.Bipolar工作原理不过笔者这里要强调的是MOS管作为电压驱动器件,通过栅压构建沟道,利用电压控制电流。而Bipolar作为电流驱动器件,通过基级复合电流控制从射电极进入集电极的载流子,从而实现电流控制电流。对于Bipolar来说电压的作用只是确定其工作状态,使集电极与基级反偏,射电极与基级正偏。 从ESD鲁棒性的角度来说Bipolar泄放大电流的能力更强, 更适合作为ESD防护器件。且Bipolar失效原因主要是热电失效,而MOS管的栅极较为脆弱,容易产生过电应力失效。但是Bipolar作为ESD器件要求较高的隔离性能,如果隔离不到位的话,ESD电流会进入衬底中,使得整个芯片都面临风险。而CMOS工艺因为Mask层次浅,无法有效隔离,所以很少使用Bipolar作为ESD防护器件。而在BCD工艺中,因为深槽隔离、埋层、高压阱的存在,器件层次深,能将ESD与核心电路进行隔离,所以能支持Bipolar应用于ESD防护。 二.Bipolar的二极效应。 1. Early 厄利效应 又名基区宽度调制效应,指基区的有效宽度随集电极的反偏电压变化而变化的效应。当集电极反向偏压电压增大时,集电级的空间电荷区加宽,引起基区有效宽度变窄,如图一所示。  图一.厄利效应示意图。 如图二所示,由于厄利效应,在设计ESD Bipolar时需要拉宽基级宽度,避免在高反偏电压下基级的空间电荷区进入射电极,造成器件射电极与集电极短路。  图二.射-集电极短路示意图。 2. Webster效应 又名电导调制效应,因为电中性条件,在大注入时额外积累起来的多子浓度与掺杂浓度相当,这时基区的电导率取决于基区掺杂浓度与额外多子浓度的总和(换句话说,大注入的结果就相当于增加了基区掺杂浓度),从而大幅度增加了基区的有效电导率,相当于增加了基区的掺杂浓度,使得基区的电阻率下降。  图三.表面最短路径示意图。 这个效应的前提是电中性条件,但是ESD电流注入器件后已经破坏了电中性条件,所以在ESD泄放时,基级的电阻率并不均匀。如图三所示,器件表面的电荷浓度要高于器件内部,说明基级表面的电阻率要低于内部,这也是要参照最短路径的原因之一。 3 .Kirk效应 又名基区展宽效应,如图四所示当集电极电压不变,而集电极电流增加时,基区一侧的集电极空间电荷区减薄,中性基区的宽度增大,集电极空间电荷区增大,空间电荷区往集电极移动。  图四.Kirk效应示意图。 ESD防护不同于普通工作情况,Bipolar在进行ESD泄放时,没有外界条件提供静态工作点,所以很难实现集电极电压不变而单纯电流增加的情况,而且大部分ESD Bipolar需要击穿基级-集电极,从而实现ESD泄放,所以很难确定器件在面对ESD时Kirk效应对器件的影响。 4 Johnson limit 因为表面态的存在,针对三极管的集电极-射电极击穿电压与截止频率呈指数衰减关系。如图所示,截止频率越高,击穿电压越低。因为Johnson limit效应,用SiGe工艺实现高频RF电路时,需要注意三极管击穿电压的浮动。  图五.Johnson limit效应示意图。 三.Bipolar的ESD防护应用。 如图六所示为Diode-Configured Bipolar该接法类似于GGNMOS与GDPMOS,区别在于Bipolar是利用器件内部的寄生二极管进行ESD泄放。  图六.Diode-Configured Bipolar示意图。 如图七所示,有时为了避免INPUT过低或者地弹造成ESD器件的误开启,会在基级串联一个分压电阻。  图七.基级耦合电阻Diode-Configured Bipolar示意图。 除了上述应用方法外,还可以在Bipolar的基级连接辅助电路用以构成Trigger Bipolar泄放电路。不过辅助电路需要往基级注入电流,并提供一个偏置电压,使Bipolar进入正向放大区,从而ESD电流可以从射电极流出器件(这里不建议使用RC频率触发电路开启Bipolar)。常见的触发方式有齐纳二极管触发,三极管触发,正偏二极管触发。  图八.Trigger Bipolar和Diode-Configured Bipolar TLP曲线。 如图八所示为Trigger Bipolar还有Diode-Configured Bipolar的TLP曲线对比,其中蓝线为正偏下的Diode-Configured Bipolar,黑线为Trigger Bipolar,红线为反偏下的Diode-Configured Bipolar。从TLP可以看出ESD性能:正偏Diode-Configured Bipolar>Diode-Configured Bipolar>反偏Diode-Configured Bipolar,但是正偏Diode-Configured Bipolar还需要配合Power Clamp使用。  图九.Zener Diode Trigger Bipolar电路示意图。 如图九所示为Zener Diode Trigger Bipolar电路,该电路利用齐纳二极管较低的击穿电压和较好的击穿稳定性。正常工作电压无法击穿齐纳二极管,而当发生ESD时,齐纳二极管发生齐纳击穿,大量电流进入ESD Bipolar基级,同时另一部分电流经过电阻产生分压,为基级提供开启电压。在由Trigger Zener Diode 产生的电压电流共同作用下,三极管进入正向放大区,ESD通过射电极流入GND Rail。  图十.BVCEO Breakdown Voltage Trigger Bipolar示意图。 如图十所示,BVCEO Breakdown Voltage-Trigger Bipolar的工作原理与Zener Diode Trigger Bipolar类似,BVCEO Trigger Bipolar先发生雪崩击穿,产生GND Rail电流,并通过电阻产生电压,使得ESD Bipolar 工作在正向放大区。而因为Johnson limit效应使得反偏击穿电压会受到器件截止频率的影响,可能出现ESD Bipolar比Triggered Bipolar/Diode先行击穿的现象,所以采用如图十一所示的Ultralow Forward-bias Diode Voltage-Trigger Bipolar避免击穿电压不同所带来的风险。  图十一.Ultralow Forward-bias Diode Voltage-Trigger Bipolar示意图。 而二极管的数目与Johnson limit的关系如图十二所示。二极管数目过多,也会存在ESD Bipolar比二极管串先行击穿的风险。  图十二.Johnson limit曲线与正偏二极管数目的关系。 无论是Trigger Bipolar还是Diode-Configured Bipolar其TLP曲线都是非Snap-back型的。还有一种是Snap-back Bipolar,这种三极管发生Snap-back的过程与GGNMOS类似,同样是由载流子导电机制变化引发Snap-back。这种Snap-back Bipolar需要将基级浮空,或者在内部嵌套多层阱结构,其电路结构与TLP曲线如图十三所示。这种Bipolar的Trigger Current比较高。具体原理与Floating WeLL类似,以后会讲。  图十三.Snap-back Bipolar示意图与其TLP曲线。 三极管虽然有诸多优势,但是其性能还是受工艺影响较大,而且太依赖电路隔离性能。目前大部分芯片在设计中可能出于面积、成本、电学参数稳定性等考虑,减少了三极管作为ESD防护器件的使用。笔者也只在较老的工艺上见到过大规模使用三极管进行ESD防护的案例。但是随着第三代半导体的兴起,三极管在片外ESD领域还是能大有所为的。 |