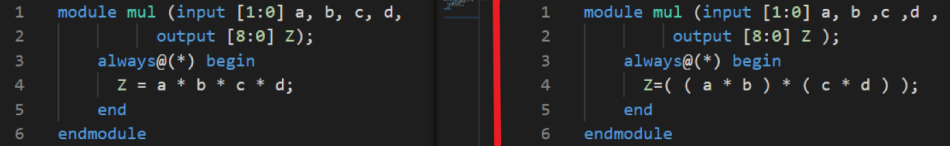

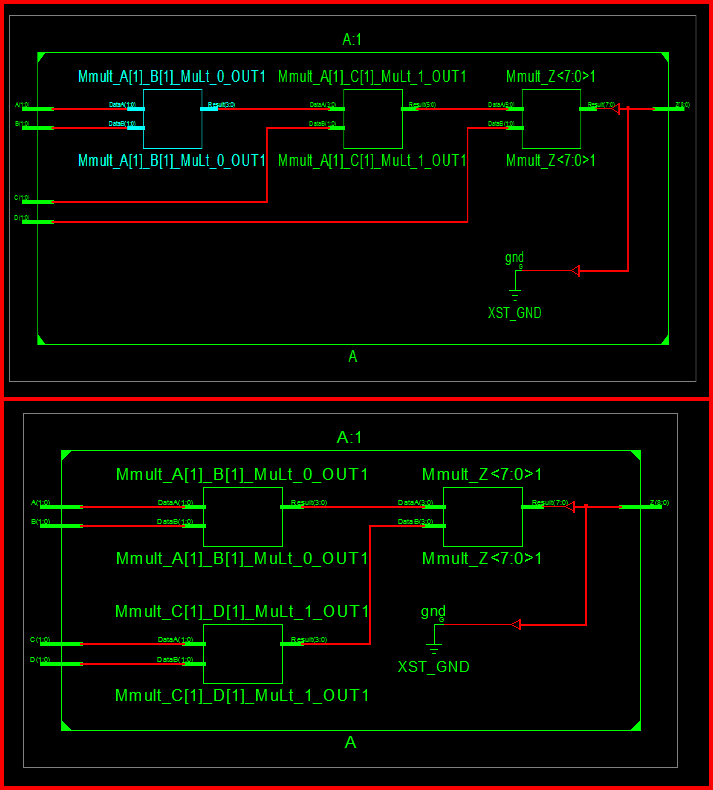

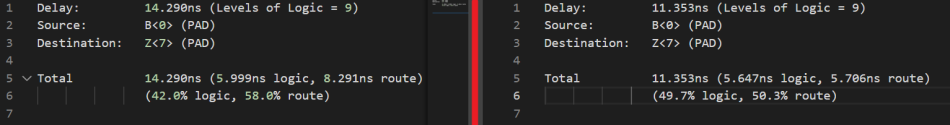

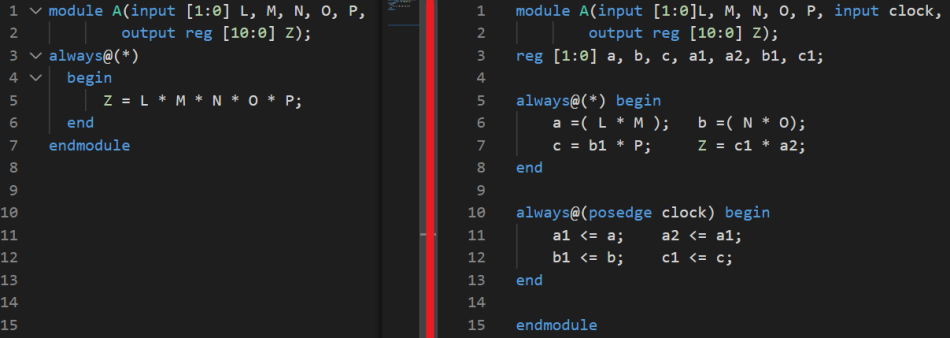

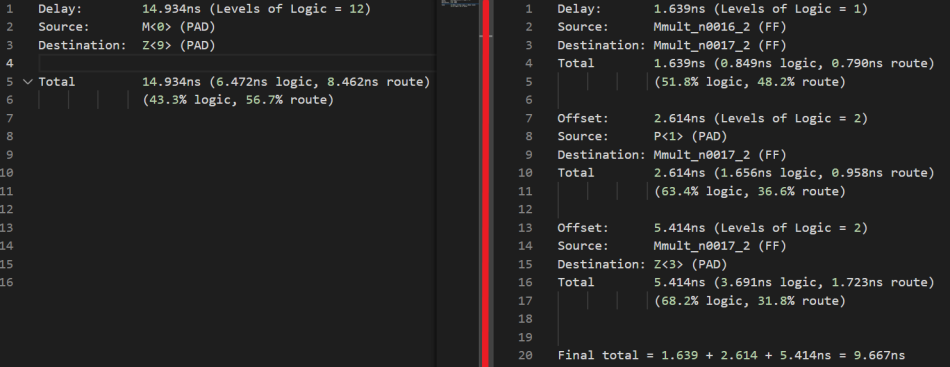

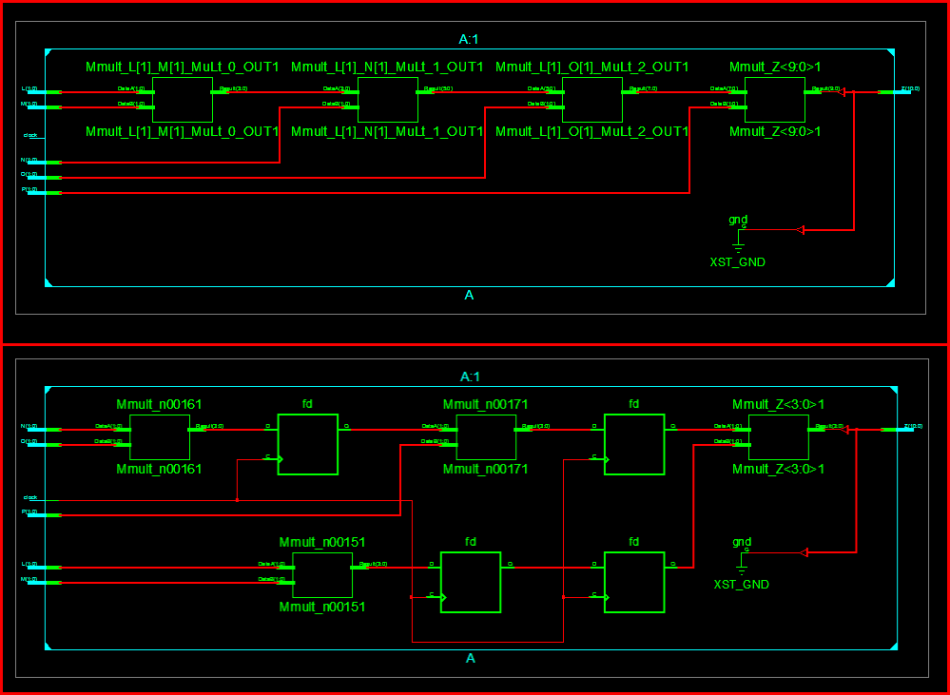

设计人员在开发芯片逻辑之前,需要在许多因素之间作出权衡。例如,如果是为移动应用开发芯片,功耗就是一个非常重要的因素。在这种情况下,需要低功耗逻辑。顾名思义,低功耗逻辑有助于降低功耗,但会影响芯片的性能。同样,如果是为数据中心应用开发芯片,则需要考虑高性能,功耗相对次之。总之,芯片的功耗和性能是成反比的。在为芯片设计编写逻辑时,设计人员需要找到功耗和性能的正确平衡点。如前所述,芯片的高速度对于某些应用来说是必须的。因此,在为此类应用开发逻辑时,有一些方法可以通过少量的逻辑优化来提高设计速度。本文将介绍可以用来提高芯片设计速度的一些技术和窍门。 1.重新格式化逻辑表达式 有时,可以通过改变逻辑代码编写的方式来提高电路的性能。图1就是这样一个例子。尽管两个代码执行相同的功能,但合成器工具以不同的方式综合两个代码,最终会影响到电路的时延。  图1:可以在在代码1(左)和代码2(右)的第4行看到差异。 图1:可以在在代码1(左)和代码2(右)的第4行看到差异。采用Xilinx ISE和Spartan6系列FPGA分析时序性能。  图2:上方是代码1的原理图,下方是代码2的原理图。  图3:代码1(左)和代码2(右)的时延比较。电路2的速度要高于电路1的速度。 结论:图3的时序分析表明,在相同的逻辑条件下,将括号放在右侧得到的总时延可以减少电路时延,从而提高电路的速度。 2. 使用流水线寄存器 另一种提高电路时序性能的方法是使用流水线(管道)寄存器。将长组合逻辑分解为多个单元,并在它们之间添加寄存器。由于数据路径逻辑中增加了寄存器,从输入获得信号到输出产生信号的时间有所增加。但是每个时钟周期计算的结果会相应增加,从而减少电路的总时延。  图4:代码3(左)和代码4(右)具有相同的功能,但代码4采用了流水线寄存器,而代码3则没有。  图5:在代码3(左)和代码4(右)的时延比较中可以发现,电路4的速度要高于电路3的速度。  图6:顶部是代码3的原理图,底部是代码4的原理图,后者包含了流水线寄存器。 结论:从图5可以明显看出,带流水线寄存器的电路的速度远高于不带流水线寄存器的电路速度。流水线增加了时延和面积,但也提高了工作频率。因此,当性能是标准时,流水线方案应该是首选。 3. 将慢速信号放在数据路径逻辑的末尾 解决长路径问题的另一种方法是将最慢的信号放在逻辑的后端。例如,Z=A&B&C&D可以重新排列为Z=(A&C&D)&B。这可确保信号B在综合完成时仍然在逻辑后端,从而有助于减小逻辑的整体时延。 4. 高层次编写代码 在设计中将加法器和乘法器等算术运算留给综合工具来实现通常是一个好主意。在较低层次进行设计,可能会导致时序问题,因此应尽可能将其留给综合器。 在高层次编写RTL代码时,可以使用Synopsys DC并在DesignWare库的帮助下实现加法器、时钟域交叉单元、乘法器和时钟门控单元等常见逻辑块。同时应注意编写能让合成器容易理解的RTL代码。这样可以产生高质量的网表。在设计中使用状态机,并实现良好的层次结构,将会得到更好的综合结果。 5. 执行综合时放松面积约束 减少面积约束,将有利于综合器工具在提供的库信息中查找除标准VT(SVT)单元之外的不同单元。更快的单元(LVT)有助于减少逻辑时延,但会增加面积和功耗。在综合过程中适当增加编译器的工作量将允许综合工具在生成网表之前尝试不同的组合和替代。唯一的缺点是它增加了编译时间。 6. 在严格的时序约束下执行综合 为了确保综合工具能够更加尽力地优化长数据路径,整个综合是在比目标周期时间更短的时间内完成的。由于要到布局和布线后才会有金属电容,因此综合后获得的时序分析只是一个估计值。在较短的时钟周期时间执行综合,会抵消后续的后端处理中出现的金属电容和其他寄生参数。 遵循以上这些方法将有助于减少设计中的时延,从而使设计能够实现更高的运行频率。 |