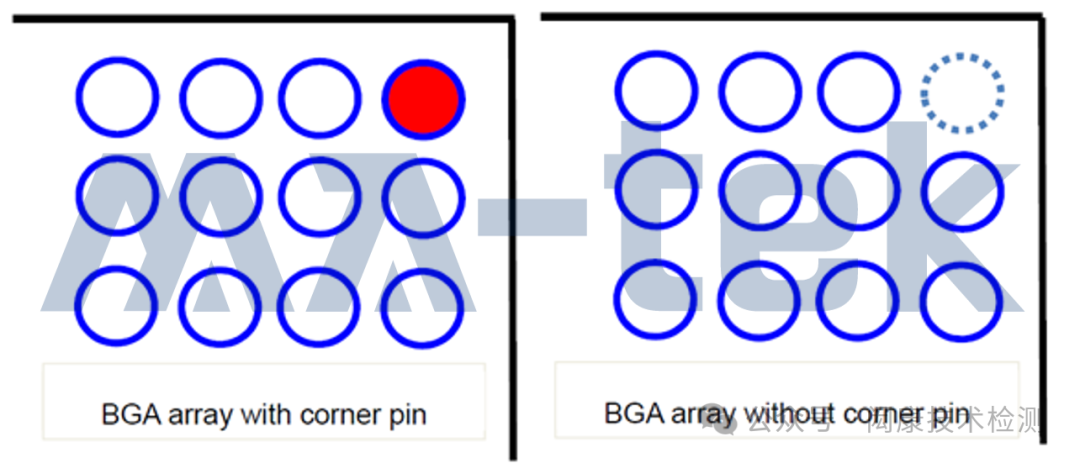

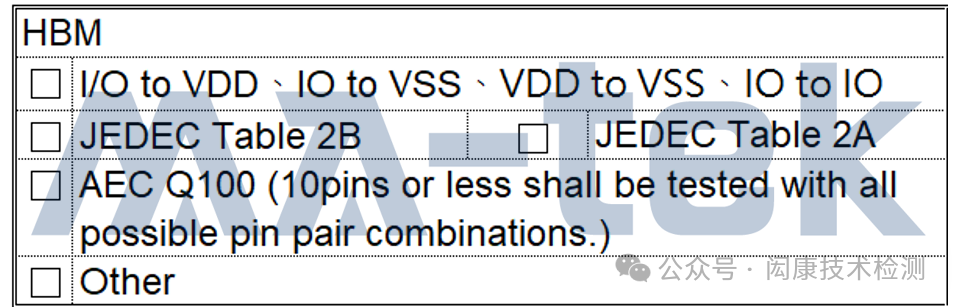

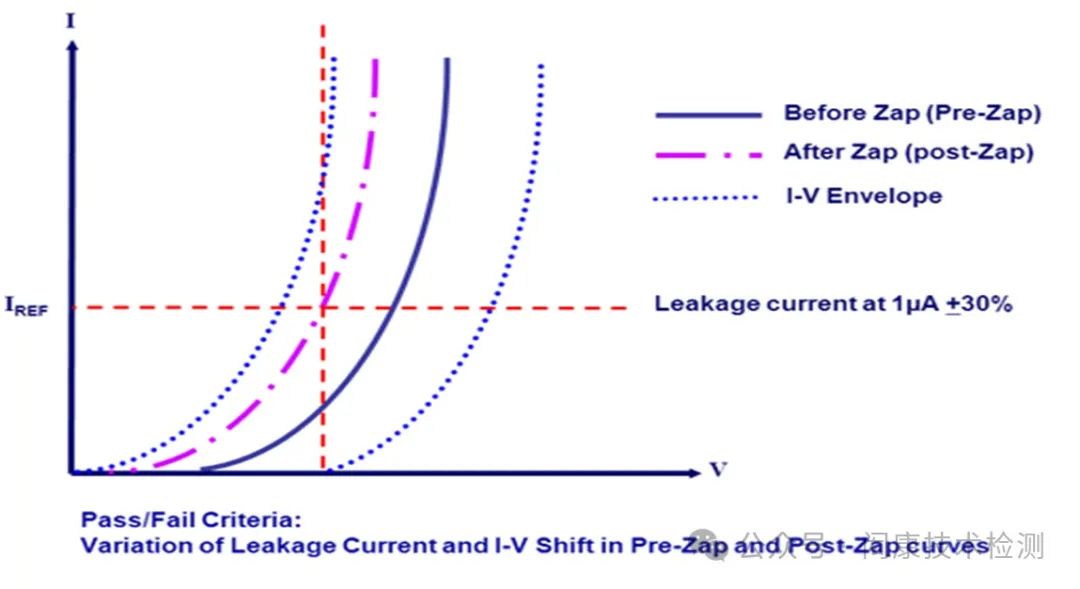

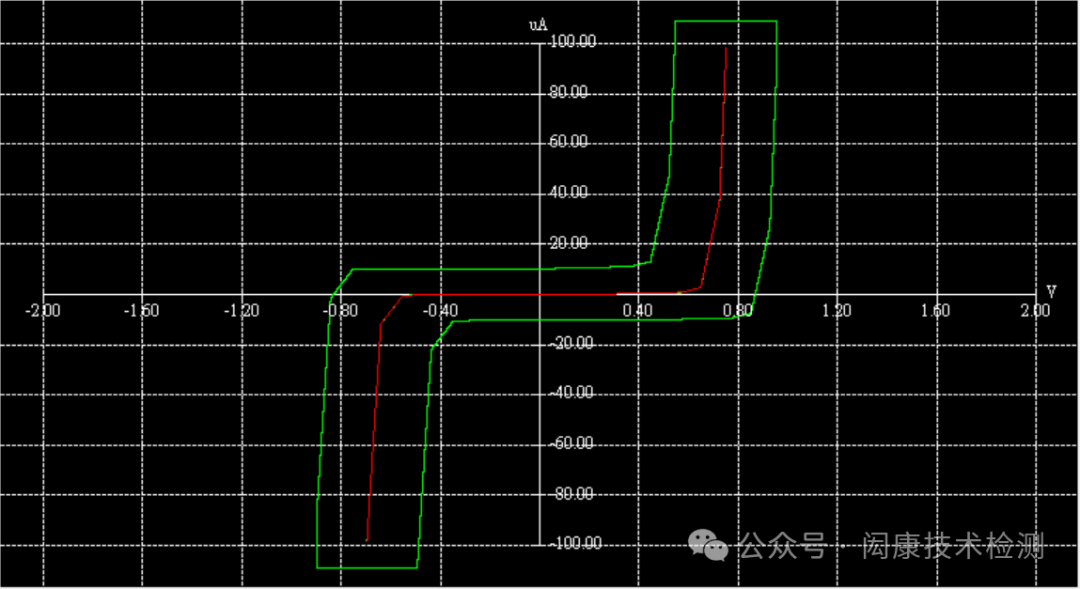

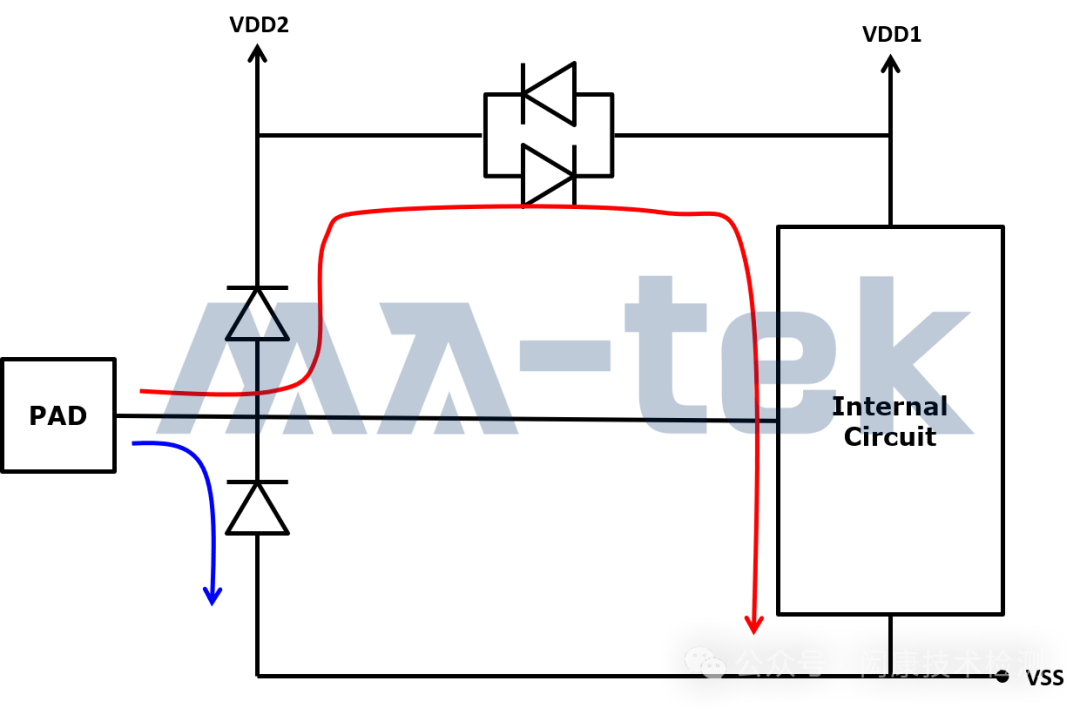

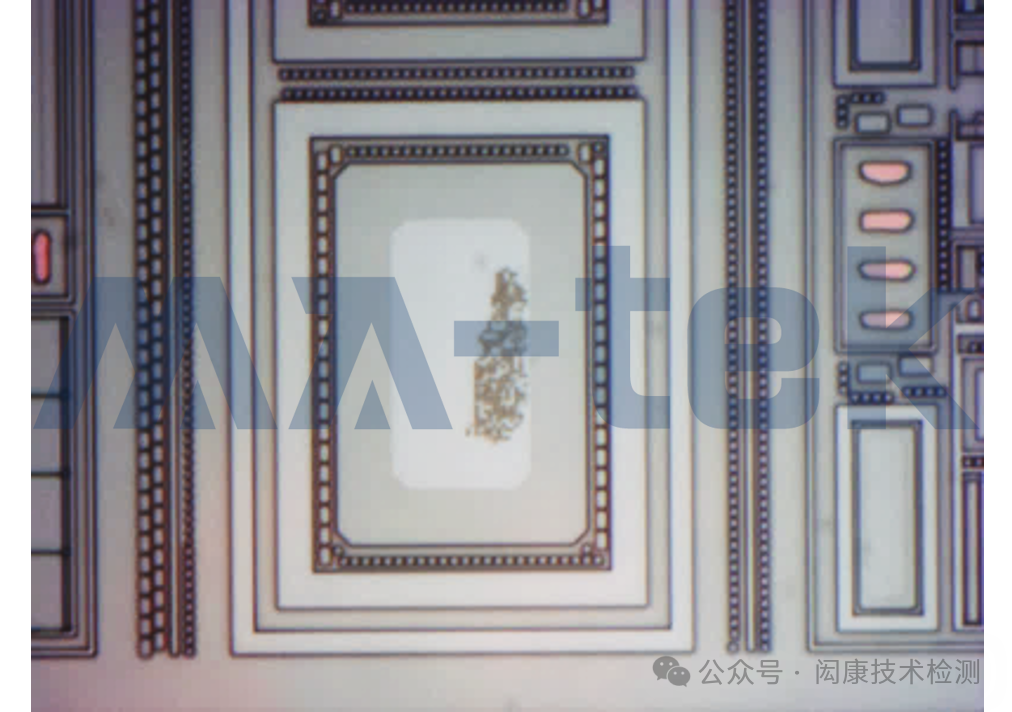

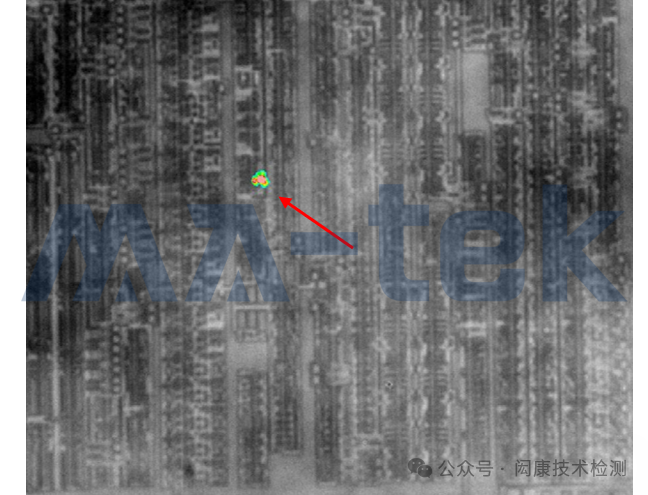

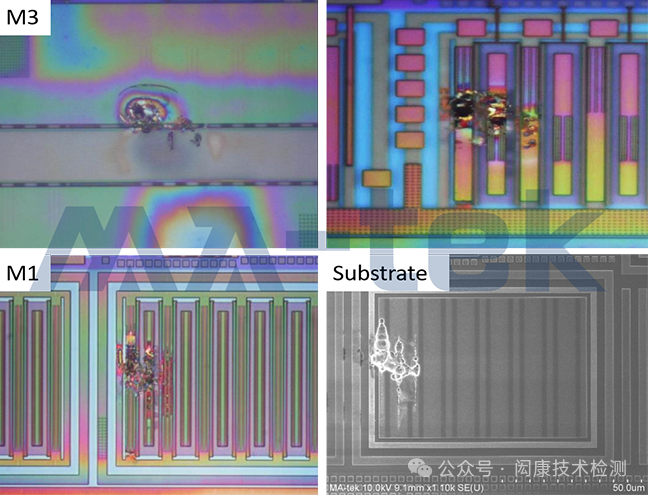

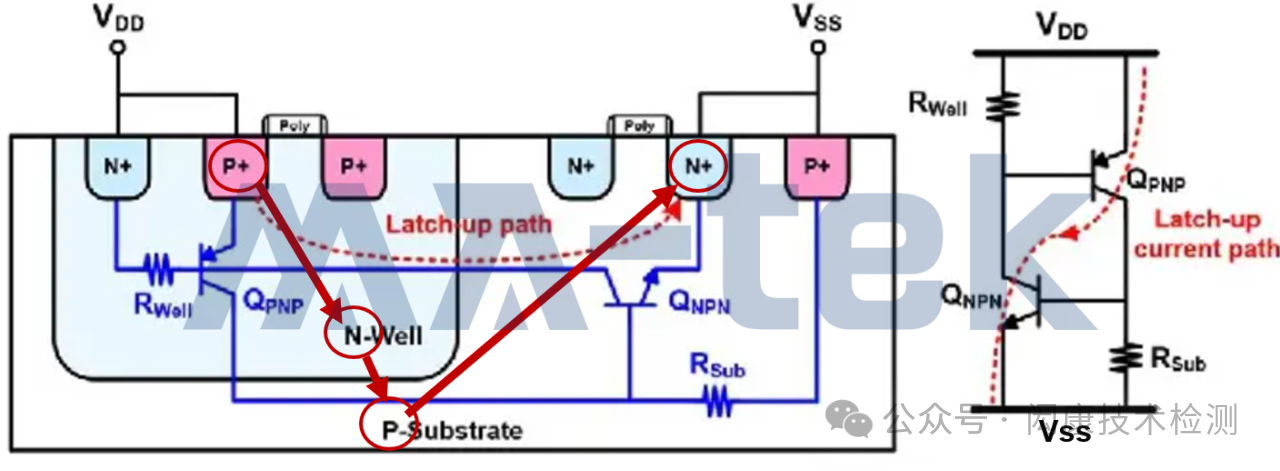

任何产品都有其使用期限,或者我们可以说这个产品的可靠性好不好,若可以使用好几年,直到下个世代的产品出来都不会损坏,那可以说这个产品有不错的可靠性,反之使用的时间达不到这个产品应具有的水平的话,可靠性就不佳了,那么如何去度量产品的可靠性好不好呢? 基本上就会考虑使用环境的条件,如电压、温度、湿度或任何环境下不利的因子,代入失效模型,便可估算出使用的年限。在我们所身处的环境中,静电是无所不在的杀手,既然静电无法完全预防,那么为了能够在电荷流经集成电路时全身而退,IC设计上就会在引脚旁设计静电放电(Electrostatic Discharge, ESD) 防护电路保护芯片,就像在大楼顶端设置避雷针的目的一样,当一道雷打在大楼上时,能够有引流的作用,确保大楼内的电器不会受损。另外由于元件结构的特性,所谓的闩锁 (Latch-up, LU) 效应会造成集成电路在操作时有大电流的现象而引起功能上的问题,甚至会使得芯片永久损伤,同样地,也需要在芯片设计上来避免 LU 的问题。 为了验证ESD与LU的防护能力,第一道课题就是如何运用专门的测试机台,遵循国际规范定义的条件与步骤,确认集成电路在 ESD 与 LU 的可靠性。若该电路元件无法通过 ESD 与 LU 测试,且已找出验证不过的原因之后,如何进行芯片设计上的补强成为第二道课题。本篇文章即是针对此两个课题阐述 ESD 与 LU 在测试前的准备事项、判断标准、以及元件失效后的问题真因解析流程。 测试前资料准备 进行 ESD 与 LU 测试前,一般会遇到的问题是该如何规划测试方案与执行,该如何与测试项目主管沟通测试方案,为提升双方沟通效率,可以依下述几项主题提供信息。 测试规范 在进行测试前,需先设定遵循的国际标准规范,规范的制定有其立论基础,因此ESD/LU测试验证通过即代表获得了客户的信任与使用上的保证。以下即是不同测试项目与其对应的国际标准规范。 1. HBM: · MIL-STD: 元件类和部分驱动 IC · AEC-Q100 或 AEC-Q101: 车规认证 · JEDEC: 其余皆使用消费型产品规范 2. CDM: ANSI/ESD SP5.3.2 : 此为 SCDM 测试规范,目前只有少数驱动IC的客户,且指定才会测试 SCDM。 AEC-Q100 或 AEC-Q101 : 车规认证 JEDEC : 旧规范 JESD22-C101F 和新规范 JS-002-2022 ,绝大部分产品是使用消费型产品的 JEDEC ,且建议客户遵循最新的 JS-002-2022。 3. LU: JESD78F : 消费型产品 AEC-Q100 : 车规认证 测试条件 HBM: 建议从500V执行,依序1KV, 2KV, 4KV, 8KV。 CDM: JEDEC的安全标准是500V,AEC-Q100另外会多增加 Corner Pins 的标准到750V(图一),电压测试级距则建议依序 250V, 500V , 750V 到 1000V 。 LU: 基本上依据规范只需要做到讯号脚位 +100mA / -100mA ,电源脚位做 1.5*VDDmax ,业界习惯会多往上一个级距,会测试到 200mA。此外还需提供额定电压与极限值以为操作条件之设定。  图一 BGA 封装脚位的 Corner Pin 示意图。左图是有 Coner Pin 设计者,其位置在红色圈圈处,此脚位的 CDM 测试标准需达750V。而右图则是无 Coner Pin 设计者。 测试颗数 HBM /CDM / LU : 依据规范建议每个测试条件数据皆要 3 个样品。 IC Package Outline Drawing (POD) 需提供测试脚位的名称、脚位类型 (Input / Output / IO / Power / GND) 与排列位置,以方便评估分析时间与条件设定,也是制作测试治具的依据。 HBM 测试组合 在选择 MIL-STD 规范时,表一第一列的四种测试组合皆可以选择,在此规范下,各 Power Domain的Power/Ground可并接在一起。在选择 JEDEC 规范时有Table 2A or 2B选择,相同 Power Domain 的 Power/Ground 彼此可并接,但不同 Power Domain的Power/Ground间是不互接的,在此基础下,所有的IO脚位对不同的 Power Domain 打 ESD,此为 Table 2B,而 IO 脚位仅对自己所属的 Power/Ground 打 ESD 则为 Table 2A。若要使用最严谨的测试条件、不清楚应使用哪种测试组合或车规验证时,建议使用 Table 2B。至于车规 AEC-Q100的认证,若是封装脚位数小于等于 6 个的话,那么任何 2 根脚位间的排列组合皆需验证。  表一 第一列为 IO 与 Power/Ground 间的测试组合,第二列与第三列为欲采用的规范。 LU特殊测试要求 LU 的测试目的是为了观察是否会有异常的讯号干扰导致激发出大电流的现象,因此在考虑设定的测试条件与环境下实际会发生的状况后,一些客户会选定某些条件进行 LU 测试,如下所述。 高温测试 在高温下由于漏电升高,易触发寄生硅控整流器(Silicon Controlled Rectifier, SCR)启动而产生 LU 效应,故可选择常温或高温(视产品规格的最大操作温度或者 Tj 温度而定) 两种测试环境,AEC 规范则是强制高温测试。 Quiescent Current 高性能运算(High Performance Computing, HPC) IC 具有较高的 Quiescent Current,随着此类 IC 市占率逐渐提高,LU 测试机台已不能满足高电流的要求,需另外订制 High Current LU 治具与外接高功率量测仪器。 Pattern 一般 IC LU 测试是静态测试,即输入的电压与电流是定值,但实际 IC 操作是动态的,输入输出脚位有高低电压周期性的变动,因此 LU测试下输入Pattern是为了模拟在 IC 动态输入下 LU 真实的作动行为。 测试Pass/Fail判断标准 HBM 与 CDM 依据规范是要测试完整的测试项,包含参数测试 (Parametric Testing) 和功能性测试 (Functional Testing),如此才能逮到因 ESD 损伤而造成的故障现象。在参数测试方面,在自动测试机台(ATE)上即是测 Open/Short(OS)、漏电和Power端的静态电流,但若以ESD测试机台来实时地比较 ESD 测试前后的差异的话,可以用两种方式来量测,第一种是在电流等于1uA时的电压,若前后差异小于 30% 便是通过 ESD 测试,如图二所示,第二种是包络线 (Curve Compare Envelope),以 ESD 测试之前的 IV 曲线为参考,并以测试的最大电压与电流的正负 10% 为调整值,将此正负值加诸在测试前的 IV Curve 即可得出一个区间范围,只要测试后的 IV 在此范围便是通过 ESD 验证,如图三所示。  图二 Zap前后的IV变化,若1uA下的电压变化达30%以上,判定此脚位ESD Fail  图三 包络线的示意图,Zap 后的 IV 曲线若超过绿线框选的范围,判定此脚位 ESD Fail LU的 Pass 判断标准是量测前的电流如果是 INOM,则 1.4xINOM 与 INOM+10mA 取其最大值,小于此值即为验证通过。 ESD验证失败的解析与解决方案 依 ESD 失效原理与经验,当静电放电产生的过电流或过电压超过元件的忍受能力时,就会产生元件烧毁的现象,元件烧毁的形态依放电路径决定,如Junction漏电、Gate Oxide Breakdown、Drain与Source间的击穿或两个不同元件间的击穿等等,元件烧毁严重者会往上向金属层延伸。由于是元件烧毁,基本上很适合以 Photon Emission Microscopy(PEM, 俗称 EMMI) 定位出烧毁位置,而 OBIRCH 由于其检测阻值变化的能力,若需进一步确认烧毁位置,也是可以考虑的定位工具。 静电放电烧毁的位置依所发生的电路一般可分为两类,ESD 电路(IO Cell)与內部电路。如图四所示,IO Cell 烧毁可以理解成 ESD 电路发挥了导流的作用,避免静电击伤内部电路,但过电流超过了 ESD 电路的忍受值而有烧毁的现象,这类的烧毁由于对应到参数测试有异常的 Pin 脚,故寻找烧毁位置上相对来说是较简单的。 依全晶面防护的理论,当静电放电不循期望导通的 IO Cell,而延着其它最快速最脆弱的路径时,便有可能击伤内部电路,此时便一定需要定位工具找出烧毁元件,才能了解放电路径做进一步的设计防堵。 总结以上简述,要确认烧毁元件或电路,有下述几个选择 1. 若是已知毁损电路在 IO Cell,为了快速确认,可以执行全层次去除(Total Delayer)后,再以光学显微镜(OM)或扫描式电子显微镜(SEM)观察,如图五所示。 2. 以亮点定位工具,EMMI 或 OBIRCH 找出亮点位置所在的元件,在一些情况下,IC设计研发工程师能依据亮点对应的元件推导出 ESD 失效模型,进而做出设计改良,如图六所示。 3. 承上,为验证精确的失效机制,可以逐层将金属层去除直到最底层的 Contact / Poly / AA 露出,观察烧毁的现象,甚至有时需以特别的样品制备方式确认 Gate Oxide Pinhole,特别是 CDM 失效的实验,如图七所示。  图四 ESD 击伤内部电路的路径  图五 典型在 IO Cell 的 ESD 损伤  图六 以晶背 EMMI 侦测方式发现 ESD 失效的亮点在逻辑电路上  图七 逐层 Delayer 观察 ESD 电路烧毁的情形 以上 ESD 失效分析流程中很重要的目的是要确认放电路径,在此要求下,建议以平面观察 (Plan View) 的方式找出损伤的痕迹,如此才能建立静电放电失效的模型,并提出疏浚或节流的对策,若是疏浚,就是设计其它的导通路径,比如更多的 Contact 来减少电流密度(Current Density),若是节流,可以设计限流的电阻以避免过多的电流造成烧毁的结果。 LU验证失败的解析与解决方案 LU 的产生是因为外界的干扰讯号触发了寄生 SCR 元件,过大的电流造成功能性的问题,因此 LU 解析的第一步就是确认寄生SCR元件在哪里。当 LU 发生时,过大的电流有可能造成芯片严重的烧毁,烧毁的位置虽可经由电性定位工具轻易地找出,但要注意的是烧毁的位置是大电流经过的路径,并不一定是寄生 SCR 元件所在,故碰到烧毁的现象反而不容易找到真因。 SCR 作动时,EMMI 可以侦测元件作动时发出的光,所以若 LU 现象造成的大电流没有损伤芯片,可以在设定触发 LU 的条件下执行 EMMI 的定位,便可找出寄生 SCR 元件的位置,进一步,在其相对应的 Layout 位置上确认 p-n-p-n 的结构,将此结构绘出寄生 SCR 结构图,之后再从 LU 产生的原理去理解是什么效应触发了 LU 现象,是某处的片电阻(Sheet Resistance)过高,亦或是某处节点有浮接(Floating)的情形等等,推理出失效模型后,LU 的问题即可迎刃而解,其道理可参考图八。  图八 CMOS结构上需找出p-n-p-n的连续性结构,并对应到SCR电路 在产品的研发阶段,ESD 与 LU 测试与分析是不可或缺的一环,依循本篇文章的验证流程,可以快速的解决认证方面的问题,若有其它特殊状况,也欢迎联络闳康的专业团队做更深入的解析。 |