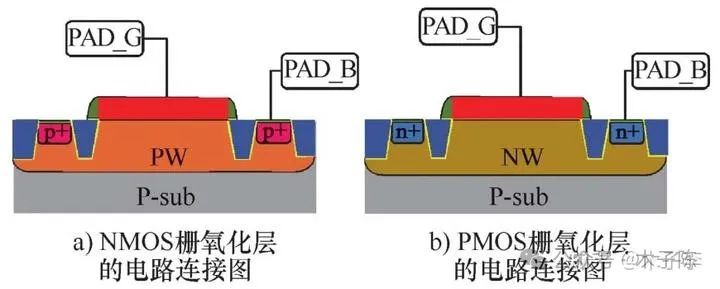

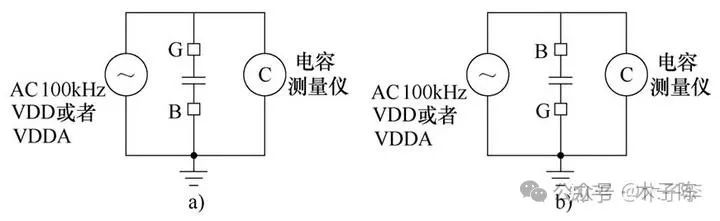

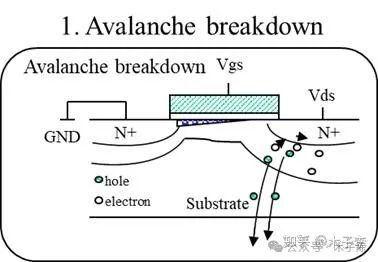

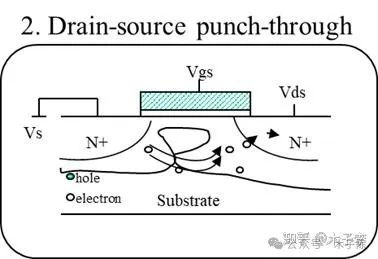

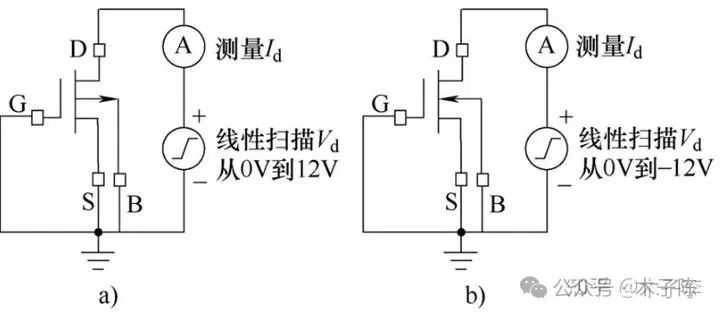

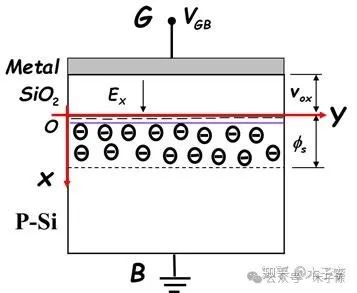

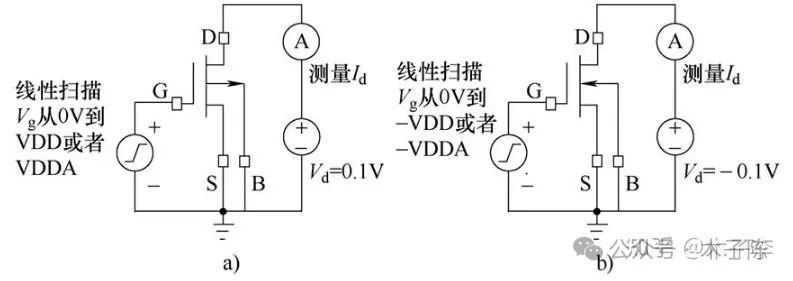

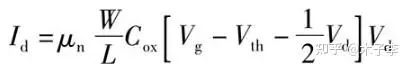

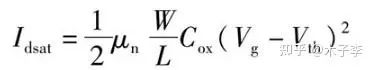

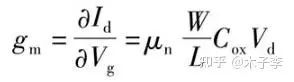

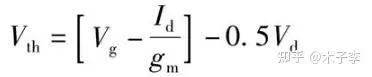

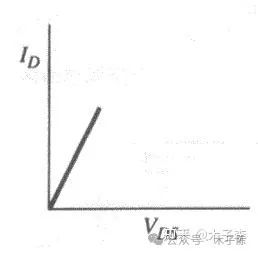

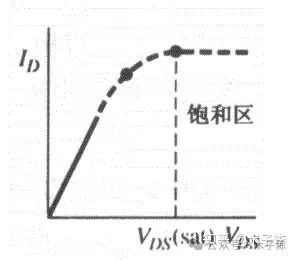

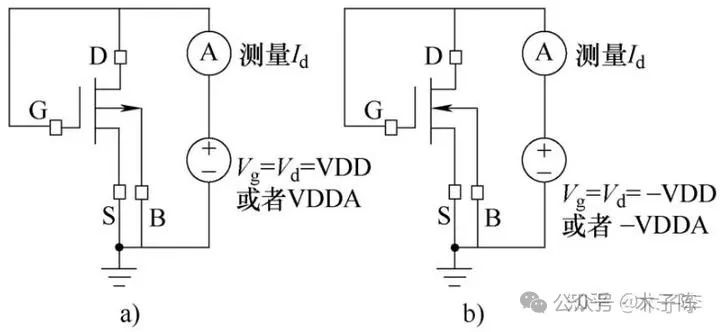

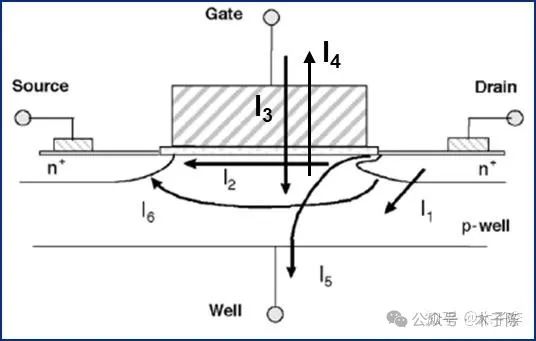

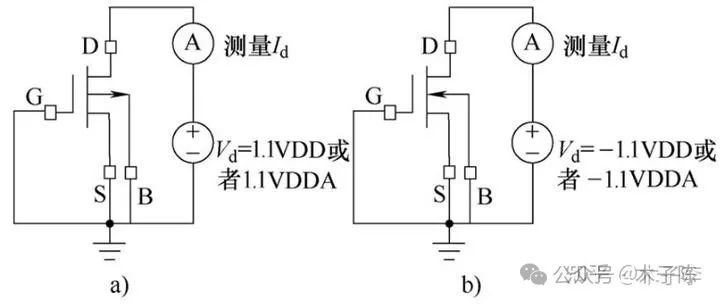

这篇文章我们来介绍一下芯片中的CMOS的关键参数是怎么测试的,首先是MOS的栅极氧化层的测试。MOS晶体管栅氧化层完整性(GOI)的测试结构是多晶硅栅-氧化层-PW衬底(NMOS栅氧化层)和多晶硅栅-氧化层-NW衬底(PMOS栅氧化层)的电容结构,其电路连接如图所示:  两个端口栅(Gate)和衬底(Body)分别连到PAD_G和PAD_B,WAT测试机器通过这两个端口把电压激励信号加载在这个电容结构的两端,从而测得所需的电性特性参数数据。 栅氧化层在整个工艺流程里是非常关键,它的质量直接影响的MOS晶体管的电性特性,所以利用NMOS栅氧化层和PMOS栅氧化层的参数栅氧化层的电容(Cgox)、栅氧化层的厚度(Tgox)和栅氧化层的击穿电压(BVgox)检测它。 · 1.栅氧化层的电容(Cgox) 基本原理:在电容的一端加载AC 100kHz扫描电压,另一端接地,从而测得电容C,Cgox=C/Area,Area是电容的面积。 NMOS栅氧化层电容Cgox的基本方法是首先在栅电容的一端多晶硅栅上加载100kHz(VDD或者VDDA)扫描电压,另一端PW衬底接地,来测试电容C,Cgox=C/Area。 PMOS栅氧化层电容Cgox的基本方法是首先在栅电容的一端NW衬底上加载100kHz(VDD或者VDDA)扫描电压,另一端多晶硅栅上接地,来测试电容C,Cgox=C/Area。  · 电性厚度Tgox 测量栅氧化层电性厚度Tgox的基本原理是在电容的一端加载AC 100kHz扫描电压,另一端接地,从而测得电容C,利用公式Tgox=(εoεoxArea)/C,εo=3.9,εox=8.85418,求得电性厚度Tgox。实际上栅氧化层电性厚度Tgox是在栅氧化层电容C的基础上进行计算得到的。 · 击穿电压BVgox 栅氧化层电容的介质是SiO2。由于SiO2是绝缘体,在一般情况下是不导电的。但是当有一个外加电场存在时,随着外加电场的不断增大,当外加电场强度所提供的能量足以把一部分价带的电子激发到导带时,这时二氧化硅不再表现为绝缘性质,而是开始导电,这时所加的外加电压的值就是所测试的电容击穿电压值。 测量栅氧化层电容的击穿电压BVgox的基本原理是在电容的一端加载反向电压,另一端接地,从而测得栅漏电流Ig或者衬底漏电流Ib,得到单位面积电流强度Ig/Area或者Ib/Area,当漏电流强度达到100pA/μm2时,认为电容被电压击穿。此时加载在电容两端的电压就是击穿电压。 影响栅氧化层的因素包括以下几方面:1)阱离子注入异常;2)离子注入损伤在退火过程中没有激活;3)栅氧化层的厚度异常。 源漏击穿电压BVD 击穿的方式分为Avalance breakdown 和 Drain-source punch-through.   · 短沟道Short Channel:一般情况会发生S/D punch through · 长沟道Long Channel:一般情况会发生Drain to body PN junction breakdown 根据发生BV时,Drain端电流Id与Is、Ib的关系判断breakdown 的来源: Id≈Is时,S/D punch through Id≈Ib时,Drain to body PN junction breakdown 测量MOS晶体管击穿电压的基本原理:在晶体管的四端分别加载电压,栅极与衬底没有形成压差,衬底没有形成反型层,此时的晶体管处于截止状态,漏极加载的电压不断增大,量测沟道中漏电流。当漏极上电压还没有达到击穿电压时,源和漏之间的电流是非常小的,当电压达到击穿电压时,源和漏之间的电流会突然增大,达到微安级甚至更高。此时加载在漏极的电压就是击穿电压。  NMOS击穿电压BVD基本方法是首先设定Vg=Vs=Vb=0V,然后线性扫描Vd从0V到12V,得到Vd在Id/W=0.1μA/μm时的值,该点的电压值就是击穿电压BVD。 PMOS击穿电压BVD基本方法是首先设定Vg=Vs=Vb=0V,然后线性扫描Vd从0V到-12V,得到Vd在Id/W=0.1μA/μm时的值,该点的电压值就是击穿电压BVD。 影响晶体管击穿电压的因素包括以下几方面: 1)阱离子注入异常; 2)LDD离子注入异常; 3)离子注入损伤在退火过程中没有激活; 4)多晶硅栅刻蚀后的尺寸异常; 5)接触孔刻蚀异常。 影响BVD的因素: 1. S/D implant (N/P Plus) 2. Well implant 3. CT ETCH 4. Co-Loop 5. AA/STI structure 6. Small Defect 7. Thermal budget 根据上面的介绍,相信大家对MOS的测试项目有了具体的了解,下面我会具体介绍一下每个测试项目的测试条件及原理,首先,当然是MOS管最重要的参数,阈值电压Vt。 · 从半导体物理的角度来理解阈值电压,阈值电压是指达到阈值反型点时所需的栅压。  测量原理:在晶体管的四端分别加载电压,S,D之间存在一定电压差,G和B之间也存在一定电压差,使衬底沟道形成反型层在源和漏之间形成通路,源和漏之间产生电流的过程。 测量方法:第一种方式是利用最大电导的原理测量;第二种方式是利用电流常数测量。 1.定电流法测量Vtlin,Vtsat; 这里介绍定电流法测试,其基本原理是认为当Id/W=0.1μA/μm时,晶体管开启导通,此时的栅极电压就是晶体管的阈值电压。  图a 为测量nmos的Vtlin, 其参数设定方法为:Vd=0.1V和Vs=Vb=0V,然后线性扫描Vg从0V到VDD或者VDDA,测得Vg在Id/W=0.1μA/μm时的值,那么Vtlin=Vg。 图b为测量pmos的Vtlin, 其参数设定方法为:Vd=-0.1V和Vs=Vb=0V,然后线性扫描Vg 从0V到-VDD或者-VDDA,测得Vg在Id=-0.1μA*(W/L)时的值,那么Vtlin=Vg。 影响晶体管阈值电压的因素包括以下几方面: 1)阱离子注入异常;. VT implant ,LDD implant,S/D implant (N/P Plus) 2)离子注入损伤在退火过程中没有激活;Thermal budget 3)AA或多晶硅栅刻蚀后的尺寸异常;Poly in-Line AEI CD 或者AA in-Line AEI CD 4)栅氧化层的厚度异常。Gate OX thickness/quality。 2.Vtgm的测量: Vtgm是线性区最大跨导法下的开启电压。 · 最大跨导法测量的基本原理是当Id=Idsat时,是最大跨导gm,其中线性区电流计算公式是:  饱和区电流的计算公式是:  根据条件Id=Idsat, 整理可得Vd=Vg-Vth, 利用线性区电流计算公式对Vg求导可得,即Id-Vg 曲线的斜率:  并将上式带回整理可得  gm的物理意义是随着Vg的不断增大,载流子在沟道中受到晶格散射的概率不断增大,载流子的迁移率不断下降,gm的最大值会发生在饱和区和线性区的交界处,此时Vg=Vd+Vth。 · 测量方法: 针对NMOS来说,首先设定Vd=0.1V和Vs=Vb=0V,然后线性扫描Vg从0V到VDD或者VDDA(VDD为低压器件的最大工作电压,VDDA为中压器件的最大工作电压。),测得最大电导时Vg的值,求该点的斜率,通过该点利用斜率作斜线相交于x轴得到数值Vg(x),那么Vt=Vg(x)-0.5Vd。  介绍完Vt ,下面要介绍电流系数,Idlin和Idsat,Ioff。 对于线性区来说,Idlin电流如图所示,  呈现这样IV曲线的原因是线性工作状态下,MOS管可以等效为电阻,其测试方法为Vb=Vs=0V,Vd=0.05V,Vg从-0.5V变化到VDD,测得Idlin。 对于饱和区来说,Idsat电流示意图如图:  测量MOS晶体管饱和电流的基本原理是在晶体管的四端分别加载电压,栅极加载最大电压使衬底沟道形成反型层在源和漏之间形成通路,漏极加载最大电压使沟道夹断,晶体管工作在饱和区,沟道中电流达到最大值。此时测得的电流是饱和电流,除以沟道宽度得到单位宽度的电流。 NMOS基本测试方法为先设定Vd=Vg=VDD或者VDDA,Vs=Vb=0V,测量电流Id,那么Idsat=Id/W。 PMOS基本方法是首先设定Vd=Vg=-VDD或者-VDDA,Vs=Vb=0V,测量电流Id,那么Idsat=Id/W。  影响Id的主要因素有: 1)阱离子注入异常; 2)n+或者p+离子注入异常; 3)LDD离子注入异常; 4)离子注入损伤在退火过程中没有激活; 5)AA或多晶硅栅刻蚀后的尺寸异常;Poly in-Line AEI CD ,AA in-Line AEI CD 。 6)栅氧化层的厚度异常。Gate OX thickness/quality。 除了上述两种,还有Ioff,漏电流也是器件性能中关心的。  漏电流主要由以上6部分组成: · I1: S/D IMP和Well的PN结反偏的漏电 · I2:S/D亚阈值漏电 · I3:Gate poly 隧穿 · I4:热载流子注入 · I5:GIDL,栅感应漏极漏电流 · I6: Punch Through ,S/D源漏穿通,需要避免。 测量方法: 测量MOS晶体管漏电流的基本原理是在晶体管的四端分别加载电压,栅极和衬底之间没有电压差,衬底没有形成反型层,晶体管工作在截止区,漏极加载1.1倍最大电压,量测沟道中的漏电流。此时测得的电流是漏电流,除以沟道宽度得到单位宽度的电流。 NMOS测量方法:设定Vd=1.1VDD或者1.1VDDA,Vg=Vs=Vb=0V,测量电流Id,那么Ioff=Id/W。 PMOS测量方法:设定Vd=-1.1VDD或者-1.1VDDA,Vg=Vs=Vb=0V,测量电流Id,那么Ioff=Id/W。  影响漏电流的因素: 1)阱离子注入异常; 2)LDD离子注入异常; 3)接触孔刻蚀异常。 |