|

一直都没有机会聊具体的测试技术,今天就开始聊一下.介绍下高速数字信号管脚的常用测试方法 目前越来越多的SOC芯片都会有高速的数字信号管脚,常见的如LVDS,HDMI以及PCIe等信号管脚.这些信号的速度通常在500Mbps到5.0Gbps的级别,一般的测试机的数字通道往往达不到这样的速度.这就需要寻找专门的方法来对应

最直接的办法当然是选用更高端的测试机台.目前高端的测试设备(例如爱德万的A93000)都有高速的数字通道测试模块,最高的速率可以达到3.6Gbps甚至更高到12Gbps.这些模块的功能非常齐全,可以覆盖一般高速信号的测试需求,甚至眼图也可以抓取.而且测试精度和稳定性都有比较高的保障.可以这一方法最大的缺点就是成本太高.为实现这么一个测试需求,测试机的整个档次就必须上一大截,成本提高很多.这对于很多消费类的产品来说有点杀鸡用牛刀的感觉.很多消费类的HDMI或LVDS信号端口在实际应用中对于眼图等性能要求并不严格,不需要如此苛刻的测试.相对而言,节约测试成本才是更重要的目标

所以很多的芯片公司往往会采用on-board的测试方案,就是在测试载板上预制测试电路,用一个对应的功能芯片发送或采集高速信号,或者可以用一个带有高速信号端口的FPGA来实现和被测芯片的数据交互.这样一来,高速信号通过专用电路转换为低速并行信号再传给测试机,或者信号直接由外围电路进行判断,将判断结果反馈给测试机.采用这种方法的公司很多,甚至泰瑞达和蔚华这样的专业测试机供应商也推出过通用的基于FPGA的供中低端测试平台用的高速信号的测试电路方案.不过这种方法有一些比较大的缺点,就是比较难于定量测试信号的质量,而且电路本身的稳定性比较差,对良率可能产生些许影响

有的公司会采用降速的方法,就是把端口的速度降到测试机能够达到的速率,这样就可以实现部分功能的测试.但这方法的最大缺陷就是由于不是实际速度的测试,芯片测试覆盖率不足,芯片实际能否跑到需求的速度仍然是未知的.针对高速的TX(输出)信号,其实有一种折中的办法可以实现实时测试.比如,信号实际输出是800Mbps,而测试机的最高采样速率是400Mbps的话,测试向量可以跑两次,一次只测单数周期的输出数据,另一次只测双数周期的.通过这办法就可以实现低采样速率测试机测试高速信号的目的.唯一可惜的是,这方法只适用于TX端口测试,对于RX(输入)端口则无能为力

对于很多同时有TX和RX端口的芯片,目前比较流行的一种方法是环回(loopback)测试.就是在PCB板上直接把TX和RX端口连接起来,采用数据自发自收的方式来进行测试.然后,由于信号自连,测试机无法驱动和观测到相应的端口,就会导致两个问题:1)缺少手段调试和分析问题,特别是在芯片出了问题的时候;2)无法作任何定量的测试,信号性能冗余度(margin)的测试无法进行.

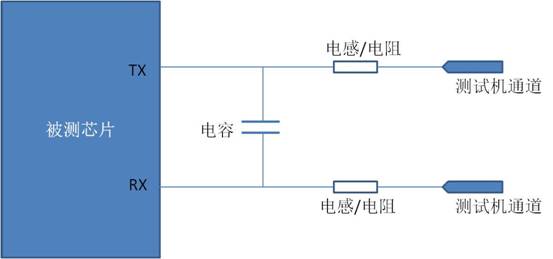

针对以上的问题,目前比较流行的方法是采用一种升级的环回测试法.具体电路连接可参考下图:

当需要测试端口的连接性的时候,测试机的通道可以直接实现各种DC测试.对于DC信号,电路里的电容表现为开路,电感则表现为短路,不会给DC测试带来任何障碍.而当需要进行高速信号环回测试的时候,电容对于高速信号表现为短路,电感则表现为短路.则高速信号可以直接从TX发送到RX,不会受到测试机电路的干扰,而且测试机可以对RX端口施加合适的直流偏置,从而实现高速信号电平特性的冗余度(眼图高度)测试 这一方法由于完全采用被动器件组合,稳定性高,不容易发生故障.但是,由于是针对高速信号,电路的设计比较复杂,电容和电感的器件选型有一定技术含量以及后续可能需要进行电路的仿真,确保电路的设计正确.一般电容往往建议采用0.01~0.1uF的0402陶瓷电容,而电感则可能需要多级电感串联 限于篇幅,今天我只是在这里针对常用的高速信号测试方法作一些概括性简单介绍,关于这个电路具体的设计,我以后找机会再慢慢聊吧 关牮 微博:封测G哥 微信:jamesg003

|