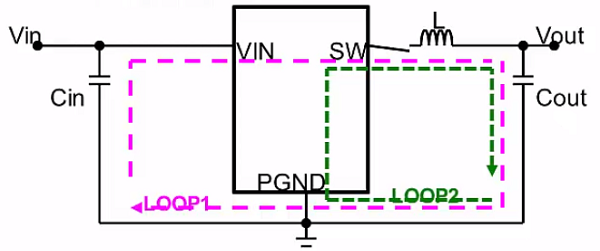

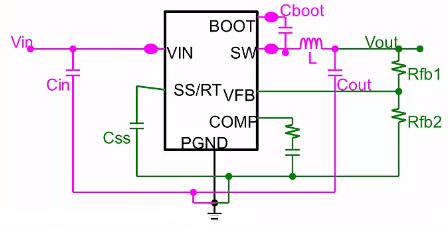

DC-DC的电路比LDO会复杂很多,噪声也更大,布局和layout要求更高,layout的好坏直接影响DC-DC的性能,所以了解DC-DC的layout至关重要。1. Bad layout· EMI,DC-DC的SW管脚上面会有较高的dv/dt, 比较高的dv/dt会引起比较大的EMI干扰;· 地线噪声,地走线不好,会在地线上面会产生比较大的开关噪声,而这些噪声会影响到其它部分的电路; · 布线上产生电压降,走线太长,会使走线上产生压降,而降低整个DC-DC的效率;

· 开关大电流回路尽量短; |

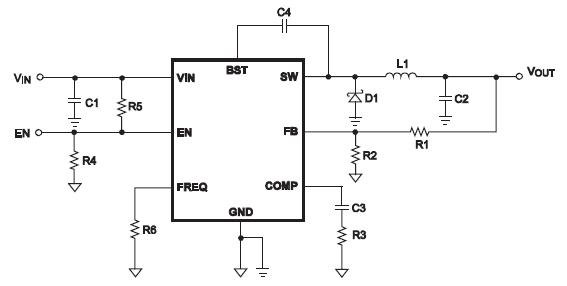

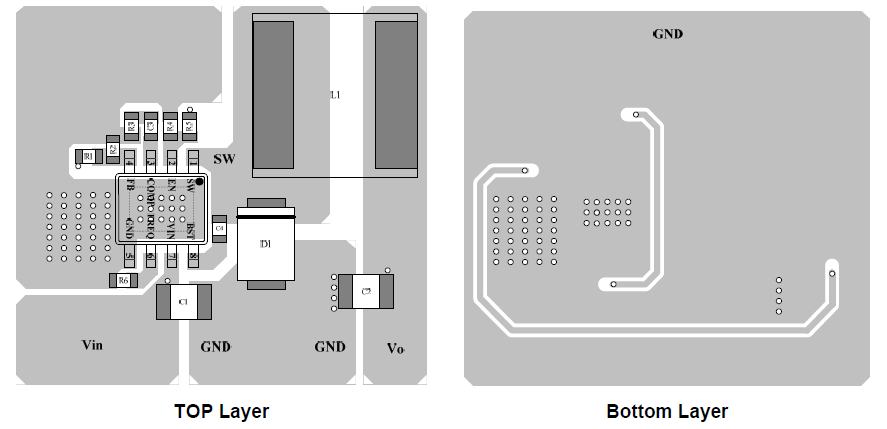

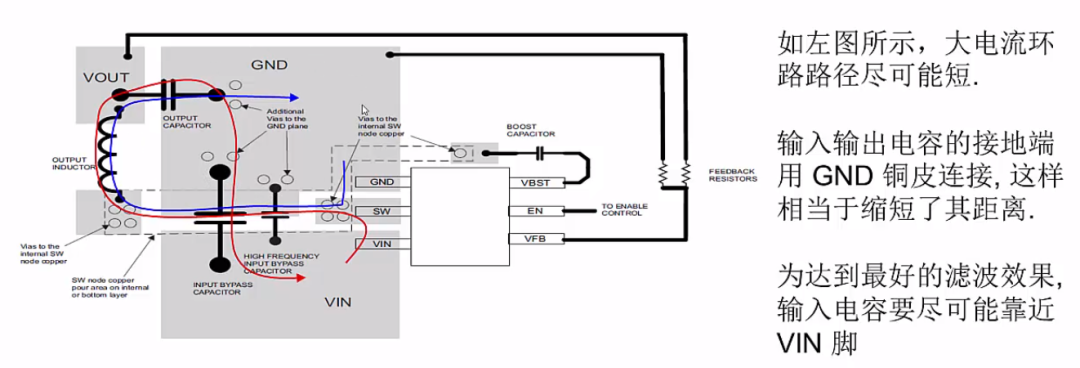

TI某开发板的DC-DC PCB layout

TI某开发板的DC-DC PCB layout