|

在一些PCB的layout中,大家往往会看到在I2C通信的接口处,往往会接入一个4.7K的电阻,有的datasheet上面明确有要求,需要接入,有的则没有要求。

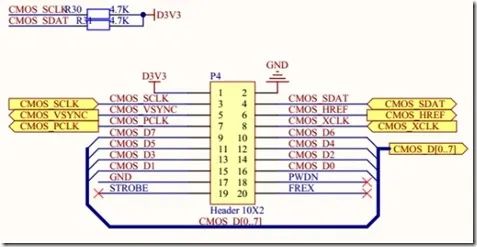

I2C总线接口电路

对于单片机来讲,有些IO内部的上拉电阻可以使能,这样就省去了外部的上拉电阻,这是对于单片机带有标准I2C通信协议接口,若是只带有模拟I2C协议接口,那么就需要考虑接入上拉电阻问题。下图是摄像头进行配置通信时SCL和SDA需要进行上拉电阻的连接。

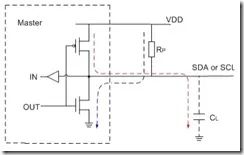

在大多数情况下,由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的,如图1所示。

图1

因为I2C总线在空闲时必须拉高,只有是高的才能拉成低的,所以这是之所以规定空闲时必须为高的一个原因,要是保持“低”的话,那是不可能成为“多主”总线的。

其实I2C总线接口在工作时只会检测高低电平,他不会在乎有无上拉电阻的问题,所以总线必须满足时序要求。

上拉电阻的大小,会牵扯到两个问题,一个是功耗,一个是速度问题,两者是一个矛盾体。如果你想尽量提高速度,那么就牵涉到总线电容的问题,其实很容易理解,上拉电阻与总线的电容形成了RC,高速时将直接影响通讯!因为总线拉高时有个充电时间以及高电平的阀值,如果还没有充电到足以保证从器件可以识别的高电平的阀值时主器件就以为完成了一个总线动作的话,那么通讯肯定是不能进行的!

I2C上拉电阻大小

I2C上拉电阻确定有一个计算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874) *c, ( T=1us 100KHz, T=0.3us 400KHz )

C是Bus capacitance

Rp最大值由总线最大容限(Cbmax)决定,Rp最小值由Vio与上拉驱动电流(最大取3mA)决定;

于是 Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)

Rpmax取值:标准模式,100Kbps总线的负载最大容限<=400pF;快速模式,400Kbps总线的负载最大容限<=200pF,根据具体使用情况、目前的器件制造工艺、PCB的走线距离等因素以及标准的向下兼容性,设计中以快速模式为基础,即总线负载电容<200pF,也就是传输速度可以上到400Kbps是不成问题的。于是Rpmax可以取的范围是1.8K~7K @ Vio=5V对应50pF~200pF。

根据Rpmin与Rpmax的限制范围,一般取5.1K @ Vio=5V , 负载容限的环境要求也容易达到。在2.8V系统中,console设计选3.3K,portable/handset等低供耗的设计选4.7K牺牲速度换取电池使用时间。

总的来说:电源电压限制了上拉电阻的最小值 ;负载电容(总线电容)限制了上拉电阻的最大值

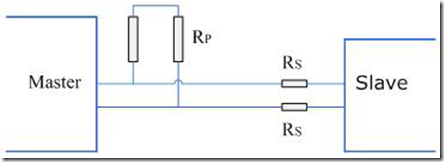

补充:在I2c总线可以串连300欧姆电阻RS可以用于防止SDA和SCL线的高电压毛刺。I2C协议还定义了串联在SDA、SCL线上电阻Rs。该电阻的作用是,有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在100~200ohm左右。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用。

I2C上拉电阻讨论

RP不宜过小,一般不低于1KΩ

一般IO 端口的驱动能力在2mA~4mA量级。如果RP阻值过小,VDD灌入端口的电流将较大,这导致端口输出的低电平值增大(I2C协议规定,端口输出低电平的最高允许值为0.4V);如果灌入端口的电流过大,还可能损坏端口。故通常上拉电阻应选取不低于1KΩ的电阻(当VDD=3V时,灌入电流不超过3mA)。

RP不宜过大,一般不高于10KΩ

由于端口输出高电平是通过RP实现的,线上电平从低到高变化时,电源通过RP对线上负载电容CL充电,这需要一定的时间,即上升时间。端口信号的上升时间可近似用充电时间常数RPCL乘积表示。

信号线负载电容(对地)由多方面组成,包括器件引脚、PCB信号线、连接器等。如果信号线上挂有多个器件,负载电容也会增大。比如总线规定,对于的400kbps速率应用,信号上升时间应小于300ns;假设线上CL为20PF,可计算出对应的RP值为15KΩ。

如果RC充电时间常数过大,将使得信号上升沿变化缓慢,达不到数据传输的要求。

因此一般应用中选取的都是几KΩ量级的上拉电阻,比如都选取4K7的电阻。

小阻值的RP电阻增大了端口 Sink电流,故在可能的情况下,RP取值应稍大一点,以减少耗电。另外,通常情况下,SDA,SCL两条线上的上拉电阻取值是一致的,并上拉到同一电源上。

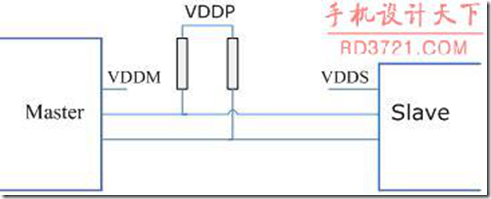

I2C应用中上拉电阻电源问题

在部中分应用中,还存在主从设备以及上拉电阻电源不一致的情况,比如Camera模组。在很多设计方案中,Camera模组不工作时,并不是进入Power Down模式,而是直接关闭模组供电VDDS。此时,处理器与模组相互连接的所有信号线都应该进入高阻态,否则就会有电流漏入模组;而对于此时的I2C控制信号线来说,由于上拉电阻的存在,必须关断上拉电阻电源VDDP。如果上拉电阻使用的是系统电源VDDM(VDDP=VDDM),无法关闭,就会有漏电流进入模组;因此这种情况下,应该使用VDDS作为上拉电阻电源(VDDP=VDDS),这样上拉电阻电源与Slave电源即可同时关闭,切断了漏电路径。

另外需要注意的是,在上述应用实例中选择的IO,应该选取上电默认为输入(或高阻)才行。

|