|

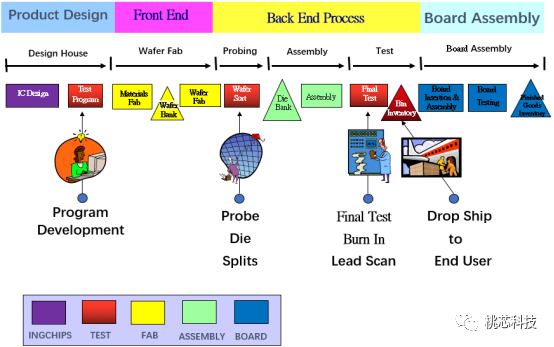

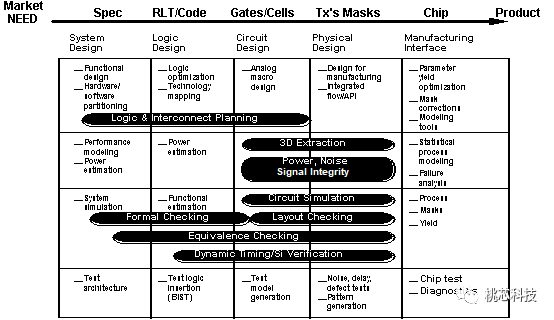

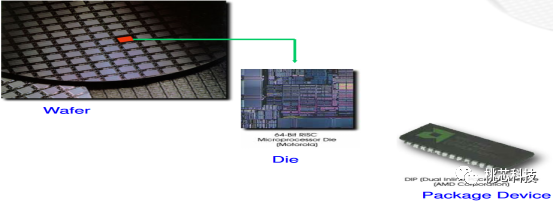

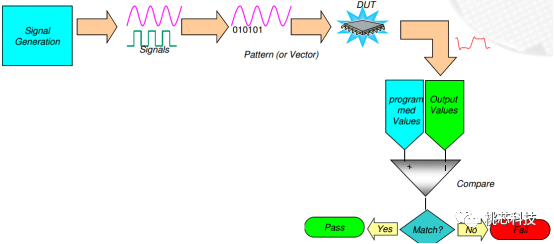

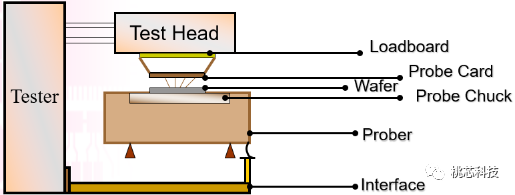

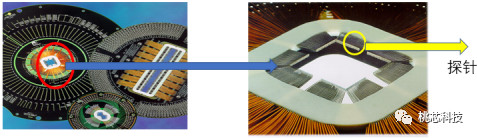

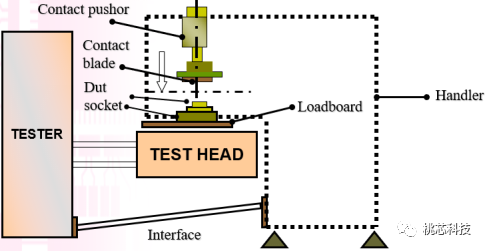

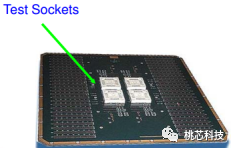

作为一个芯片设计公司(fabless),我们也非常关注集成电路产业链的各个环节,以此更好地给客户提供价值。 这次我们给大家说说芯片测试相关。 1、测试在芯片产业价值链上的位置 如下面这个图表,一颗芯片最终做到终端产品上,一般需要经过芯片设计、晶圆制造、晶圆测试、封装、成品测试、板级封装等这些环节。 在整个价值链中,芯片公司需要主导的环节主要是芯片设计和测试,其余的环节都可以由相应的partner来主导或者完成。  图(1) 2测试如何体现在设计的过程中 下图表示的是设计公司在进行一个新的项目的时候的一般流程,从市场需求出发,到产品tape out进行制造,包含了系统设计、逻辑设计、电路设计、物理设计,到最后开始投入制造。 最下面一栏标注了各个设计环节中对于测试的相关考虑,从测试架构、测试逻辑设计、测试模式产生、到各种噪声/延迟/失效模式综合、进而产生测试pattern,最后在制造完成后进行测试,对测试数据进行分析,从而分析失效模式,验证研发。 所以,测试本身就是设计,这个是需要在最初就设计好了的,对于设计公司来说,测试至关重要,不亚于电路设计本身。  图(2) 图(2)设计公司主要目标是根据市场需求来进行芯片研发,在整个设计过程中,需要一直考虑测试相关的问题,主要有下面几个原因: 1) 随着芯片的复杂度原来越高,芯片内部的模块越来越多,制造工艺也是越来越先进,对应的失效模式越来越多,而如何能完整有效地测试整个芯片,在设计过程中需要被考虑的比重越来越多。 2) 设计、制造、甚至测试本身,都会带来一定的失效,如何保证设计处理的芯片达到设计目标,如何保证制造出来的芯片达到要求的良率,如何确保测试本身的质量和有效,从而提供给客户符合产品规范的、质量合格的产品,这些都要求必须在设计开始的第一时间就要考虑测试方案。 3) 成本的考量。越早发现失效,越能减少无谓的浪费;设计和制造的冗余度越高,越能提供最终产品的良率;同时,如果能得到更多的有意义的测试数据,也能反过来提供给设计和制造端有用的信息,从而使得后者有效地分析失效模式,改善设计和制造良率。 3 测试的各种 对于芯片来说,有两种类型的测试,抽样测试和生产全测。 抽样测试,比如设计过程中的验证测试,芯片可靠性测试,芯片特性测试等等,这些都是抽测,主要目的是为了验证芯片是否符合设计目标,比如验证测试就是从功能方面来验证是否符合设计目标,可靠性测试是确认最终芯片的寿命以及是否对环境有一定的鲁棒性,而特性测试测试验证设计的冗余度。 这里我们主要想跟大家分享一下生产全测的测试,这种是需要100%全测的,这种测试就是把缺陷挑出来,分离坏品和好品的过程。这种测试在芯片的价值链中按照不同阶段又分成晶圆测试和最终测试(FT,也叫封装测试或者成品测试),就是上面图(1)中的红色部分。 测试相关的各种名词: ATE-----------Automatic Test Equipment,自动化测试设备,是一个高性能计算机控制的设备的集合,可以实现自动化的测试。 Tester---------测试机,是由电子系统组成,这些系统产生信号,建立适当的测试模式,正确地按顺序设置,然后使用它们来驱动芯片本身,并抓取芯片的输出反馈,或者进行记录,或者和测试机中预期的反馈进行比较,从而判断好品和坏品。 Test Program---测试程序,测试机通过执行一组称为测试程序的指令来控制测试硬件 DUT-----------Device Under Test,等待测试的器件,我们统称已经放在测试系统中,等待测试的器件为DUT。 晶圆、单颗die和封装的芯片----如下面图(3)所示  图(3) 图(3)Wafer就是晶圆,这个由Fab进行生产,上面规则地放着芯片(die),根据die的具体面积,一张晶圆上可以放数百数千甚至数万颗芯片(die)。 Package Device就是封装好的芯片,根据最终应用的需求,有很多种形式,这个部分由芯片产业价值链中的封装工厂进行完成。 测试系统的基本工作机制:  图(4) 图(4)对测试机进行编写程序,从而使得测试机产生任何类型的信号,多个信号一起组成测试模式或测试向量,在时间轴的某一点上向DUT施加一个测试向量,将DUT产生的输出反馈输入测试机的仪器中测量其参数,把测量结果与存储在测试机中的“编程值”进行比较,如果测量结果在可接受公差范围内匹配测试机中的“编程值”,那么这颗DUT就会被认为是好品,反之则是坏品,按照其失效的种类进行记录。 晶圆测试(wafer test,或者CP-chip probering): 就是在图(3)中的晶圆上直接进行测试,下面图中就是一个完整的晶圆测试自动化系统。 Prober--- 与Tester分离的一种机械设备,主要的作用是承载wafer,并且让wafer内的一颗die的每个bond pads都能连接到probe card的探针上,并且在测试后,移开之前的接触,同时移动wafer,换另外的die再一次连接到probe card的探针上,并记录每颗die的测试结果。  图(4) 图(4)Probe Card---乃是Tester与wafer上的DUT之间其中一个连接介面,目的在连接Tester Channel 与待测DUT。大部分为钨铜或铍铜,也有钯等其他材质;材质的选择需要高强度、导电性及不易氧化等特性,样子如下面图(5)所示。  图(5) 图(5)当 probe card 的探针正确接触wafer内一顆 die的每个bond pads后, 送出start信号通过Interface给tester开始测试, tester完成测试送回分类讯号 ( End of test) 给Prober, 量产時必須 tester 与 prober 做连接(docking) 才能测试。 最终测试(FT,或者封装测试): 就是在图(3)中的Package Device上进行测试.下图就是一个完整的FT的测试系统。对比wafer test,其中硬件部分,prober换成了handler,其作用是一样的,handler的主要作用是机械手臂,抓取DUT,放在测试区域,由tester对其进行测试,然后handler再根据tester的测试结果,抓取DUT放到相应的区域,比如好品区,比如坏品1类区,坏品2类区等。  图(6) 图(6) 而probe card则换成了load board,其作用是类似的,但是需要注意的是load board上需要加上一个器件—Socket,这个是放置package device用的,每个不同的package种类都需要不同的socket,如下面图(7)所示,load board上的四个白色的器件就是socket。  图(7) 图(7)Handler 必须与 tester 相结合(此动作叫 mount 机)及接上interface才能测试, 动作为handler的手臂将DUT放入socket,然后 contact pusher下压, 使 DUT的脚正确与 socket 接触后, 送出start 讯号, 透过 interface 给 tester, 测试完后, tester 送回 binning 及EOT 讯号; handler做分类动作。 |