|

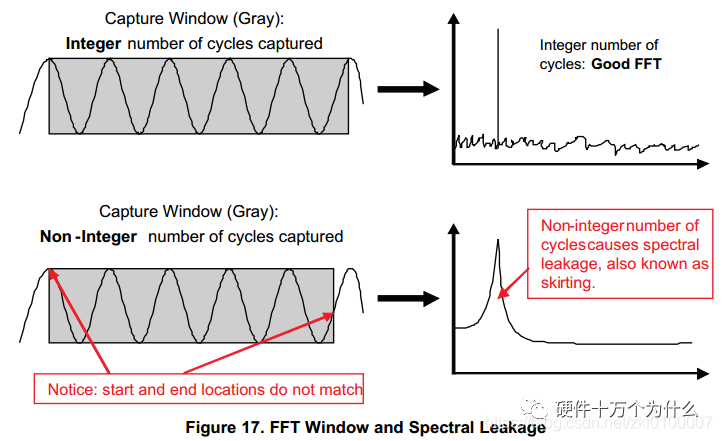

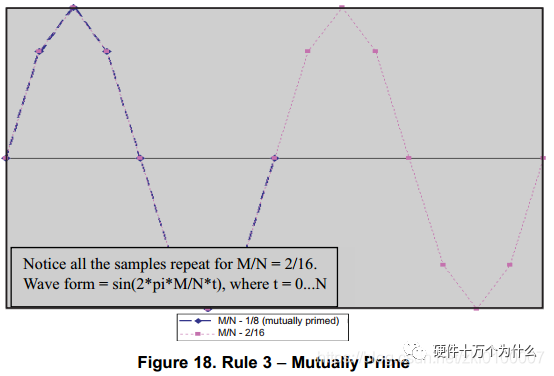

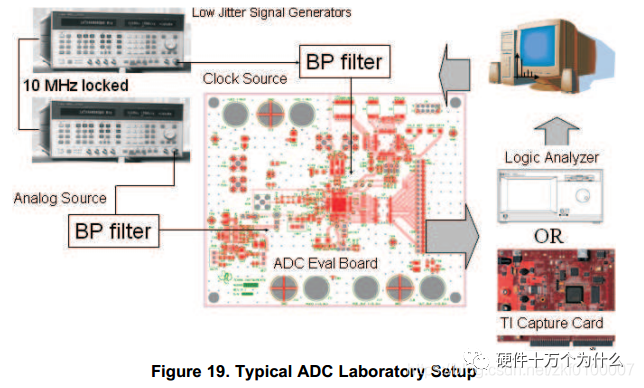

那么问题来了,如果关注时钟上升斜坡,那为什么不直接给ADC提供方波时钟信号?答案是:方波时钟确实是一个可行的ADC时钟选择。但是,设计者必须在正弦和方波之间做出一系列的折衷。 其一是低抖动方波时钟与时钟频率范围间的折衷。对于大多数应用,通过窄带SAW或晶体滤波器以改进ADC时钟的close-in相位噪声(抖动)。滤波后,时钟变成低抖动正弦时钟,可以直接提供给ADC。这种方法的局限在于时钟频率范围受限于滤波器带宽。一些公司有时钟抖动清除及时钟分配芯片,这些芯片具有较好的相噪性能、方波输出和较宽的频率范围,其相噪特性足以满足系统需求,而不需要额外滤波器。 其二是方波时钟与正弦时钟在信号完整性方面的折衷。与正弦信号相比,方波信号具有丰富的谐波,具有高频分量。由于信号反射及对其它信号的干扰,高频分量会对电路设计带来较大困难。不管采用哪种时钟信号,必须对电路设计着重考虑,以满足ADC的抖动需求。 4.4实验评估 ADC的实验评估主要包括软件和硬件两个方面。 ADC实验评估的软件手段主要是FFT。由于其高速及准确性,FFT是时域到频域变换的卓越评估工具。 要实现FFT,必须理解一致性、加窗和频谱泄漏等概念。 下图显示了加窗和频谱泄漏。窗口选择不当会导致频谱泄漏。  某些设计者需要非整数个周期。在这些特殊情况下,由于频谱泄漏,不能使用FFT,可以使用布莱克曼窗或者傅利叶分析。这种方法允许采集非整数个周期信号,但是需要更多计算时间并且会对噪底计算和频率响应引入少量误差。 FFT一致性定义如下:  上式中的参数需遵循以下规则: 规则1:M是奇整数。M为整数是为了避免频谱泄漏,奇数的要求是由于规则3。 规则2:N是2的幂。FFT的点数必须是2的幂,通常是4096,8192,16384,32768或65536。选择N时,需要在计算时间、测量重复性等因素之间做权衡。 规则3:M和N是互质数。M和N互质是为了保证采集到非重复数的样本。由于FFT的特性,重复样本除了带来额外的计算量外,并不能提供更多的有用信息。由于N是2的幂,若限定M是奇整数,则可保证M和N互质。  规则4:FIN与FS的分辨率须大于输入源的最小分辨率要求。例如,模拟输入和时钟源的最小分辨率为10Hz,则它们不能被设置为小于10Hz的分辨率。在做FFT时,如果频率分辨率小于输入源的分辨率,会采集到非整数个周期,进而引起频谱泄漏。 设计实例: 需求如下: Fin=70MHz Fs=125Msps 分辨率为1Hz 求解M,N,Fin,Fs。 (1)取N=8192,M=NFin/Fs=4587.52,取M=4587. (2)根据N重新计算Fs(保证分辨率为1Hz) X=Fs/N=125M/8192=15258.789 X取整为Xnew=15258. 新的Fs=XnewN=152588192=124.993536Msps (3)计算新的Fin Fin=FsM/N=124.993536Msps*4587/8192=69.9988446MHz ADC实验评估的硬件包括: (1)时钟源:为达到所需的抖动要求,需通过BPF滤除close-in和宽带噪声 (2)模拟输入源:为达到所需的噪声和谐波要求,需通过BPF滤除噪声和谐波 (3)数据采集仪:保证采集仪具有足够的速度和存储容量用于FFT处理 典型的ADC实验设置如下图所示:

|