|

我们都知道,SCAN的fail,对应于制造过程中出现的defect。所以一些EDA厂商,会有scan diagnosis的工具。这些工具结合芯片的逻辑设计和物理结构,并给它足够的scan fail cycle的信息,能够定位出具体是哪个位置出现了defect。这样的诊断,有助于fab厂快速提高自己的工艺水平,尽快实现yield ramp。 这样的diagnosis通常是在CP阶段做。因为结合scan fail的cycle,芯片的xy坐标的分布,能够更全面更准确地反映出工艺上的问题。在FT上也可以做,但这样反映出来的问题就不太全面,因为缺少了XY坐标的信息,就缺乏了趋势分析的数据。然而在工艺水平比较老的时候,有些产品只做FT不做CP,这种情况下,FT阶段的diagnosis信息仍然是有价值的。 几年前我恰好有机会做过一次FT上的SCAN diagnosis, 最终还真定位到了问题。然而diagnosis出来的问题,也有可能和实际PFA出来的问题,并不完全一致。一方面是工具本身只能分析metal层以上的问题,器件层的问题是没办法分析的,另一方面,因为ATPG算法模型的问题,它会有一些assumption,比如认为stuck fault都是SSF(signle stuck at fault),有这类assumption的存在,diagnosis就没办法做到完全准确,所以只能给出一个defect的概率。所以诊断结果和PFA结果不能完全对应上,也是有可能的。 diagnosis工具需要设计文件,包括网表和互联设计。通常是LEF、DEF和FLAT文件。LEF文件是Library Exchange Format 的缩写,里面规定了physical design的规范,比如design rule和器件cell的抽象信息(不包括cell的物理信息)。DEF文件是Design Exchange Format的缩写,里面定义了芯片layout的连接关系。跟LEF文件一起,可以表示出整个芯片metal层以上的互联设计。FLAT文件,是SOC做完综合后,生成了ATPG文件后,生成的一种展开的网表文件。在diagnosis的时候,要注意FLAT文件里面的ATPG设置必须跟生成pattern的ATPG设置一致。不一致的话是没办法做diagnosis的。

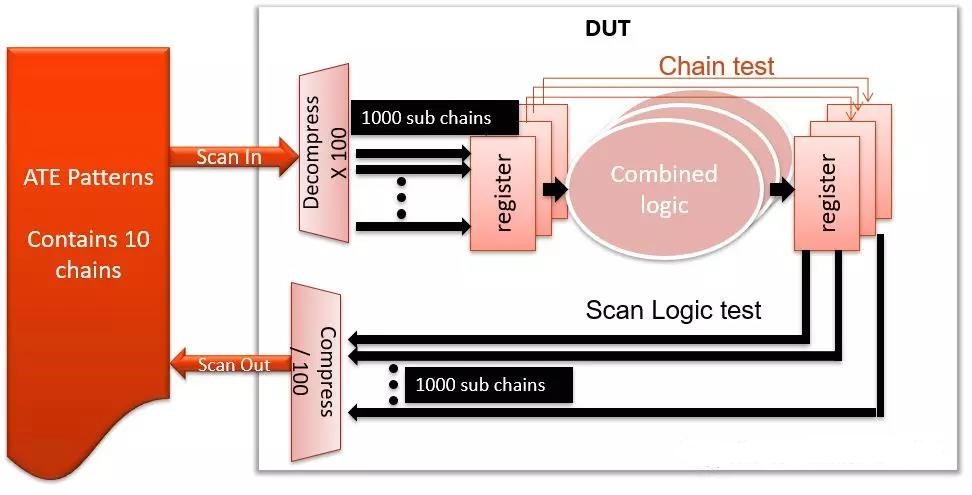

diagnosis需要的ATE log,需要上千个pattern的fail log,且fail cycle要大于一定的数量。这里所谓的上千个pattern,是指pattern在芯片内部经过decompression之后的sub chain。因为diagnosis工具是根据fail的cycle计算defect的概率,当fail cycle太少的时候,工具也没办法判断到底defect在哪。 根据芯片规模大小的不同,diagnosis的过程可能需要几十小时。

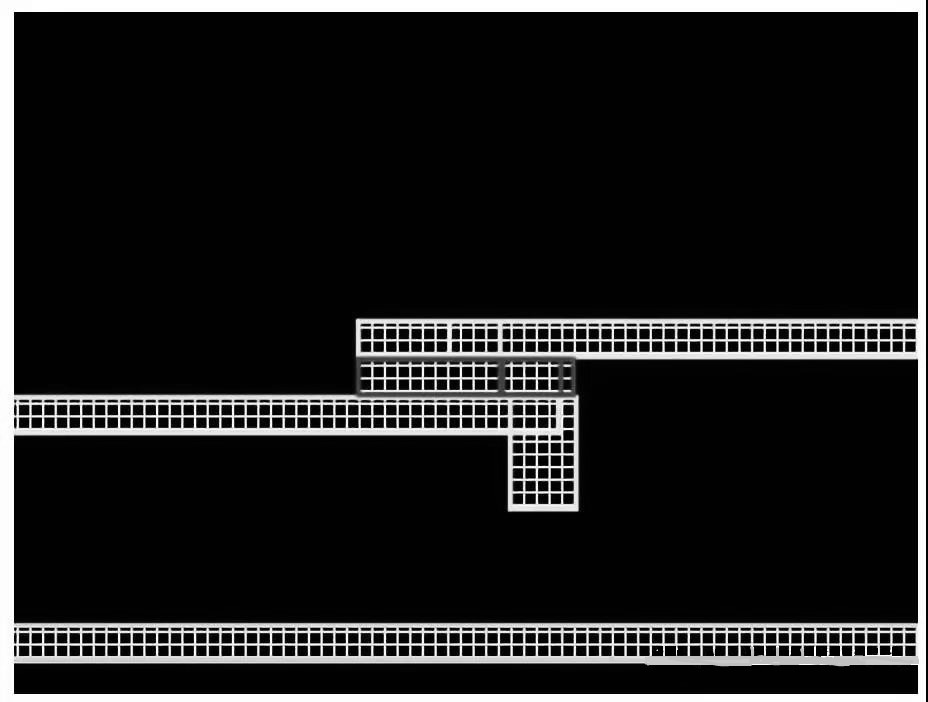

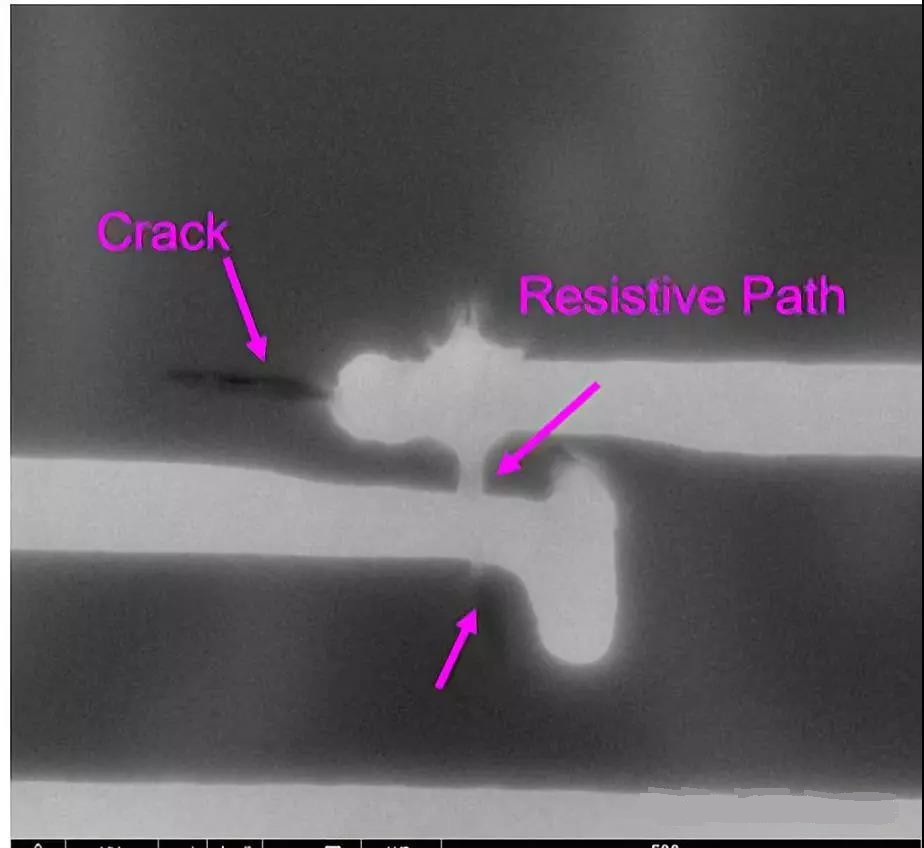

diagnosis软件会圈出疑似发生defect的位置,并给出概率:100%,还是95%,还是80%: 如果实际做physical FA的话,在显微电镜下看到的defect是这样的:

可以看到本来应该连在一起的metal,现在只有一条细线连着,形成了resistive的path。标注crack的地方,是dielectric material出现了裂缝。因为芯片内部不是真空的,这类crack容易受到湿度变化和使用状态的影响,导致芯片fail。 如果是CP测试,有wafer map的信息,diagnosis软件还会根据fail的类型,分布,推断出大概是fab的那类工艺出了问题。 上面提到的SCAN的diagnosis,针对于stuck at fault。对于transition fault和MBIST,需要其它工具别的算法来实现。所以分析数据时,针对不同类型的yield loss,要做不同的分析。 SCAN失效分析,需要Physical Design,DFT,ATE,FAB,PFA多方协作,不是一个容易的工程。正因为不容易,才具有很大的价值。 |