|

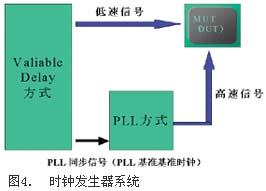

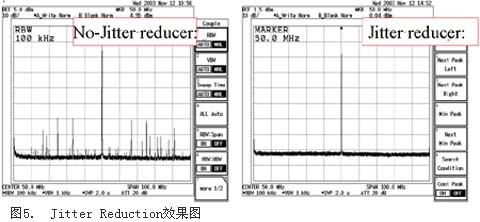

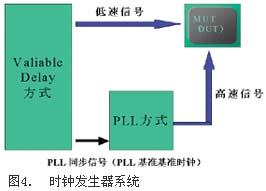

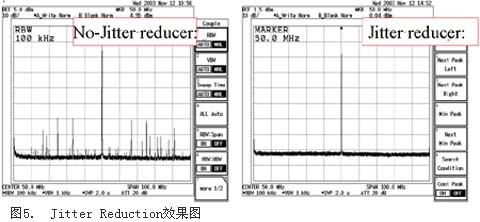

因此我们采用的是如图4所示的低速时钟发生采用Variable Delay方式,高速部采用与低速部保持同步的PLL方式。另外,Jitter Reduce电路的嵌入也可以使得高速部的向量(Pattern)发生尽可能的不受到低速部的Jitter误差的影响。

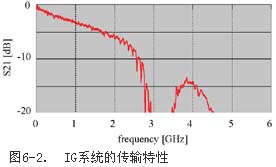

从PE到被测芯片(DUT)的高速信号传送

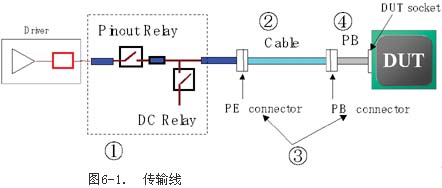

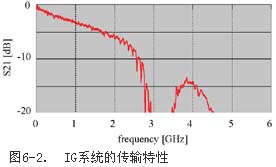

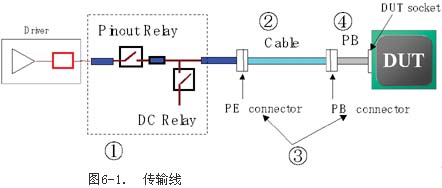

在实际测试中,从ATE的Driver端到被测芯片(DUT)的信号传送过程,会遇到如图6-1所示的Pin-Relay、传输线路(同轴线)、接线端子、印刷线路等各影响高频信号衰减的问题。图6-2是一般的1GHz信号用线路的传输特性,当用它来传输更高频率的信号时,我们可以看到在2.5GHz开始就会造成较大的衰减损失。这个衰减如果是超过10dB以上的话,是很难进行正确补偿的。因此为了减小在高频带的损失,我们对上述图6-1线路进行了以下4个项目的改进。

① Pin Relay & DC Relay

② 同轴线

③接线端子(Connecter)

④ 印刷线路

传输线路的改善

① Pinout Relay & DC Relay

安装在测试系统内部的信号输出/输入控制部的Relay本身的性能对最终的波形品质有较大的影响。现在普通使用的Photo-Mos Relay的最大信号带宽是1GHz左右,不能达到传送5GHz这样的高频信号的要求。因此,我们采用的是爱德万测试研制开发的,具有非常好带宽的小型MEMS Relay。

② 同轴线

为了传输这样的高频信号,和普通的同轴线相比,除了需要高精度的阻抗(Zo)特性以外,还应当具有低损耗、Zo值不受电缆弯曲变形,温度等外部影响的特性。为了实现Zo的高精度,(1)同轴线做成尽可能的保持圆心性。(2)最大限地提高同轴线各部分所用材料的尺寸精度、组装精度,保证实际Zo与计算值在最大±0.5Ω的误差。另外为了提高耐弯曲变形强度,采用了编组绞织屏蔽线及FEP外皮,以使得电线弯曲时的受力均匀分布,避免线材的直角弯曲,保证了即使受到外力情况下的Zo无变化。经过φ30mm的S字扭曲试验验证,普通的同轴线的阻抗变化是+3.3Ω,而上述特制同轴线的变化为0.1Ω以下。另外,高频特性也从-2.5dB@3GHz提高到了-1.8dB@3GHz。同时,FEP外皮在耐热性方面也有较大的优势,使得这种同轴线的最高使用温度达到了150℃。

③ 接线端子

为了保证高性能的高频信号传输,除了保证同轴电缆的传输特性,与之相连接用的接线端子的高频特性也是非常重要的。

④ 印刷线路

当被输送信号达到数GHz程度时,导线的集肤效应会造成较大的导线损失及诱电损失(tanδ)。当信号的传输线路较短的时候,信号的损失几乎体现不出来,但是在多管脚VLSI芯片的测试中,其信号传输线最少也有数十管脚到一百多管脚,Load board上的高速信号传送长度约为15cm到25cm。由于在这种情况下前述线导体损失及诱电损失(tanδ)的影响已经不能忽略,因此我们采用了低诱电率、tanδ较小的材质来制作Load Board的印刷线路,达到抑制信号传送损失的目的。

通过以上①到④对全体传输线路的改善,我们得到了可以达到4GHz的传输特性。而且在2.5GHz附近的信号衰减也仅为-4dB左右,因此可以通过本文后述补偿方法以使得系统达到5GHz带宽的信号传送。

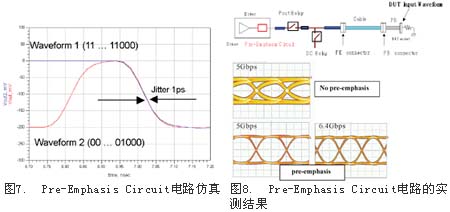

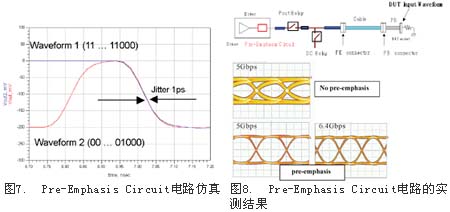

传输损失的补偿

信号的线路衰减(insertion losses)越大。因此当传输脉冲信号时,表现为信号上升沿的变形及整体波形的非整合性。前沿的变形是由于我们知道脉冲信号中包含了全部的奇数高次谐波成分,在通过传输线路时由于高次谐波成分的衰减而造成的。由于一部分的非整合性的存在,在实际应用中会产生图形向量(Pattern)造成的时序错误(Timing error)。因此需要通过对其进行一定的补偿。图7所示为在线路中插入与其相反传输特性的pre-emphasis电路时的Jitter仿真结果,图8是实测波形。由于实测波形中含有一定的随机Jitter(Random Jitter)成分,虽然Jitter值有一定差异,但是我们同样可以确认到与仿真结果一样的Jitter改善效果。

芯片测试

利用这个5G高速选件(Option),我们对Redwood(5Gbps)、XDR内存、PCI-Express高速接口等进行了测试评价。

Redwood(5Gbps)

将5G选件自身的输出通道(Dr)与输入通道(Cp)对接起来对其进行性能评价,这个高速选件的信号输入比较部(Cp)本身虽然为了对应高速接口芯片测试,其结构为差分输入比较结构(differential),但是其也具有单端输入比较(Single-End)功能。虽然在实际的高速芯片测试中并不需要这种单端输入,但是在许多评价解析情况下存在对这种功能的要求,因此5G高速选件中加入了分别的单端输入正负单端(Pos/Neg)比较功能。

XDR

XDR是在目前的高速接口(IF)中唯一采用IO共通使用的接口标准。测试系统的输入输出通道(Dr/Cp)与芯片之间是一种被称为Fly-by的连接方式。控制采用的是本文前面所述的将差分的正负(Pos/Neg)固定电压值输出机能。

PCI-Express

PCI-Express的基本规格中对差分电压的中间点电压值有其特殊的要求。对应其规格要求,在对PCI-Express进行测试时,2个驱动通道(Dr)并列使用作为芯片的1个输入。

总结

针对高速差分信号的测试,爱德万测试基于高速SoC测试系统T6683开发了最大对应5Gbps的高速测试选件。通过这个系统,

1. 技术验证了现阶段各种具有代表性的高速接口芯片的测试可行性。

2. 开发成功了数Gbps以上测试所需的未来测试系统的基础要素技术及其实现方案。

|